- 1Solana初识\了解Solana:领导者轮换机制_solana原理

- 2解决pytorch报错:RuntimeError: DataLoader worker (pid(s) ***, ***, ***, ***) exited unexpectedly_runtimeerror: dataloader worker (pid(s) 18832, 852

- 3【 C++ 】哈希表底层结构剖析_c++ 实现哈希表开散度

- 4软考高项:项目沟通及干系人管理模拟试题_关于项目干系人的选择题怎么写

- 5MySQL数据库基础

- 6com.alibaba.otter.canal.client.impl.ServerNotFoundException: no alive canal server for ucs_sf_to_qg_

- 7软件测试笔试题1(附答案)_软件测试笔试题博客

- 8百川智能发布超千亿大模型Baichuan 3,中文评测超越GPT-4

- 9一个小技巧 N-garm_ngarm算法

- 10十月丰收季,程序员小跃都收获了什么?_10月程序员

【无标题】Quartus II 11.0 联合Modelsim SE-64 10.6d进行仿真实验简要说明

赞

踩

(一)工程的建立

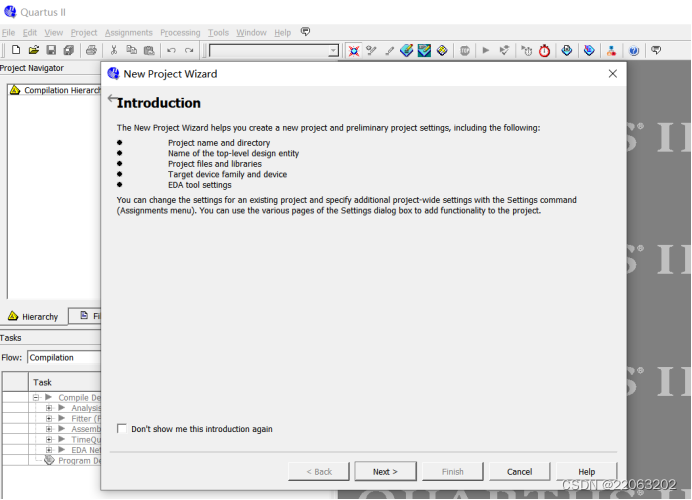

1、双击桌面Quartus II 11.0 (64-Bit)图标,建立FPGA工程。

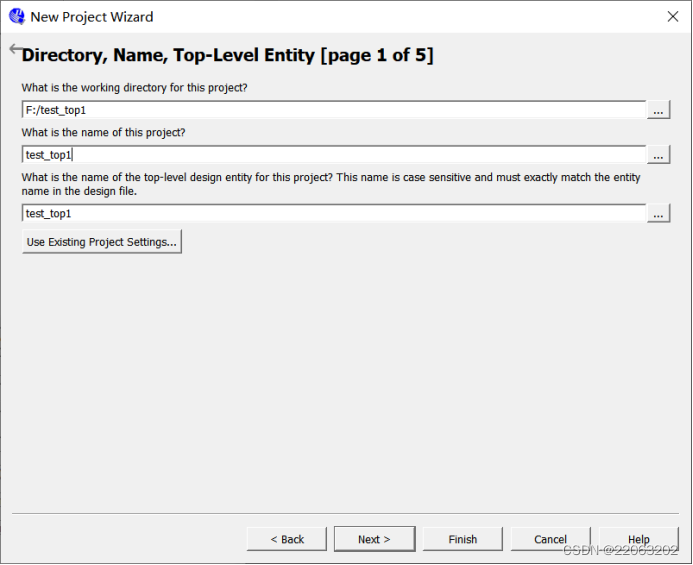

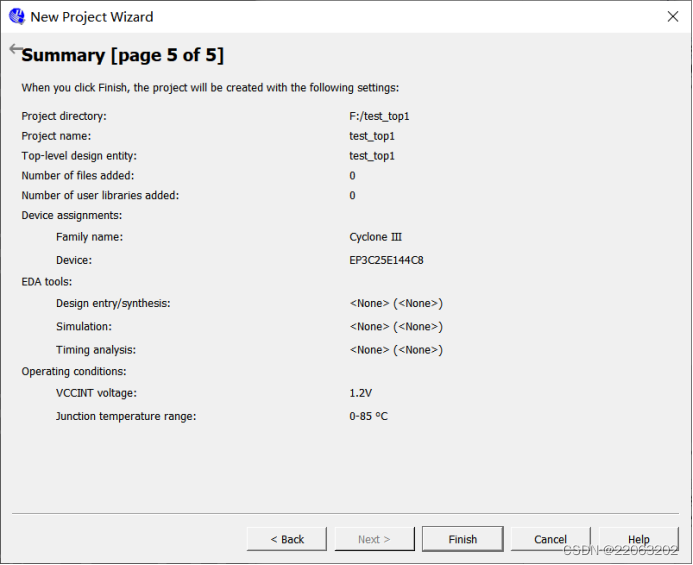

2、点击上图NEXT,在F盘底目录下创建名为test_top1文件夹,并且第一行工程目录名为test_top1,第二行工程名称取为test_top1。

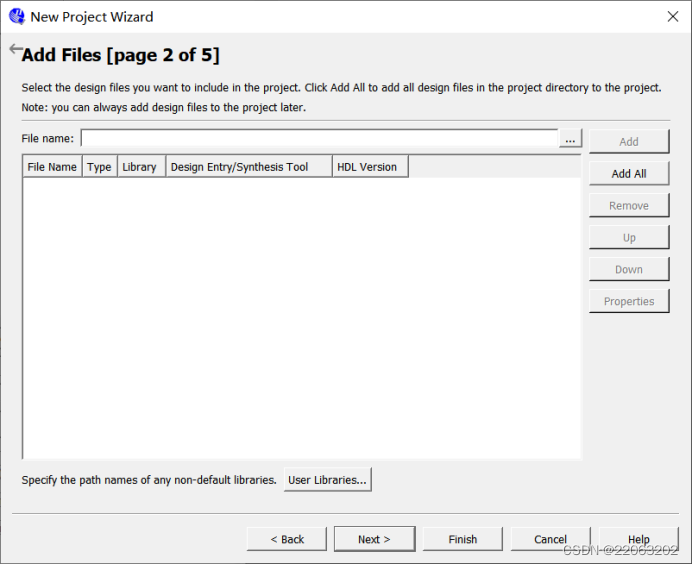

3、点击上图NEXT

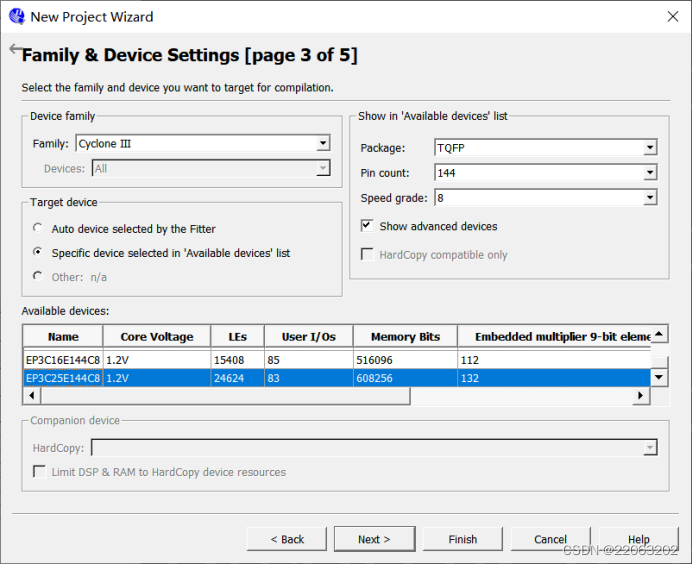

4、点击上图NEXT,在出现如下图时选择相应器件

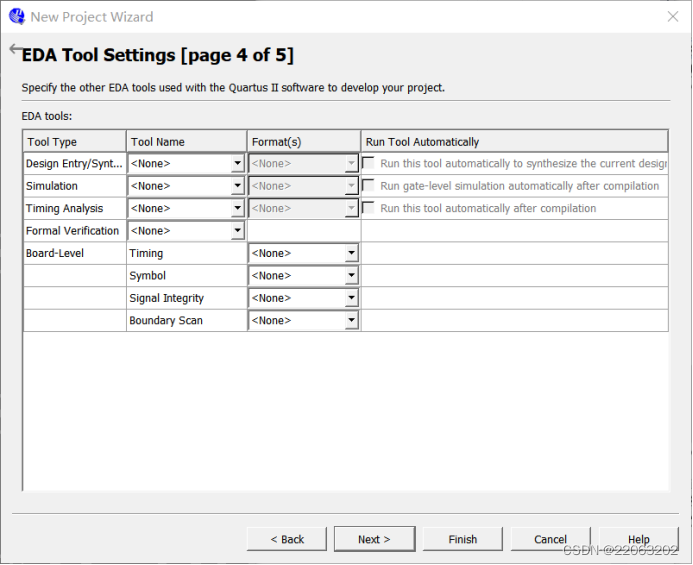

5、如上图点击NEXT

6、如上图,点击NEXT

7、如上图点击Finish,至此,工程就建立好了。

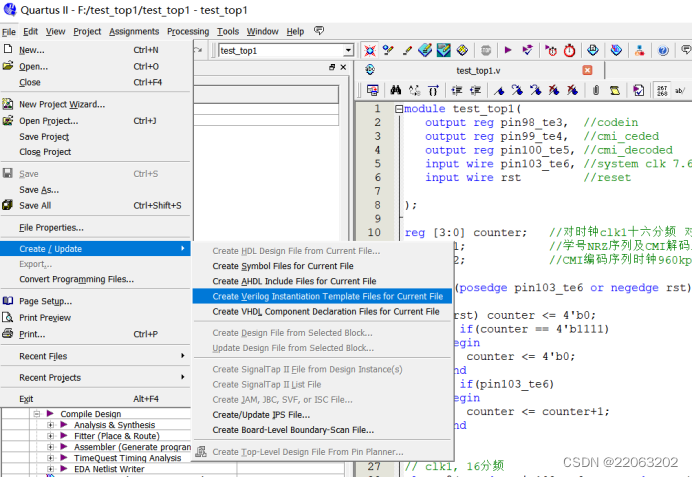

(二)顶层文件设计

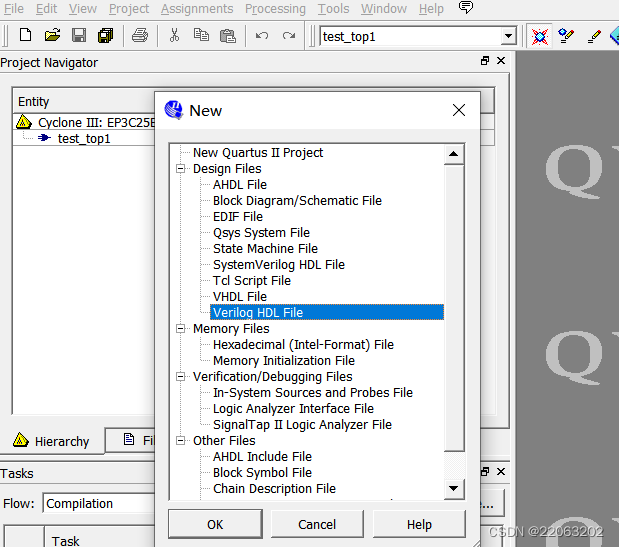

- 新建一个文件

点击OK即得到如下界面

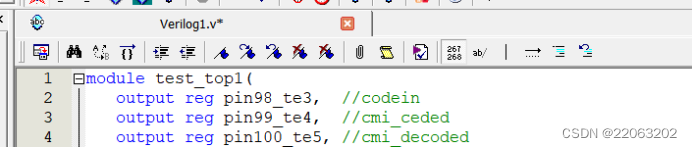

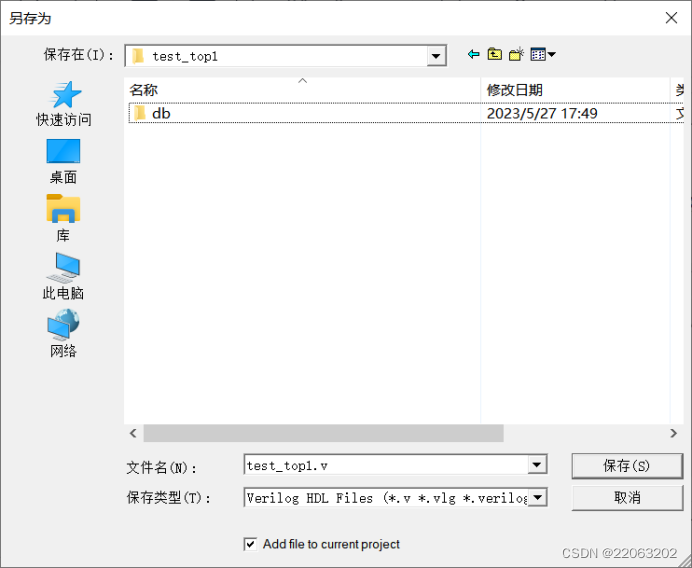

2、编写顶层.v代码,可事先写好后粘贴,保存文件。保存文件的路径为该工程所在的路径,文件名与.v文件中的module后面的“test_top1”一种,最好和工程名也一致。

3、编译代码。打开文件并进行语法编译,如果有错,则需要根据提示进行修改。

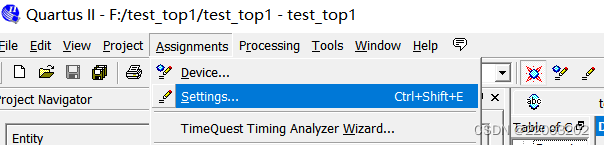

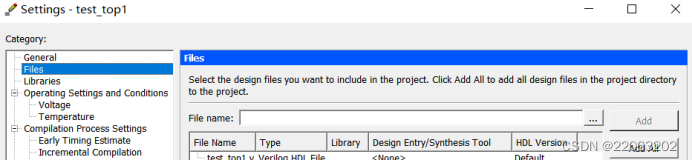

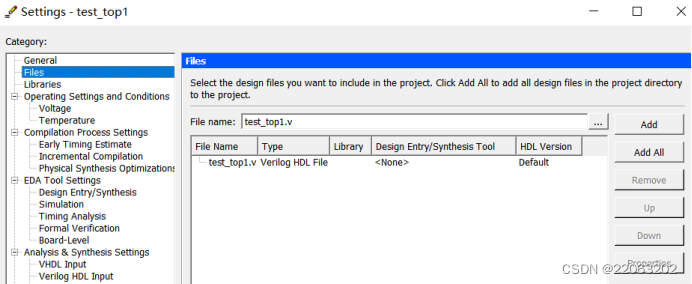

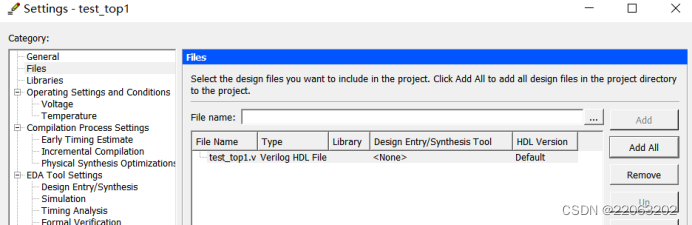

4、将文件加入到本工程

点击File name后面的三个点“...”

点击“test_top1.v”得如下结果

点击刚才File name后面的“Add”后点击“OK”。

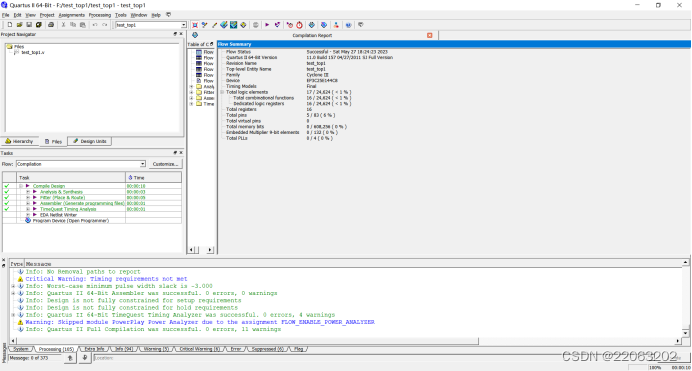

5、编译工程,如果有错误,根据提示进行修改直至编译结果无ERROR反馈信息。

(三)管脚定义

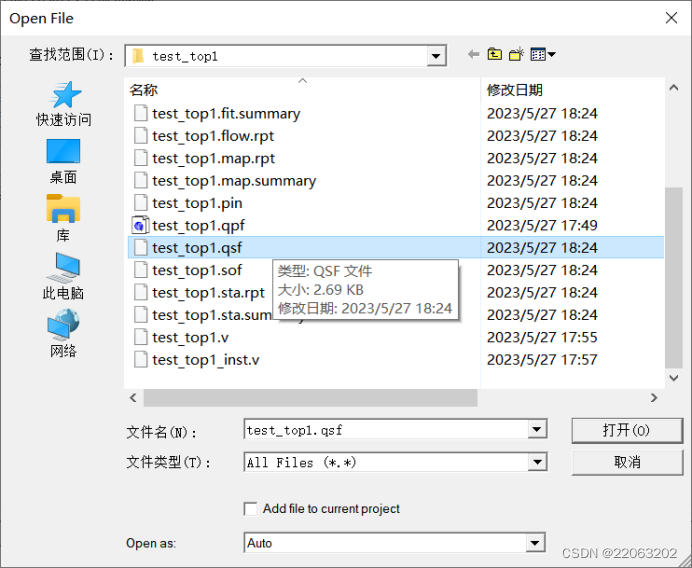

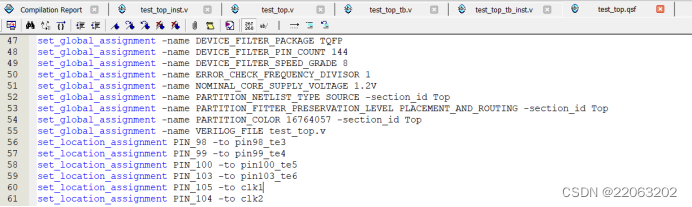

打开并修改编译后生成的“test_top.qsf”文件

在该文件最后增加信号与管脚的对应关系(需编辑和粘贴下面文本):

set_location_assignment PIN_98 -to pin98_te3

set_location_assignment PIN_99 -to pin99_te4

set_location_assignment PIN_100 -to pin100_te5

set_location_assignment PIN_103 -to sys_clk

set_location_assignment PIN_105 -to clk1

set_location_assignment PIN_104 -to clk2

表示输入输出信号与FPGA 的具体管脚相对应。

其中pin98_te3、pin99_te4、pin100_te5、 sys_clk,clk1,clk2这是信号

的名称,要与“test_top1.v”文件中定义的输入、输出信号的名称一致。

修改完成后,保存*test_top1.qsf文件

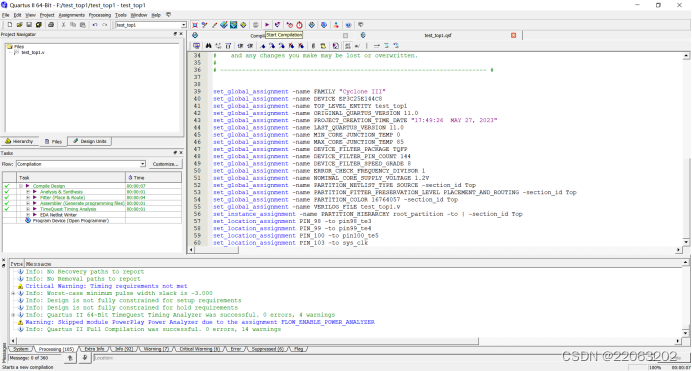

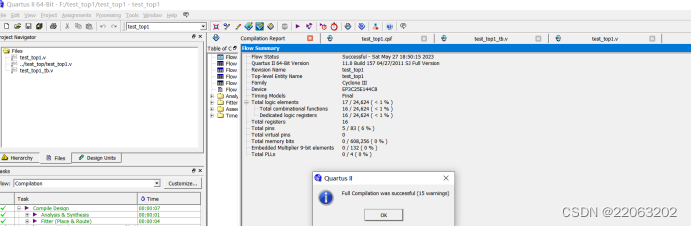

(四)再次编译工程,修改相应的错误

(五)modelsim仿真

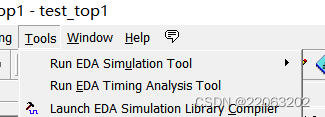

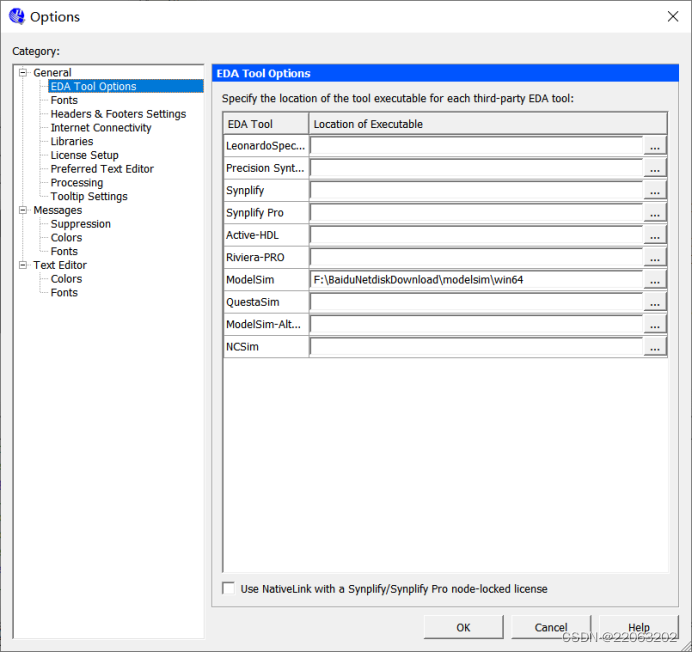

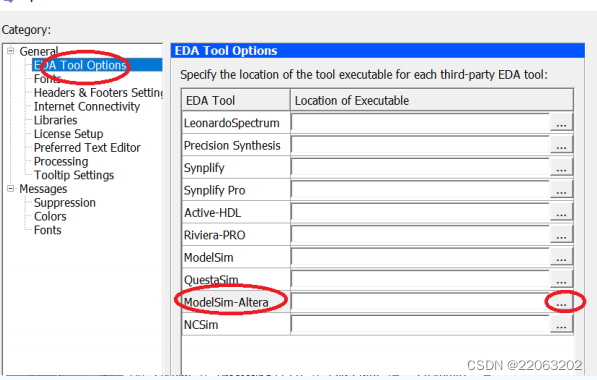

- 关联modelsim

这里根据自己电脑之前已经安装的modelsim 的版本而定,如果安装的是“ModelSim-Altera”则如下操作,如果安装的像我的是modelsim则如上一张图添加。

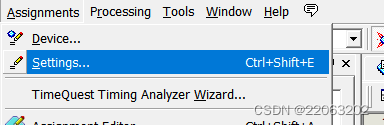

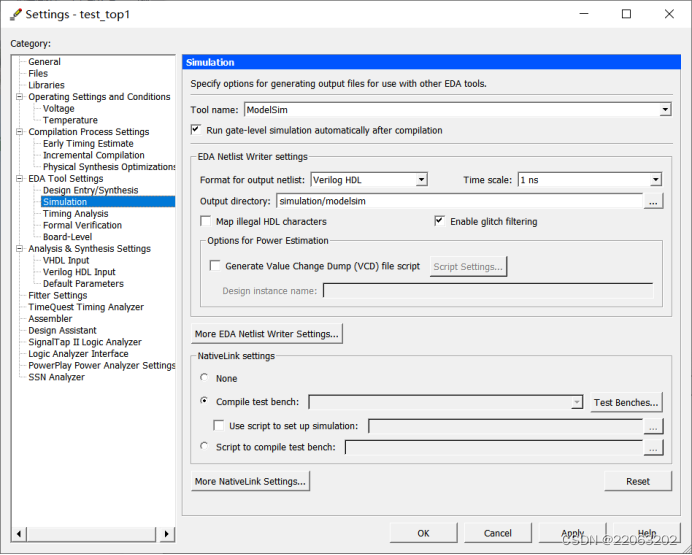

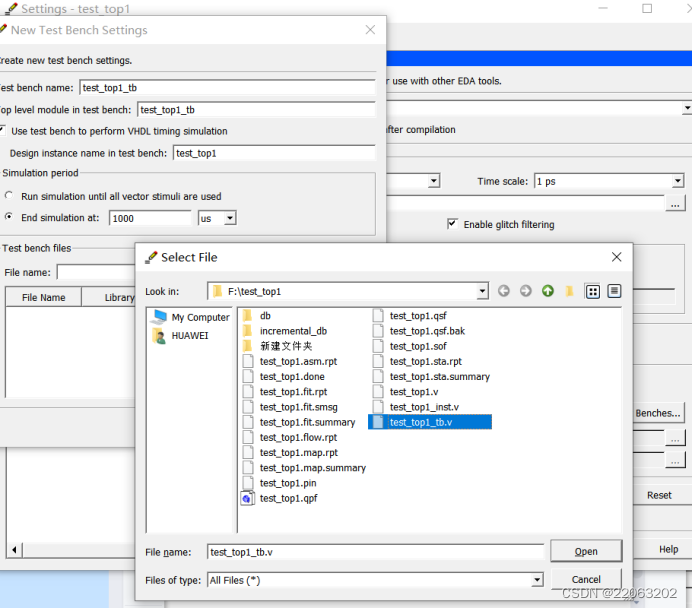

2.配置Modelsim

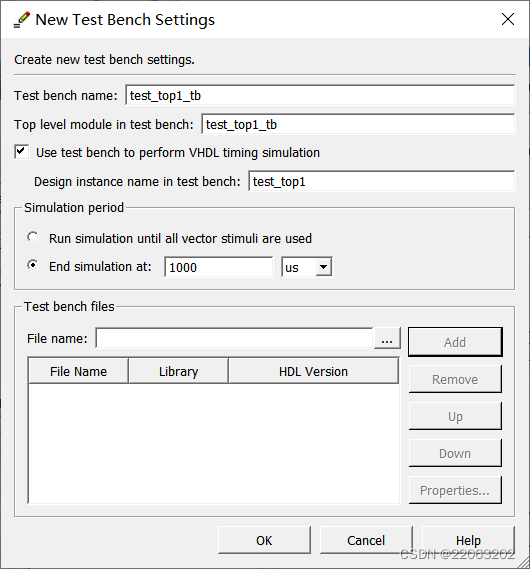

在上图中,开仿真的相应配置,自己的仿真软件为modelsim则在Tool name选择ModelSim ,如果是ModelSim-Altera则选择ModelSim-Altera,接下来关联test bench files,分别填入test_top1_tb, test_top1_tb和test_top1。其中“test_top1”是要仿真的模块名称,也是工程顶层文件名。“1000”us是需要的总仿真时间长度。

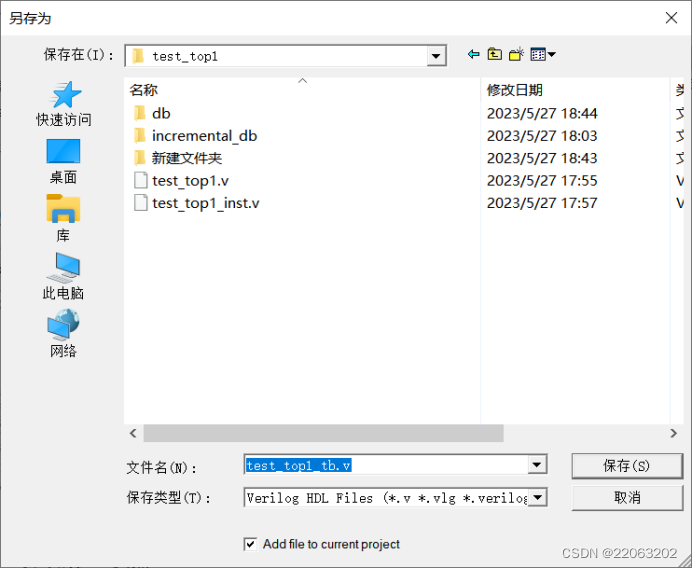

在test bench files中,选择加入事先建立好的test_top1_tb.v仿真文件

注意这里前新建了一个名称为“test_top1_tb”的文件。

在新加的名为“test_top1_tb”的文件后,编译整个工程

点“Add”,OK,OK,再点“Apply”后,最后点“OK”。

3、编译测试文件

打开并编译当前的test_top_tb.v文件,如果有错语法就需要根据提示修改。

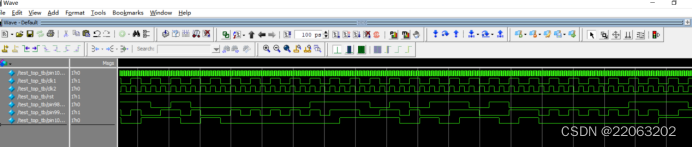

4、编译整个工程,如果全程无误。就可以显示各信号仿真结果波形了。

注:以上仿真步骤为光通信基础课程的实验课仅是个人记录,难免有错误,如果能对读者有所帮助那也再好不过。