- 1计算机二级考试c语言 上机,计算机等级考试二级C语言上机题[2]

- 2不知道软考考哪些内容吗?那来看看或许对你有帮助——软件设计师_软件测试软考应该考哪一门科目?

- 3机器学习实战18-机器学习中XGBClassifier分类器模型的应用实战,以及XGBClassifier分类器的调优策略_xgbclassifier调优

- 4python 求线性回归_stats.linregress(x, y)

- 5auditd和kswapd0导致kylin环境内存CPU占用过高_kylin audit 内存

- 6Oracle RAC 集群的安装(保姆级教程)_oracle rac集群搭建

- 7前端和后端如何进行交互?

- 8JeecgBoot单体搭建及部署保姆式教程_jeecg-boot

- 9测试开发——用例篇(如何设计一个测试用例,设计测试用例的一些具体方法)_测开设计测试用例

- 10[杂谈]-ESP32中的无线通信协议

EDA实验-----正弦信号发生器的设计(Quartus II )_quartus正弦信号发生器

赞

踩

目录

一、实验目的

- 学习使用Verilog设计波形发生器。

- 掌握LPM_ROM在波形发生器设计中的使用方法。

二、实验仪器

- PC机

- EDA实验箱 一台

三、实验原理

FPGA中的波形发生器控制电路,它通过外来控制信号和高速时钟信号,向波形数据ROM发出地址信号,输出波形的频率由发出的地址信号的速度决定;当以固定频率扫描输出地址时,模拟输出波形是固定频率,而当以周期性时变方式扫描输出地址时,则模拟输出波形为扫频信号。

波形数据ROM中存有发生器的波形数据,如正弦波或三角波数据。当接受来自FPGA的地址信号后,将从数据线输出相应的波形数据,地址变化得越快,则输出数据的速度越快,从而使D/A输出的模拟信号的变化速度越快。

四、实验内容

设计一个基于LPM_ROM的正弦波信号发生器,并进行仿真测试及实验系统上的硬件测试。(附加:正弦波的频率可调,相位可调)

五、实验步骤

- 打开QUARTUSII软件,新建一个工程。

- 新建一个Schematic File 文件。

- 利用波形生成器生成正选波的.mif文件,数据为8数,一个周期为128个数据。

- 定制LPM_ROM。

- 设计ROM的地址发生器。

- 在Schematic File 文件中设计正弦波信号发生器。在空白处双击鼠标左键,在 Symbol 对话框左上角的libraries 中,分别将创建模块放在图形文件 Schematic File中,加入输入、输出引脚,双击每个引脚,进行引脚命名,并锁定管脚,将未使用的引脚设置为三态输入(一定要设置,否则可能会损坏芯片)

- 编译仿真无误后,参照附录进行管脚分配。下表是示例程序的管脚分配表。分配完成后,再进行全编译一次,以使管脚分配生效。

| 端口名 | 对应FPGA管脚 | 说明 |

| CLK | 209 | 时钟为50MHZ |

| RST | 153 | 复位 |

| DOUT | 167、165、166、162、164、159、161、156 | 输出数据 |

8.用下载电缆通过JTAG口将对应的sof文件加载到FPGA中。观察实验结果是否与自己的编程思想一致

六、注意事项

- 注意观察当输入数据改变是输出的反应。

- 一定要把没用的管脚设置成三态输入。

- 对实验现象进行分析总结。

七、实验过程(操作过程)

1.定制LPM_ROM模块

打开Mif任意波编辑器Mif_Maker2010

这个软件我上传到了百度网盘,可自行下载。

链接:https://pan.baidu.com/s/1PqheFDBqXH4oLtOjMfv_Vg?pwd=9458

提取码:9458

这里我们点击查看这里,然后设置全局参数。

然后就是点击波形,设置正弦波。

弄完了之后,就保存这个.mif文件,最好保存到你当前的工程目录下。

这里我们可以去通过记事本打开这个.mif文件,可以查看里面的相关参数

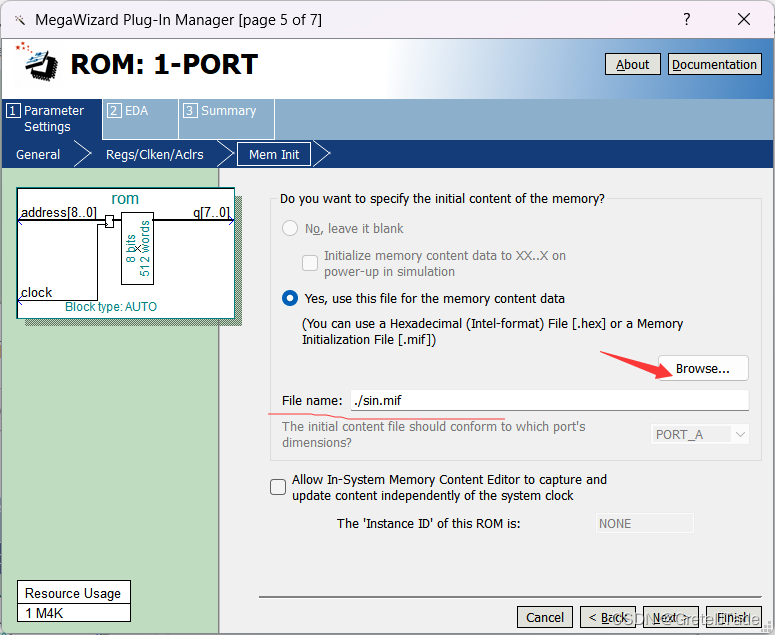

2.定制LPM_ROM元件

这里我们创建了工程后,创建一个block文件,然后点击选择元器件,再点开此处。

然后下一步

然后我们搜索rom,下面就会有两个元器件显示,选择第一个,然后在右边箭头的位置写上你的ROM元器件的命名,再点击下一步。

然后这里去设置输出量q的宽度和设置地址线宽。这里我们输出设置为8个宽度,储存容量设置为512e words。

然后这里去设置输出量q的宽度和设置地址线宽。这里我们输出设置为8个宽度,储存容量设置为512e words。

这里的‘q’不勾选。

这里我们把第一步创建好了的.mif文件添加到这里来。

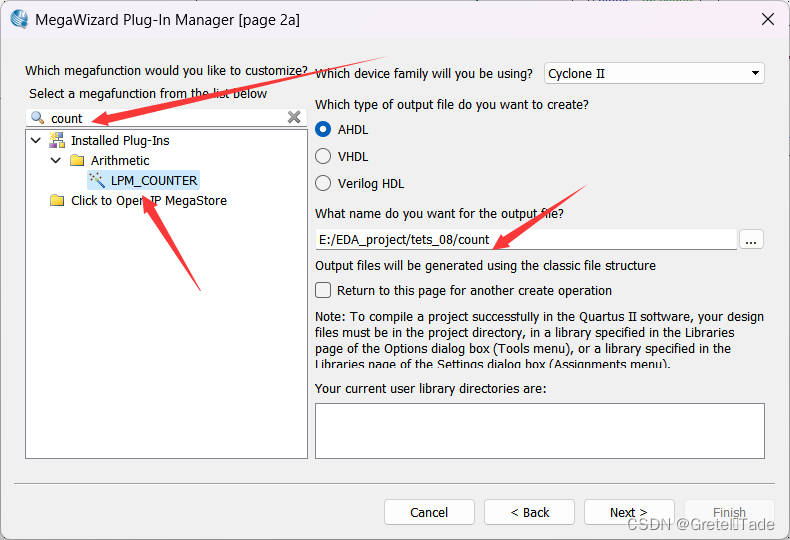

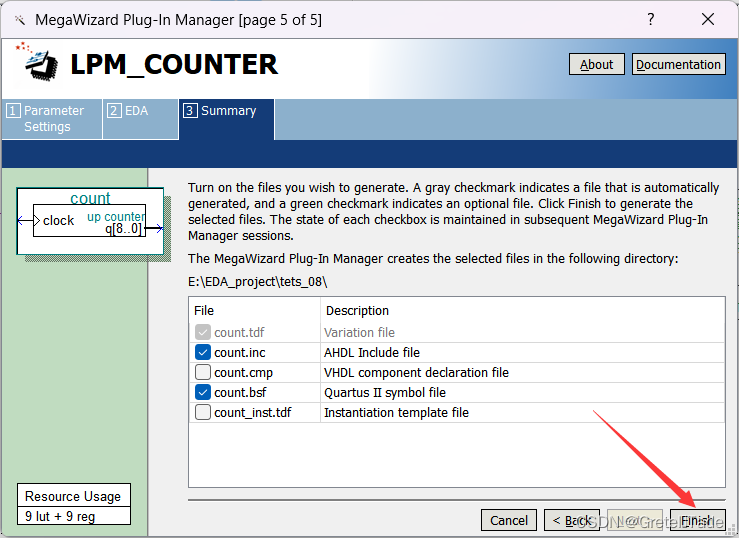

3.计数器定制

在元器件定制这里,我们搜索count,然后去命名,再点击下一步。

这里的输出要连接到前面定制的ROM元件的地址,所以位宽要与地址的位宽保持一致。

然后一直点击下一步就行了,创建完成。

4.创建锁相环

同样的在元件定制界面上

- 搜索pll

- 下面就会显示出ALPLL,点击选中

- 然后进行命名

输入频率我们设置为50MHz

这里不勾选任何。

到这里,我们把输出频率设置为10MHz。

然后一直点击下一步,最后创建完成。

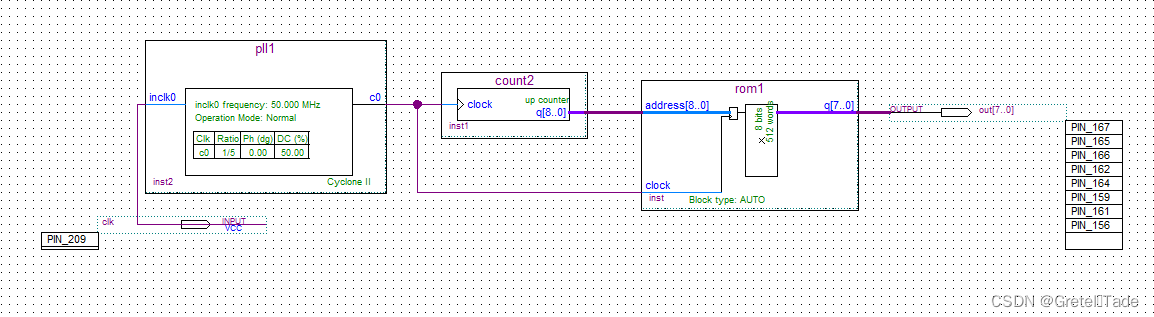

5.作出电路图

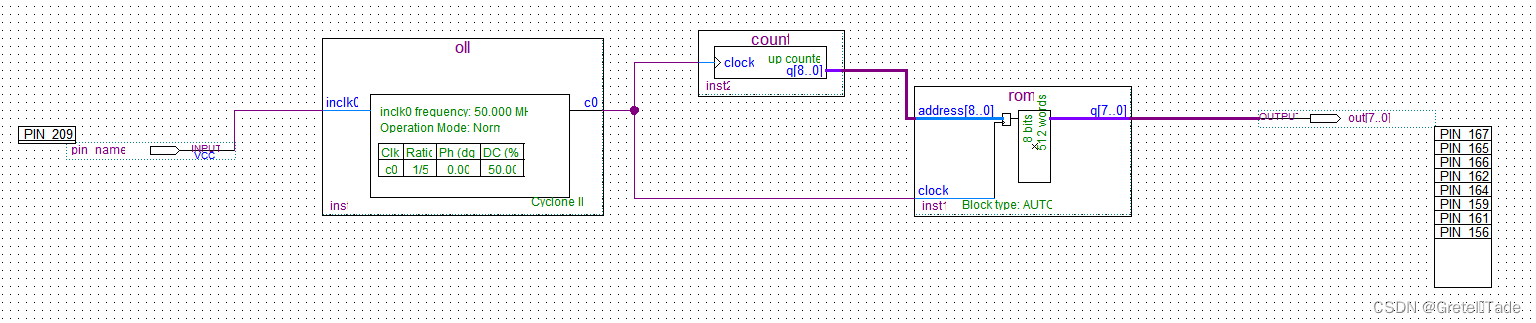

最后我们根据上文的电路图去连接电路,并且配置相关的引脚,结果如下:

然后就是编译运行,结果无误。

6.顶层设计仿真

电路图编译运行无错后,我们就把sof文件烧录到开发板上。

这里我们会看到,下面有一个芯片,这个也就是我们写好了的sof文件,然后就是通过你的电脑接口去连接到开发板,如果你看到上面有一个No Hardware的时候,你点击旁边的按钮进行接口设置,设置为USB接口即可(USB线连接了你的开发板就会自动显示出来的)。最后点击start就可以进行烧录了。

烧录后,别断开与开发板的连接,还没完呢。

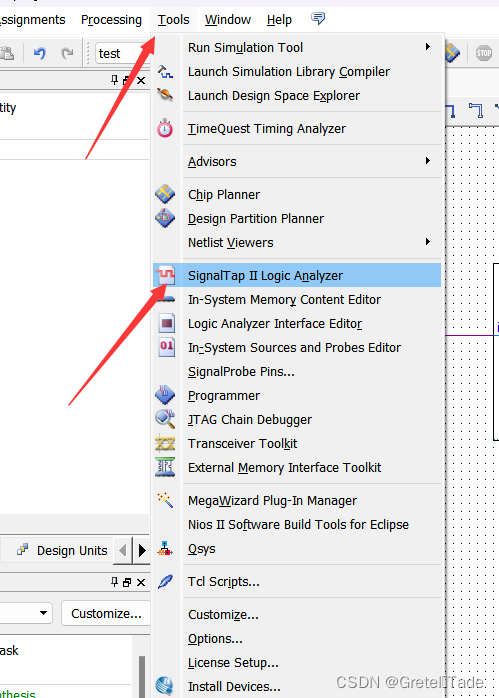

我们点开此处,使用SignalTap II Logic Analyzer去仿真。

在这里点击setup,去进行相关设置。

这里我们点开时钟设置,然后点击SignalTap I: pre-synthesis这个模式,按照下图的1,2,3步骤操作。

然后,选择输入管脚,把这个管脚作为一个时钟设置。

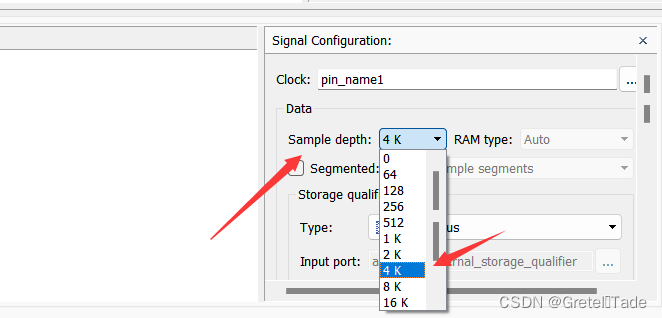

这里进行区间描点设置。前面我们设置的正弦波一个周期是512个点的,那这里我们选择的最好大于512就行了,我这里选择4k,也就是一个周期作4k个点。

这里我们去设置监视仿真输出。以下步骤执行完成之后,点击OK就行了。

最后这里,我们先看到右边的两个箭头,如果你已经连接好了开发板后,这些会显示出来的,同样的我们也可以去执行烧录操作。然后我们只需要去点击左边箭头指向的的仿真即可。

结果如下所示:

实验完毕。

以上就是本次实验的全部内容了,喜欢的话给个关注吧!

分享一张壁纸: