- 1Typora + PicGo + Gitee/GitHub 免费搭建个人图床_gitee+github

- 2CONVERT 转换函数的简单使用方法_convert函数

- 3数据结构--带头结点的单向链表_带头结点的单链表

- 4JavaScript 中的数学与时光魔法:Math与Date对象大揭秘

- 5网络运输层之(3)GRE协议

- 6OpenCV安装:最基础的openCV程序运行示例_opencv安装程序

- 7如何利用python选股

- 8数据结构修炼第一篇:时间复杂度和空间复杂度_栈和队列的时间复杂度和空间复杂度

- 9计算机网络管理 常见的计算机网络管理工具snmputil,Mib browser,SNMPc管理软件的功能和异同_snmp网络管理软件

- 10基于n-gram模型的中文分词_ngram分词

Verilog(3)I2C通信协议_用verilog写一个i2cmaster和slave的模型

赞

踩

1.1:

I2C全称:Inter-Integrated Circuit,是一种同步、半双工的通信总线。

同步:发送接收端要严格同步,一般有同步时钟线。

半双工:I2C只有一条数据线,所以master发数据与收数据不能同时进行。

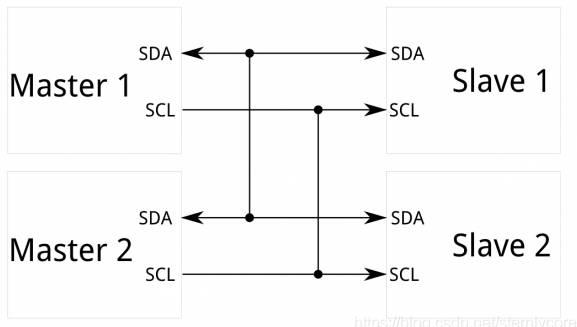

图中是2个master+2个slave的示意,同一时刻只有一个master与一个slave通信。若想实现这个效果:

1.多个master-slave 时钟、数据线连在一起,需要实现信号的“线与”逻辑(所以SDA、SCL 被设计为漏极开路结构,外加上拉电阻实现“线与”)。

2.需要实现 “时钟同步”和“总线仲裁”,引脚在输出信号的同时还能对引脚上的电平进行检测,检测是否与刚才输出一致,为 “时钟同步”和“总线仲裁”提供硬件基础。

3.I2C在读写时需要带上设备地址,这样不使用多的信号线就可指定特定的slave(而SPI通信需要多的片选线)。

1.2:

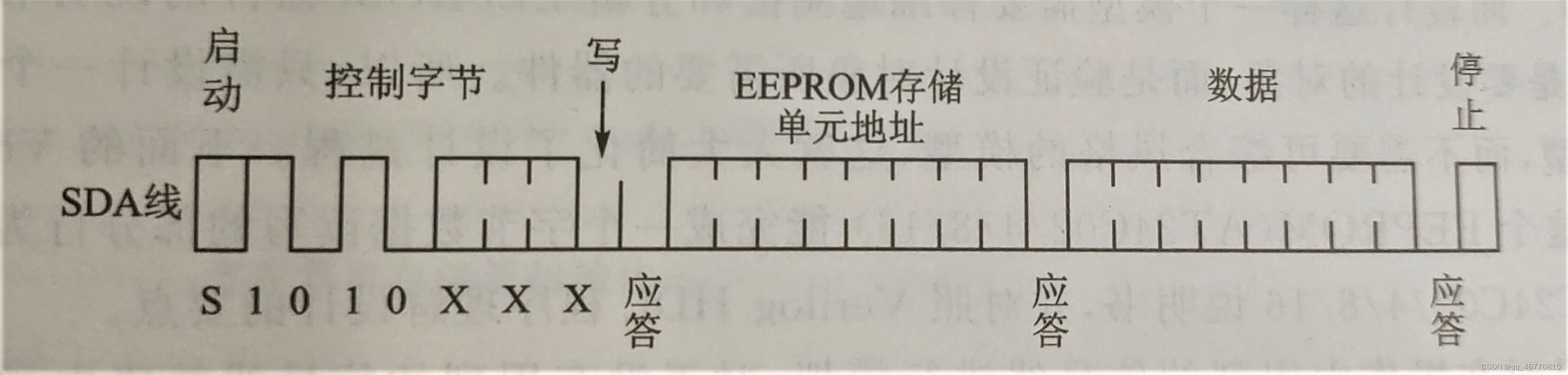

写过程:

Master发起START

Master发送I2C addr(7bit)和W(写)操作0(1bit),等待ACK

Slave发送ACK

Master发送reg addr(8bit),等待ACK

Slave发送ACK

Master发送data(8bit),即要写入寄存器中的数据,等待ACK

Slave发送ACK

第6步和第7步可以重复多次,即顺序写多个寄存器

Master发起STOP结束传输

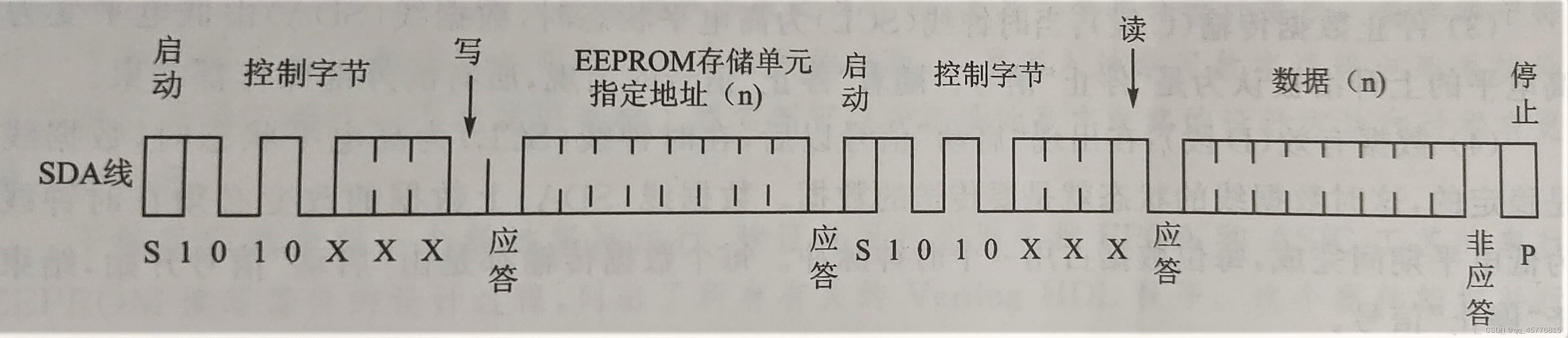

读过程:

Master发起START

Master发送I2C addr(7bit)和r(读)操作1(1bit),等待ACK

Slave发送ACK

Slave发送data(8bit),即寄存器里的值

Master发送ACK

第7步和第8步可以重复多次,即顺序读多个寄存器

当master接收完想要的数据后,由Master发送NACK,告知slave停止发送数据

Master发送STOP结束传输

1.3:

1.总线空闲状态:

SDA和SCL同时处于高电平时,规定为总线的空闲状态。此时各个器件的输出级场效应管均处在截止状态,即释放总线,由两条信号线各自的上拉电阻把电平拉高。

2.总线START:

SCL为高电平时,SDA由高电平向低电平跳变,开始传送数据。

3.总线STOP:

SCL为高电平时,SDA由低电平向高电平跳变,结束传送数据。

4.总线Restart:

SCL为高电平时,SDA由高电平向低电平跳变,本质上也是START信号,用在完整I2C读过程中的读阶段,在首次发送停止信号之前,master通过发送Restart信号,可以转换与当前slave的通信模式(从写模式到读模式),或是切换到与另一个slave通信。

5.数据阶段:

在IIC总线上传送的每一位数据都有一个时钟脉冲相对应(或同步控制),即在SCL串行时钟的配合下,在SDA上逐位地串行传送每一位数据。进行数据传送时,在SCL呈现高电平期间,SDA上的电平必须保持稳定。只有在SCL为低电平期间,才允许SDA上的电平改变状态。简单的说就是,数据在SCL下降会被采样,所以SDA需要在SCL为高电平时保持稳定。

6. ACK与NACK信号:

IIC总线上的所有数据都是以8位字节传送的,发送器每发送一个字节,就在第9个时钟脉冲期间释放数据线,由接收器反馈一个应答信号。应答信号为低电平时,规定为有效应答位(ACK简称应答位),表示接收器已经成功地接收了该字节;应答信号为高电平时,规定为非应答位(NACK),一般表示接收器接收该字节没有成功。

这段话再说细一点:

在写阶段,master写了一字节数据,在第9个时钟脉冲期间释放数据线,由slave反馈应答信号,ACK(低)表示数据成功接收,NACK(高)表示该字节没有接收成功;

在读阶段,master向slave收数据,slave写了一字节数据,在第9个时钟脉冲期间释放数据线,由master反馈应答信号,ACK(低)表示数据成功接收,NACK(高)表示该字节没有接收成功。

还有一种特殊情况:当master决定不再接收数据时,应向slave发送NACK信号,高速slave不再发送。

以下情况会导致出现NACK位:

1.接收器没有发送机响应的地址,接收端没有任何ACK发送给发送器

2.由于接收器正在忙碌处理实时程序导致接无法接收或者发送

传输过程中,接收机器别不了发送机的数据或命令

3.接收器无法接收

4.master接收完成读取数据后,要发送NACK结束告知slave。

当master接收到slave的NACK信号后,可以STOP这次传输,也可以重新START。

所以:NACK并不只是表示字节没有成功接收,也可以表示master告诉slave不再需要发送数据。

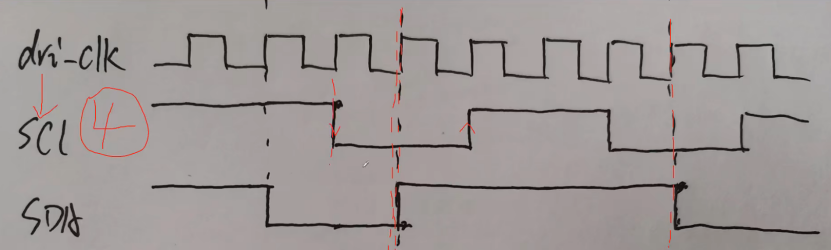

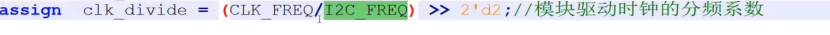

分频系数就是scl一个周期有几个clk,dri_clk=4*scl,所以分频系数再除以四(等价于右移两位)。

- //I2C的SCL四倍频

- always@(posedge clk or negedge rst_n)begin

- if(!rst_n)begin

- dri_clk <= 1'b0;

- clk_cnt <= 10'd0;

- end

- else if(clk_cnt == clk_divide[8:1] - 1'd1)begin

- clk_cnt <= 10'd0;

- dri_clk <= ~dri_clk;

- end

- else

- clk_cnt <= clk_cnt + 1'd1;

- end