- 1Linux查看网络带宽使用情况_linux网卡使用率百分比

- 2使用 Flutter 打造引人入胜的休闲游戏体验

- 3ananconda环境中,出现SSLError报错_conda sslerror

- 4python远程文件管理系统_python 读取远程服务器文件

- 5自制【平衡小车】程序篇——基于STM32核心_stm32平衡小车pid算法程序

- 6关于camera:基于S12单片机的循迹小车视觉系统设计与优化_像素帧数小车

- 7做ROS小车实物的第一天_用ros做一个实物出来要多久

- 8数据结构之链表练习题(leetCode)_先将键盘输入的一组整数依次存入循环链表(尾插法),然后删除头部第一个元素,最后将

- 9Debezium系列之:Debezium2.X之Oracle数据库的Debezium连接器_io/debezium/connector/oracle/rest/debeziumoracleco

- 10Docker容器中的OpenCV:轻松构建可移植的计算机视觉环境_容器中显示cv::imshow

【FPGA】Robei EDA的使用(8)——Quartus上板实验_qurtus17.1 如何上板

赞

踩

#致知穷理,学古探微;立德立言,无问西东。

之前在Robei的赛杯群里,看到有人问关于如何将robei 的文件导入Quartus并下载,Robei在各个教程里,确实也从没有写过关于如何和Quartus联调的教程。趁着这几天刚好在 Altera的板子上写代码,就顺便写个博客,供大家参考。

——————————————————以下是正文的分割线————————————————

以流水灯代码为例(这个最简单但也最具有代表性)

Robei 部分

-

top 文件

在把各个模块写好之后,要有一个顶层文件包含所有的模块。

-

FPGA的配置

在Robei EDA 的Setting中,可以选择FPGA的品牌和开发环境。目前只有Xilinx的Vivado和Altera的Quartus。(严格来说是Intel家的FPGA)

不过,还是希望Robei早日把兼容国产FPGA的开发环境提上日程,比如上海安路和广东高云。

-

生成管脚约束文件

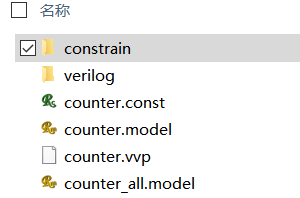

新建文件,选择类型为constrain,命名并保存。

将模块拖拽到页面上,进行连线。

-

IO口分配

根据自己开发板上面的芯片对应外设的管脚,把对应的管脚分配给Robei上Ports。

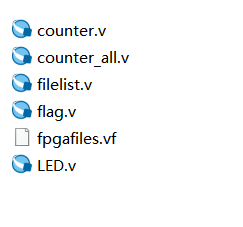

点击下载样子的按钮,会看到告知管脚文件生成。这个时候,回到文件的文件夹,就能看到robei自动生成的代码和管脚约束文件。(就生成流程来说,vivado和Quartus其实没有太大区别,只是对于两者的EDA来说,Xilinx的管脚约束文件是xdc,而Quartus的是qsf)

点击下载样子的按钮,会看到告知管脚文件生成。这个时候,回到文件的文件夹,就能看到robei自动生成的代码和管脚约束文件。(就生成流程来说,vivado和Quartus其实没有太大区别,只是对于两者的EDA来说,Xilinx的管脚约束文件是xdc,而Quartus的是qsf)

Quartus 部分

-

新建Quartus Project

这个新建Project就不放教程讲了,不会的直接搜索“Quartus新建工程文件”就可以了。(我用的版本是破解版的17.1) -

导入Verilog代码和qsf约束文件

和Vivado有所不同的是,在vivado里的管脚约束xdc文件和Verilog是分开导入的。但是在Quartus里,在创建新工程时,只导入Verilog代码,qsf文件是在工程建立后才添加的。

可以看到文件已经成功添加入工程中。在Assignment中选择Import,可以对工程添加qsf文件。

添加完之后,可以进行整体的综合编译,编译成功后,选择Pin Planner,可以看到管脚已经被分配好了。

-

编译下载

导入文件后,可以在file中看到。导入即可直接进行综合,综合成功后烧录代码。 -

上板实验

因为上板测试是在实验室做的,但是博客是在宿舍写的,所以就没有成功的图。下次在再补。

——————————————————正文结束的分割线———————————————

唉,最近事情不是一般的多,实验报告、大作业、课程论文,好多事情叫你忙来忙去。Robei的进展也不是很好,摄像头一直有各种奇怪的问题,令人头大。太打击人了,可是每每想放弃,又非常的

不甘心,毕竟自己已经花了这么多时间在这上面,这个时候放弃就太吃亏了。给自己加油吧~