- 1修改jar包文件并重新打包_android jar重新打包

- 2Golang框架:cobra_golang cobra

- 3第31篇-SAP MRP最小安全库存和服务水平的研究学习、思考_sap里service level

- 4bfs的Floodfill算法_floodfill算法例题

- 5GPT-4对编程开发的支持_gpt4可以写代码吗

- 6<网络安全>《68 微课堂<第9课 常见IT系统集成商简介>》

- 7Suno AI:如何使用应用程序通过 AI 创作精彩歌曲

- 8Django图书商城系统实战开发 - 实现个人中心管理_django个人中心

- 9python 机器人聊天_使用python构建您的第一个聊天机器人并将其集成到电报中

- 10vue3 自定义指令_vue3自定义指令流程

SDC学习之set_clock_group_sdc clock group

赞

踩

目录

-set_clock_group

clock_group实际上就如同字面意思,有关联的时钟会作为同一个group,不相关的时钟可以设置为不同group,这样系统就不会分析不相关时钟之间的path,减少时序分析的时间。

Set Clock Groups(set_clock_groups) 约束可以用于指定设计中的哪些时钟是不相关的。默认情况下,假设所有具有公共基本(common base)或父时钟 (parent clock) 的时钟都相关,并且这些时钟域之间的所有传输都适用于时序分析。我们可以通过切割时钟组 (cutting clock groups) 来排除时序分析中特定时钟域之间的传输。set_clock_groups 命令能够切断不同组中不相关时钟之间的时序。无论是指定 -exclusive 还是 -asynchronous 组,都会执行相同的分析。使用 -group 选项定义组可以排除每个独立组的时钟之间的时序路径。

可以定义时钟信号组,然后定义每个组之间的关系。定义时钟信号包括在每个 Group (-group)中,然后指定组是否是 Logically exclusive (-logically_exclusive),Physically exclusive (-physically_exclusive) 或者 Asynchronous ( -asynchronous)。

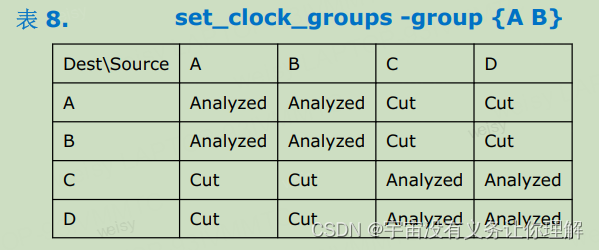

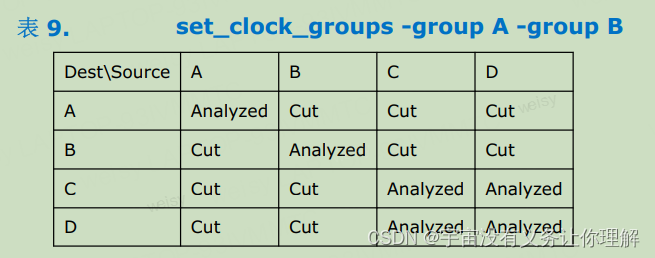

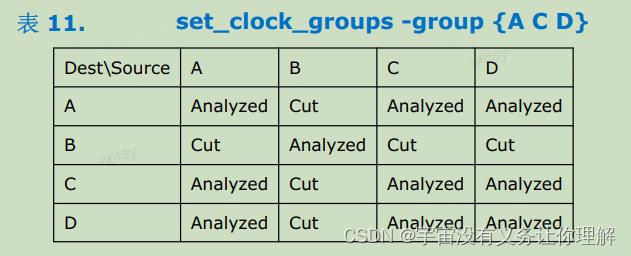

下表显示了set_clock_groups的影响。

只有时钟A被设置为clock_group,杜绝了A和其他时钟之间的时序分析,此时只有A-A和其他剩余时钟之间的两两时序分析。

AB被设置为一个clock_group,此时AB和其他时钟之间的时序分析被cut,但是同一个group之内会时序分析,即AB之间会分析,group之外的时钟会时序分析,即CD之间会时序分析。

当A和B被设置为不同的group时,对group A分析,A和其他时钟之间的时序分析被cut,同理B和其他时钟的时序分析也被cut,C和D之间会时序分析。

当AC/BD被设置为同一个group时,AC和其他时钟之间的时序分析被cut,但是AC之间会进行时序分析,同理可得BD。

当ACD被设置为同一group,ACD和其他时钟之间的时序分析被cut,但是同一个group之间会进行时序分析。

-asynchronous

如果两个时钟在设计中不相互通信,则它们是异步的。例如,free-running&on-chip的振荡器相对于从外部进入芯片的系统时钟信号是异步的。两个时钟域中的时钟边沿可以相对于彼此随时出现。

可以将两个时钟之间的关系声明为异步,在这种情况下,工具不会检查由一个时钟 launche 并由另一时钟 capture 的时序路径,这就像声明两个时钟之间set false path一样,要声明两个时钟之间的异步关系,请使用set_clock_groups -asynchronous命令。

在工艺进入深亚微米后,由于串扰的影响,建立时间和保持时间的检查也会受串扰的影响而产生变动,当用户希望执行串扰分析时,可以使用 -allow_path这个选项,这个选项仅可以和-asynchronous一块,代表执行串扰分析而不禁用时钟之间的时序电路路径。

-logically_exclusive

如果两个时钟不互相影响,那么它们就是互斥的。例如,电路可能将两个不同的时钟信号复用到一条时钟线上,一个是用于正常操作的快速时钟,另一个是用于低功耗操作的慢速时钟。在任何给定时间仅启用两个时钟之一,因此两个时钟之间没有交互。这种互斥时钟在仿真时不会同时toggle。

为了防止工具花费时间分析exclusive时钟之间的交互,您可以声明时钟之间的false path或使用命令set_clock_groups -logically_exclusive声明时钟为独占时钟,或者也可以使用case analysis来禁用不希望考虑的时钟。

声明时钟 CK1 和 CK2 逻辑上互斥:

set_clock_groups -logically_exclusive -group {CK1} -group {CK2}这会导致该工具忽略从 CK1 域开始并在 CK2 域结束或从 CK2 到 CK1 域结束的任何时序路径。这就像设置一条从 CK1 到 CK2 以及从 CK2 到 CK1 的 false path。要了解已设置的时钟组,请使用report_clock -groups 。

可以在每个组中指定多个时钟。例如,声明时钟 CK1 和 CK2 与 CK3 和 CK4 互斥:

- set_clock_groups -logically_exclusive \

- -group {CK1 CK2} -group {CK3 CK4}

这会导致该工具忽略在一个组中开始并在另一组中结束的任何路径。

如果指定两个以上的组,则每个组相对于其他指定的组都是互斥的。例如,

- set_clock_groups -logically_exclusive \

- -group {CK1 CK2} -group {CK3 CK4} -group {CK5}

如果您仅指定一组,则该组相对于设计中的所有其他时钟而言是排他的。例如,

set_clock_groups -logically_exclusive -group {CK1 CK2}您可以选择为时钟组声明分配一个名称,这样以后可以更轻松地删除该特定声明:

- set_clock_groups -logically_exclusive -name EX1 \

- -group {CK1 CK2} -group {CK3 CK4}

使用remove_clock_groups命令删除时钟分组声明:

remove_clock_groups -logically_exclusive EX1要删除使用以下命令所做的所有独占时钟分组声明set_clock_groups:

remove_clock_groups -logically_exclusive -all-physical_exclusive

-physically_exclusive —— 定义物理上独占并且同时又不活动的时钟。

由于时钟信号的复用或物理分离,时钟组可以是physical exclusive的,也可以是logical exclusive的。物理上互斥的时钟之间不能有串扰,也不能有逻辑交互。在这种情况下,使用-physically_exclusive选项而不是-logically_exclusive。这可以防止工具尝试在时钟网络之间执行串扰分析。

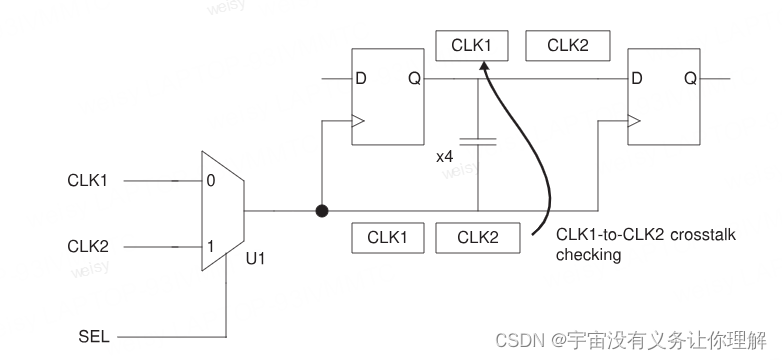

要同时分析两个时钟,您可以将它们定义为逻辑上互斥的:

- set_clock_groups -logically_exclusive \

- -group {CLK1} -group {CLK2}

该-logically_exclusive选项使工具禁止 CLK1 和 CLK2 之间的任何逻辑(时序路径)检查。然而,它仍然计算两个时钟之间耦合电容器 x4 上的串扰增量延迟,但是分析结果可能不那么乐观,因为两个时钟永远不会同时出现在网络上。为了消除这种分析,请将时钟定义为物理上互斥的:

- set_clock_groups -physically_exclusive \

- -group {CLK1} -group {CLK2}

然后,该工具会忽略物理上互斥时钟网络之间的任何串扰,并抑制时钟之间的逻辑检查。这消除了对电容器 x4 上 CLK2 和 CLK1 之间串扰的悲观分析。