热门标签

热门文章

- 1npm安装时一直idealTree:npm: sill idealTree buildDeps卡住不动

- 2python3.6使用line-profiler踩坑记录_line-profiler-4.1.3与python3.6适配吗

- 3使用 CSS 实现垂直居中的5种方法_css 定位垂直居中

- 4超声成像_人工智能如何帮助转变医学超声成像

- 5入职接一个月来谈谈华为OD的感受(拜托入职佬写的,一字未改)

- 6虚拟机上的ubuntu本地跟gitlab或gitee远程仓库建立连接_虚拟机设置绑定gitee

- 7SMB协议简单免费搭建个人winNAS_windows smb服务

- 8Scikit-learn库的基础与使用_scikit-learn机器学习算法库

- 9jmeter测试mysql数据库_【JMeter】JMeter完成一个MySql压力测试

- 10【重磅开源】MapleBoot权限控制使用介绍(菜单权限、按钮权限、数据权限)

当前位置: article > 正文

vivado 与 VIO 核输出探针进行交互_vivado vio

作者:AllinToyou | 2024-06-11 18:41:44

赞

踩

vivado vio

与

VIO

核输出探针进行交互

VIO

核输出探针用于将值写入实际硬件中的

FPGA

或

ACAP

中运行的设计。

VIO

输出探针通常用作为待测设计的低带

宽控制信号。

VIO

调试探针需手动添加到

VIO

仪表板的“

VIO

探针

(VIO Probes)

”窗口中。请参阅“在‘调试探针

(Debug Probes)

’窗口中查看

VIO

核”章节

,

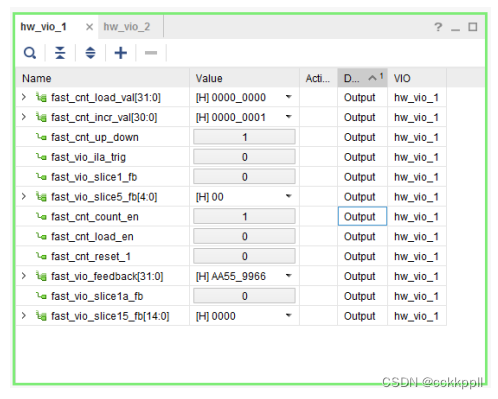

以了解具体方法。下图中显示了

VIO

仪表板的“

VIO Probes

”窗口中的

VIO

输出探针示例。

使用

VIO

核视图来编写

VIO

输出

VIO

输出探针可使用“

VIO

仪表板

(VIO Dashboard)

”窗口的“

VIO

探针

(VIO Probes)

”窗口来进行设置。每个输出探

针均可作为表格中的单独一行来查看。

VIO

输出探针的值显示在表中的“值

(Value)

”列中

(

请参阅“与

VIO

核输出探

针进行交互”

)

。只要在“

Value

”列中输入新的值

,

就会更新

VIO

核输出值。单击“

Value

”列即可显示下拉对话

框。您可在“

Value

”文本字段中输入期望的值

,

然后单击“

OK

”。

也可以使用

Tcl

命令将新的值写出至

VIO

核。例如

,

如果要将二进制值“

11111

”写出至名为

vio_slice5_fb_2

且

基数已设为

BINARY

的

VIO

输出探针

,

请运行以下

Tcl

命令

:

set_property OUTPUT_VALUE 11111 [get_hw_probes vio_slice5_fb_2]

commit_hw_vio [get_hw_probes {vio_slice5_fb_2}]

相关信息

与

VIO

核输出探针进行交互

设置

VIO

输出显示类型和基数

VIO

输出探针的显示类型可通过如下方式进行设置

:

在“

VIO Dashboard

”窗口的“

VIO Probes

”窗口中右键单击

VIO

输出探针并选择

:

• “

Text

”

,

用于将输出显示为文本字段。这是对应

VIO

输入探针矢量

(

位宽大于

1

)

的唯一显示类型。

• “

Toggle Button

”

,

用于将输出显示为切换按钮图形。此显示类型仅适用于

VIO

输出探针标量以及

VIO

输入探针

矢量的个别元素。

当

VIO

输出探针的显示类型设置为“

Text

”时

,

您可通过如下方式更改基数

:

在“调试探针

(Debug Probes)

”窗口的

“

VIO

核

(VIO Cores)

”选项卡视图中

,

右键单击

VIO

输出探针并选择

:

• “

Radix

” → “

Binary

”

,

以将基数更改为二进制。

• “

Radix

” → “

Octal

”

,

以将基数更改为八进制。

• “

Radix

” → “

Hex

”

,

以将基数更改为十六进制。

• “

Radix

” → “

Unsigned

”

,

以将基数更改为无符号十进制。

• “

Radix

” → “

Signed

”

,

以将基数更改为有符号十进制。

您还可使用

Tcl

命令来设置

VIO

输出探针的基数。例如

,

要将名为“

vio_slice5_fb_2

”的

VIO

输出探针的基数更改为十

六进制

,

请运行以下

Tcl

命令

:

set_property OUTPUT_VALUE_RADIX HEX [get_hw_probes vio_slice5_fb_2]

复位

VIO

核输出值

VIO v2.0

核具有支持您为每个输出探针端口指定初始值的功能。您可在“硬件

(Hardware)

”窗口中右键单击

VIO

核并

选择“

Reset VIO Core Outputs

”选项来将

VIO

核输出探针端口复位为初始值。您还可使用

Tcl

命令来复位

VIO

核输

出

:

reset_hw_vio_outputs [get_hw_vios {hw_vio_1}]

注释

:

将

VIO

输出探针复位为其初始值可能导致输出探针值与

Vivado IDE

不同步。请参阅“将

VIO

核输出值同步到

Vivado IDE

”章节以了解有关如何处理此类情况的信息。

将

VIO

核输出值同步到

Vivado IDE

在复位

VIO

输出、对

FPGA

或

ACAP

进行重新编程或者由其它

Vivado

工具实例设置输出值之后到启动当前实例之

前

,

VIO

核的输出探针可能与

Vivado IDE

出现不同步。在上述任何情况下

,

只要

VIO

状态指示“输出不同步

(Outputs

out-of-sync)

”

,

就需要执行以下

2

项操作中的任一操作

:

• 在“硬件

(Hardware)

”窗口中右键单击

VIO

核并选择“

Commit VIO Core Outputs

”选项

,

将值从

Vivado IDE

写

入

VIO

核。您也可以运行以下

Tcl

命令来执行此操作

:

commit_hw_vio [get_hw_vios {hw_vio_1}]

• 在“

Hardware

”窗口中右键单击

VIO

核并选中“

Refresh Input and Output Values from VIO Core

”选项

,

以便使

用

VIO

核输出探针端口的当前值来更新

Vivado IDE

。您也可以运行以下

Tcl

命令来执行此操作

:

refresh_hw_vio -update_output_values 1 [get_hw_vios {hw_vio_1}]

声明:本文内容由网友自发贡献,不代表【wpsshop博客】立场,版权归原作者所有,本站不承担相应法律责任。如您发现有侵权的内容,请联系我们。转载请注明出处:https://www.wpsshop.cn/w/AllinToyou/article/detail/704356

推荐阅读

相关标签