之前在使用Altera的三速以太网MAC IP的基础上,完成了UDP协议数据传输。此次为了将设计移植到xilinx FPGA上,需要用到xilinx的三速以太网MAC IP核,当然也可以自己用HDL编写,但必须对数据链路层协议有非常清晰的认识。以下是在使用xilinx 三速以太网MAC过程中的一些记录和总结。

在使用IP核传输数据之前要对MAC层功能有个了解。MAC层功能用一个词概括就是“成帧解帧”,具体来讲TX方向对用户侧发送来的MAC帧添加前导码和帧尾校验和,对长度过短帧会在帧尾填充0直至最小帧长,此外流控模块可以根据需要发送pause帧。RX方向过滤掉不符合规范的数据帧并移除填充域,只有目的MAC地址与自身相符且帧尾校验和正确的数据帧才为有效数据帧,去除前导码和校验域后即发送给用户侧。接收端也会根据可能收到的pause帧做出暂停发送处理。

认识以太网帧结构同样非常重要,目前常见的是Ethernet II和IEEE802.3两种格式,总体可以归纳为:目的MAC地址 源MAC地址 长度/类型 有效负荷(可能有填充) 帧校验,长度依次是6byte、6byte、2byte、46~1500byte、4byte。区别在于Ethernet II帧长度/类型域解释为上层协议类型,而IEEE802.3同样位置是长度字段。区分两者的标准是:当该字段值小于等于1500(十六进制的0x05DC)时,为IEEE802.3格式;当字段值大于等于1536(或者十六进制的0x0600)时,帧使用的是Ethernet II格式。其中Ethernet II最为常见。

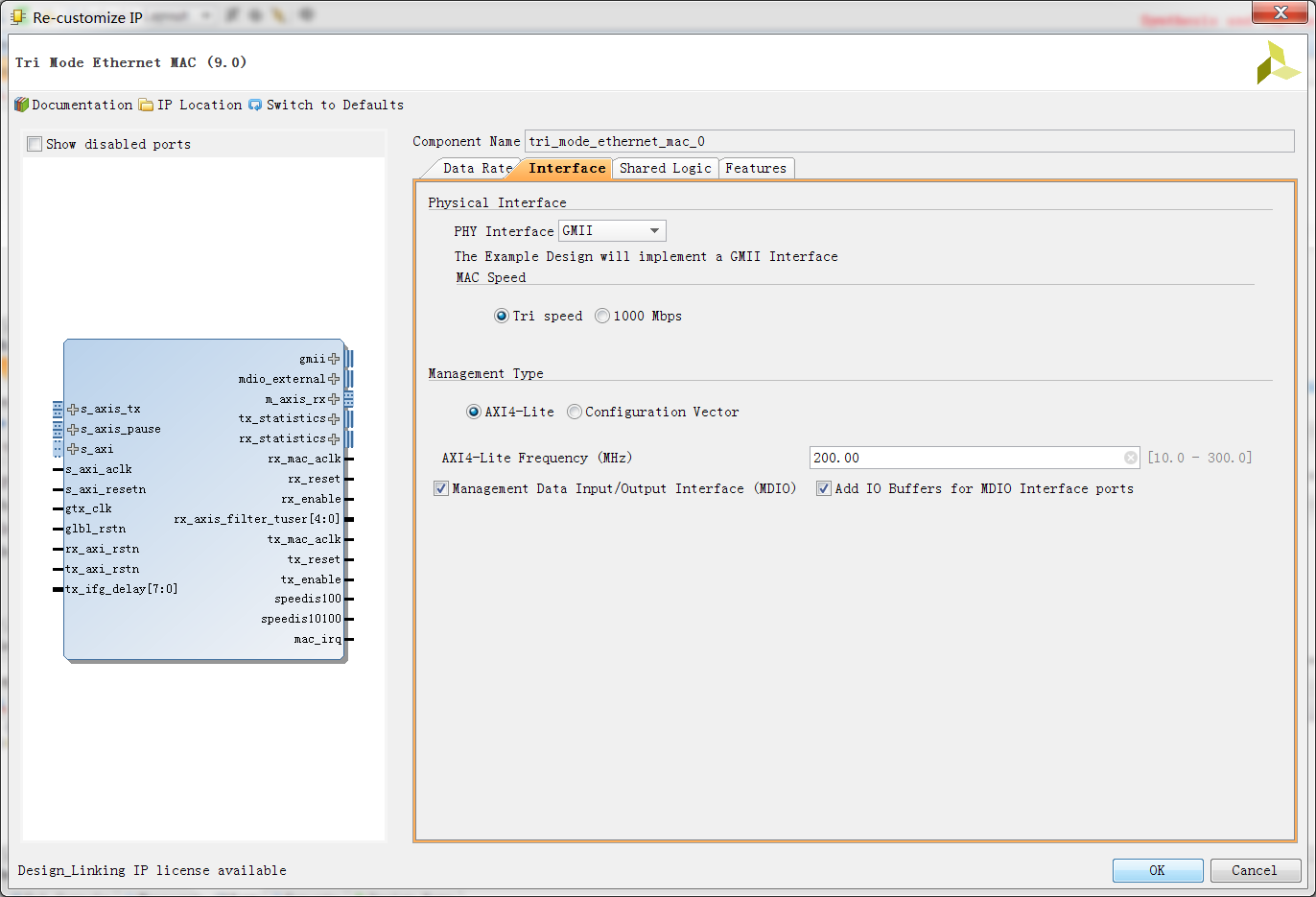

IP核的配置很简单,根据自己的需求设置即可。重点关注第二页,这里选择使用GMII作为物理层接口,并选择三速模式,可以通过接口改动传输速率。

IP核配置生成输出文件后,和其他较为复杂的IP核一样要熟读文档和分析example design的结构和功能。资料主要参考PG051.我们直接打开example design顶层文件对工程有个整体的认识:

// -------------------------------------------------- // | EXAMPLE DESIGN WRAPPER | // | | // | | // | ------------------- ------------------- | // | | | |