- 1【VUE】6、VUE项目中引入axios_vue引入axios

- 2chipscope 选不到要查看的信号解决办法_chipscope找不到信号

- 3【EI/SCOPUS征稿】第四届计算机视觉和数据挖掘国际学术会议(ICCVDM 2023)

- 4pillow软件 Android,Pillow app

- 5Linux进程线程编程练习题(附答案)_linux 有关于线程和进程的代码题

- 6毕业设计:YOLOv8车牌识别系统 深度学习 pytorch LPRNet车牌识别算法(源码+数据集)✅_yolo车牌识别毕业论文

- 7使用docker安装mysql_sudo docker start mysqldb

- 8Flink实战(7):flink checkpoint配置详解_execution.checkpointing.min-pause

- 9Navicat Premium 连接sqlserver报错:未发现数据源名并且未指定默认驱动程序_未发现数据源名称并且未指定默认驱动程序怎么解决

- 10【已解决】devtools::install_github(“immunogenomics/presto“) 报错_pkgbuild::check_build_tools(debug = true)

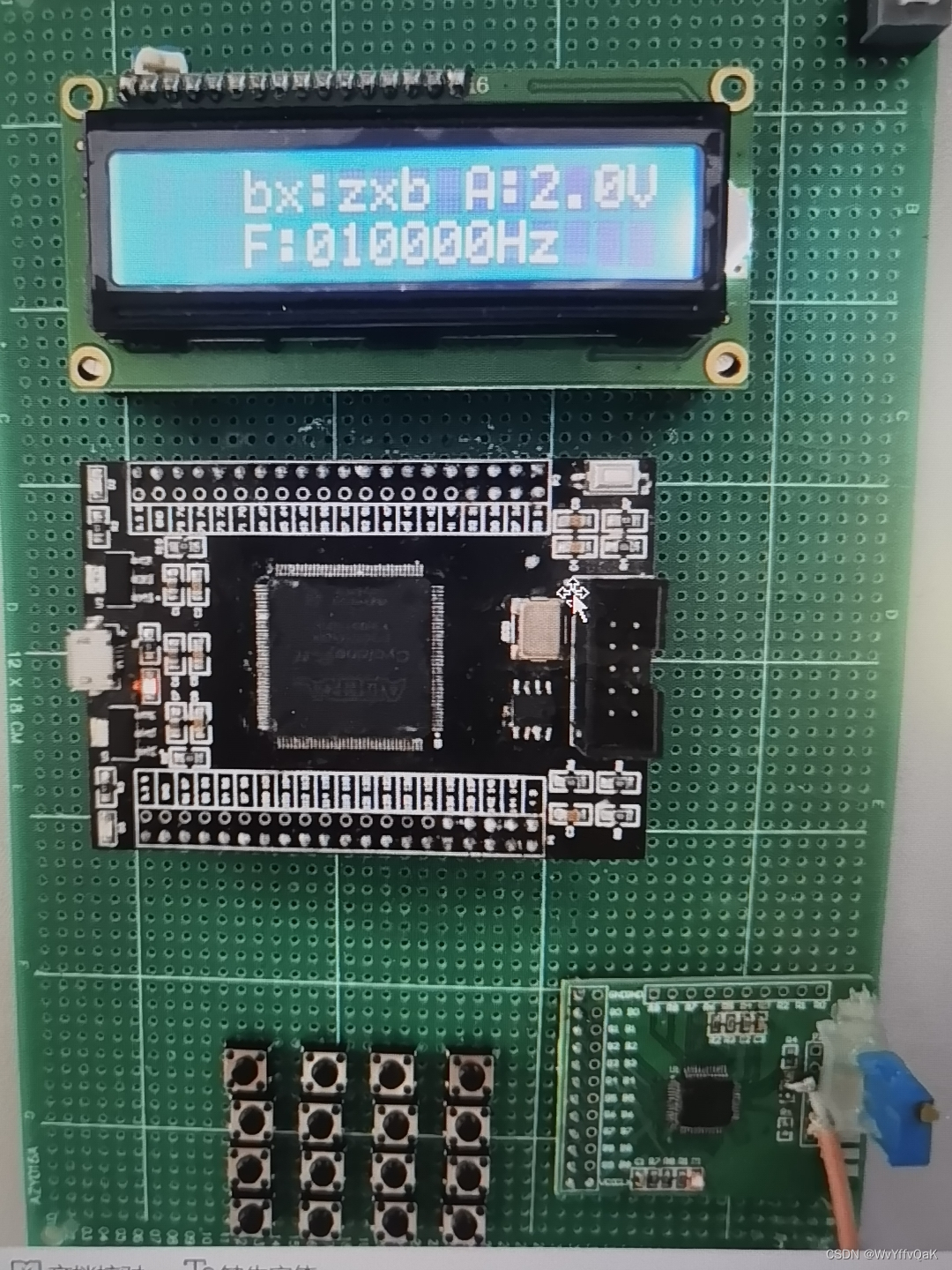

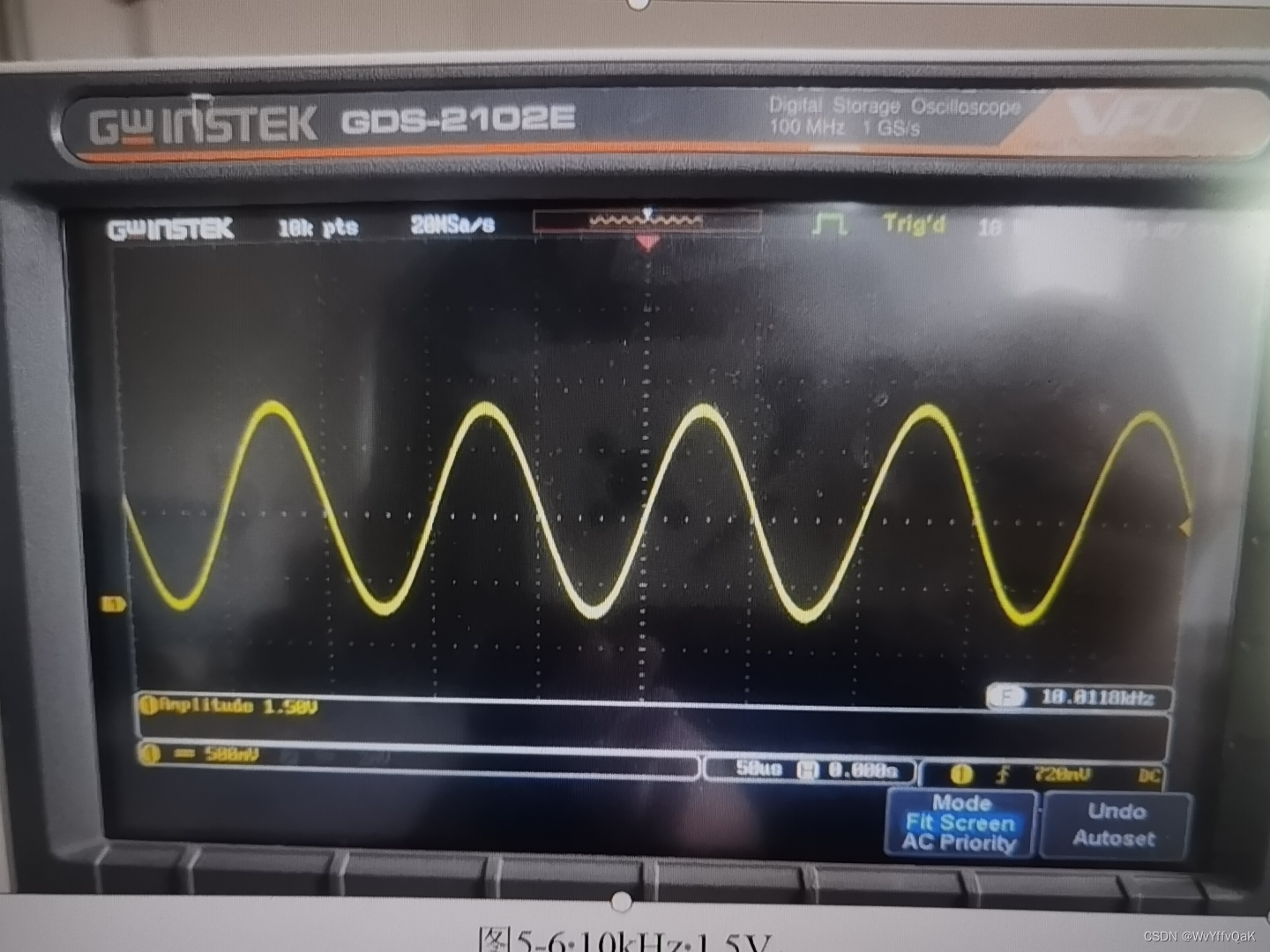

基于FPGA的DDS原理信号发生器设计 quartusII 9.1平台 Verilog HDL语言编程 可产生正弦波_dds信号发生器设计fpga

赞

踩

基于FPGA的DDS原理信号发生器设计 quartusII 9.1平台 Verilog HDL语言编程 可产生正弦波、方波、锯齿波以及三角波 频率幅度可调节 代码+原理图

在现代电子技术领域,针对各种应用的信号发生器是一种非常核心的设备,而基于现场可编程逻辑门阵列(FPGA)的直接数字合成(DDS)信号发生器是其中一种应用广泛的设备。这篇文章将介绍如何使用Quartus II 9.1平台和Verilog HDL语言编程设计一种基于FPGA的DDS原理信号发生器,该设备可以产生正弦波、方波、锯齿波以及三角波,同时频率幅度也可以进行调节。

首先,我们需要了解DDS原理信号发生器的工作原理。DDS技术是一种利用数字方式控制产生测量信号的新技术,它是通过一个数字信号处理器(DSP)来控制一片存储器中的频率定标值,再通过数字相乘器,产生出某一频率的正弦信号。该设计流程中,使用的是Quartus II 9.1平台和Verilog HDL语言编程,以实现该设备的设计。

其次,我们需要使用脉冲宽度调制(PWM)技术,在数字域内来产生正弦波、方波、锯齿波以及三角波。PWM技术是一种将一个传统的信号转化成PWM波形的技术,而在这种基于FPGA的DDS原理信号发生器中,通过调整频率的方法把信号转化成PWM波形,以产生出各种不同类型的波形信号。

最后,需要将代码和原理图整合起来,以实现基于FPGA的DDS原理信号发生器的设计。这种设备的设计可以使用多种不同的方案,其中一种最为常见的方案是使用一种基于FPGA的数字信号处理器(DSP)作为芯片,再加上一些数字电路和逻辑控制的电路,来实现该设备的设计。

综上所述,基于FPGA的DDS原理信号发生器是一种非常重要的数字电路设备,它能够产生各种不同类型的信号波形,并且具备频率幅度可调节的特点。在本文中,我们介绍了如何使用Quartus II 9.1平台和Verilog HDL语言编程,来实现这种设备的设计。希望这篇文章能够为电子工程师、数字电路设计师以及学习数字电路的人提供一些参考和帮助。

相关代码,程序地址:http://lanzouw.top/667517182905.html