- 1Go 在STM32MP157C 上跑起来!_golang stm32

- 2Python简化远程部署和系统管理的工具库之fabric使用详解

- 3NOC2023软件创意编程(学而思赛道)python小高组决赛真题_小学高年段 python noc试题

- 4深入探究 HTTP 简化:httplib 库介绍

- 5【angular-基础教程】属性指令NgStyle

- 6方便又好用,必须吹爆这几个良心工具!

- 7scrapy框架爬取网站图片_scrapy框架使用beautifulsoup爬取图片

- 8AI+智慧培训机构视频监控方案

- 9云原生向量数据库Milvus知识大全,看完这篇就够了[基本概念、系统架构、主要组件、应用场景]_faiss、chromadb、es、milvus

- 10ros2+在Ubuntu上安装gazebo_gz-harmonic和gazebo的关系

ASIC设计流程简介

赞

踩

今天小编为大家介绍一下ASIC芯片的设计流程。

ASIC(Application Specific Integrated Circuit)即专用集成电路,是指应特定用户要求和特定电子系统的需要而设计、制造的集成电路。

1. ASIC设计流程

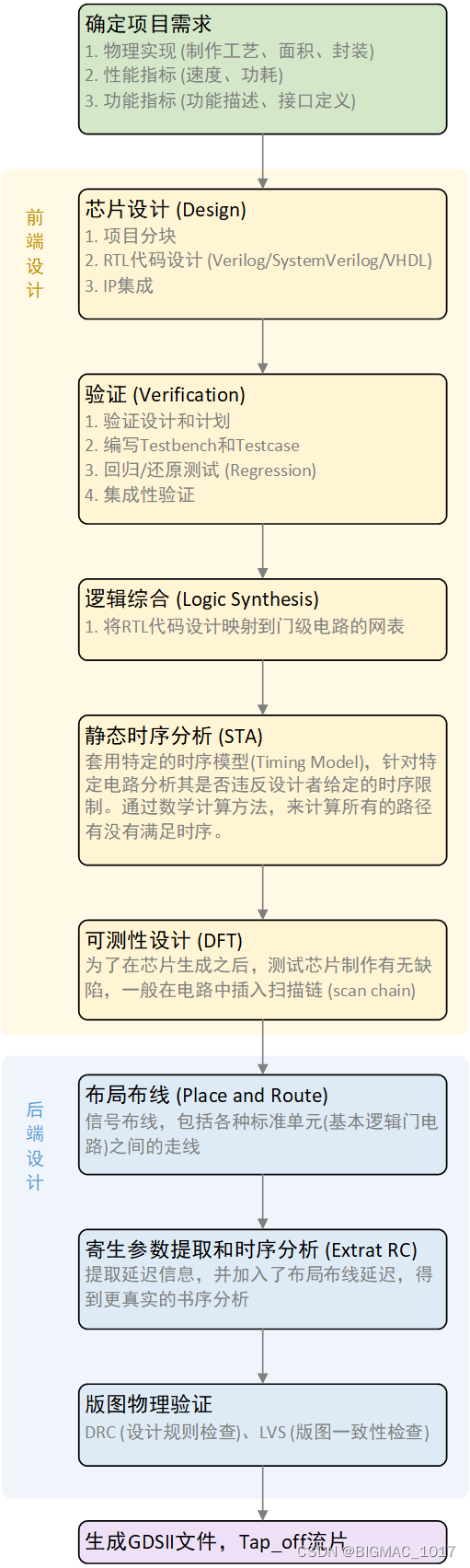

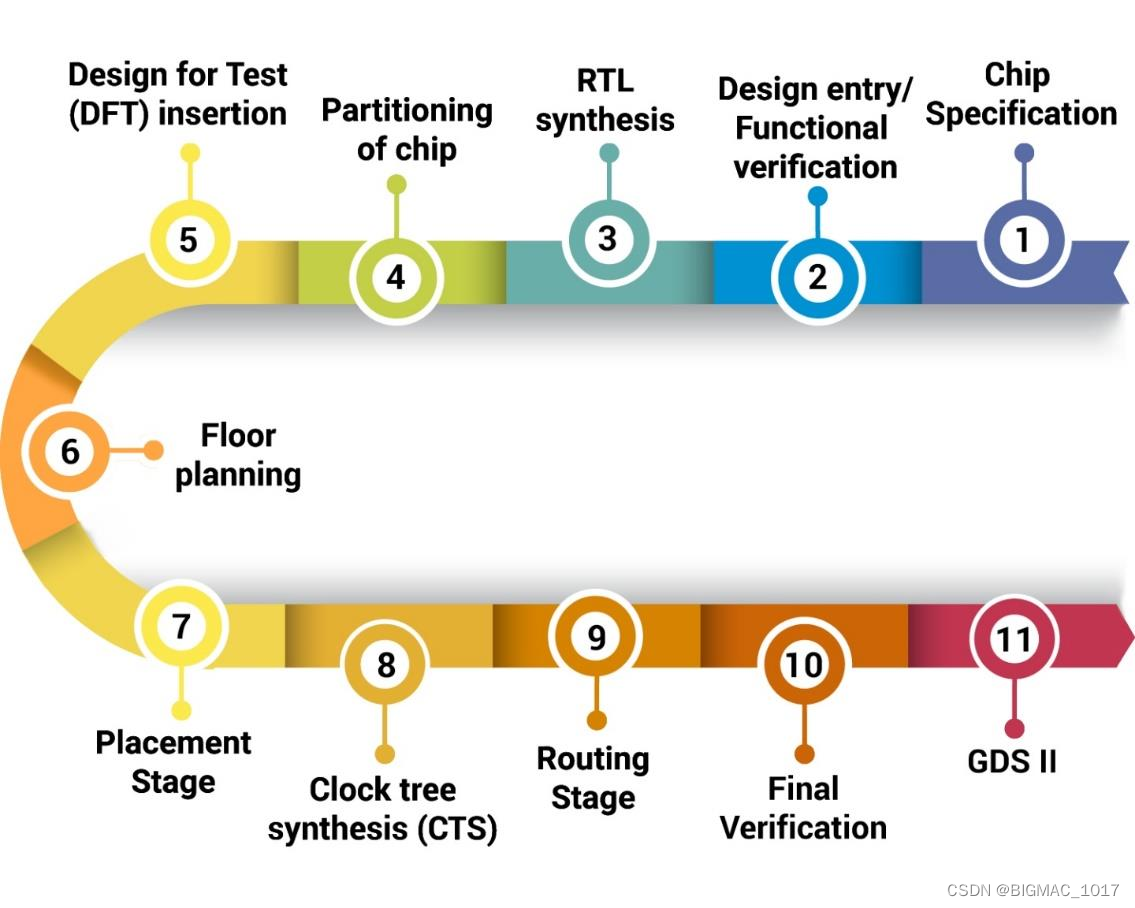

ASIC的设计流程大致如下图所示:

(1) RTL(Register Transfer Level)设计:利用硬件描述语言,对电路以寄存器之间的传输为基础进行描述。

(2) 验证:在功能上确保每一步设计与实现的流程转换时,能保证它的逻辑正确。

(3) 逻辑综合:将RTL级设计中所得的程序代码翻译成实际电路的各种元器件以及他们之间的连接关系,可以用一张表来表示,称为门级网表(Netlist)。门级网表也是一个标准的Verilog语言,比RTL层级更低。

(4) STA (Static Timing Analysis):套用特定的时序模型(Timing Model),针对特定电路分析其是否违反设计者给定的时序限制(Timing Constraint)。

(5) DFT (Design for Test):可测性设计,为了在芯片生产之后测试芯片的良率,看制作有无缺陷,一般是在电路中插入扫描链(scan chain)。

(6) 布局布线 (Place and Route):就是普通信号布线了,包括各种标准单元(基本逻辑门电路)之间的走线。比如我们平常听到的90nm工艺,实际上就是这里金属布线可以达到的最小宽度,从微观上看就是MOS管的沟通长度。

(7) Extrat RC 和 STA:前面综合后的STA用的是一个理想时序模型去做的,这个实际上并没有实际的时序信息。实际CELL摆在哪里,两个CELL之间的走线延时等信息都是没有的,因为这个时候还没有布局布线,两个的位置都是不确定的,自然没有这些信息。当位置确定后,才会真正的去提取这些延时信息,然后再做布局布线之后真正的时钟走线,时钟路径的延时也是更真实的。如果布局布线之后还有不满足时序的地方,也会退回去前面的阶段进行修改。

(8) 版图物理验证:对完成布线的物理版图进行功能和时序上的验证。验证的项目比较多,如LVS (Layout Vs Schematic)验证,版图与逻辑综合后的门级电路图的对比验证;DRC (Design Rule Checking),设计规则检查,检查连线间距,连线宽度等是否满足工艺要求;ERC (Electrical Rule Checking),电气规则检查,检查短路和开路等电气规则违例;等等。实际的后端流程还包括电路功耗分析,以及随着制造工艺不断进步产生的DFM (可制造性设计)问题。物理版图验证完成也就是整个芯片设计阶段完成,下面的就是芯片制造了。

(9) 物理版图以GDSII的文件格式交给芯片代工厂,芯片代工厂在晶圆硅片上做出实际的电路,再进行封装和测试,就得到了实际的芯片。

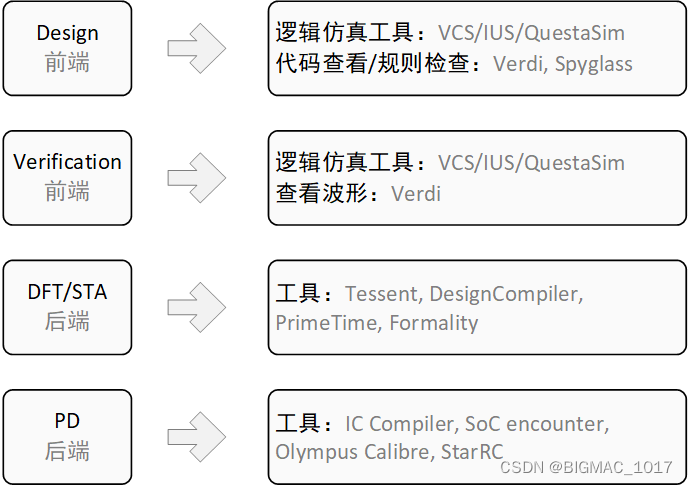

2.设计各阶段使用到的工具

如果大家对我们的文章感兴趣,可以关注我们的公众号:“FpgaHome”,实时关注我们的更新动态。