- 1如何做好一名前端Leader_如果你是某项目前端团队的负责人,你将如何开展工作?

- 22020,智能货柜的现状与未来_智能称重柜在智能货柜整体销量中有多少占比

- 3Android 开发中的SSL pinning_ssl pinning 抓包

- 4基于python的拍卖系统_一个完整的拍卖系统

- 5GitHub Pages + Hexo搭建个人博客网站,史上最全教程_github pages +hexo

- 6Mac下常用命令_mac常用命令

- 7ChatGPT:让论文写作不再是难题

- 8mysql设置账号只能访问某些表,某些字段的权限_授予用户修改字段的权限

- 9大话设计模式——单例模式_c# 单例模式 大话设计模式

- 10这 11 款最佳 Linux 发行版深受 Ubuntu 爱好者喜欢!_哪个linux发行版好用

适用于异构芯片(CPU,ASIC,DSP,FPGA,GPU/GPGPU)的软件并行技术_由 dsp 与 fpga 向 gpu 升级阶

赞

踩

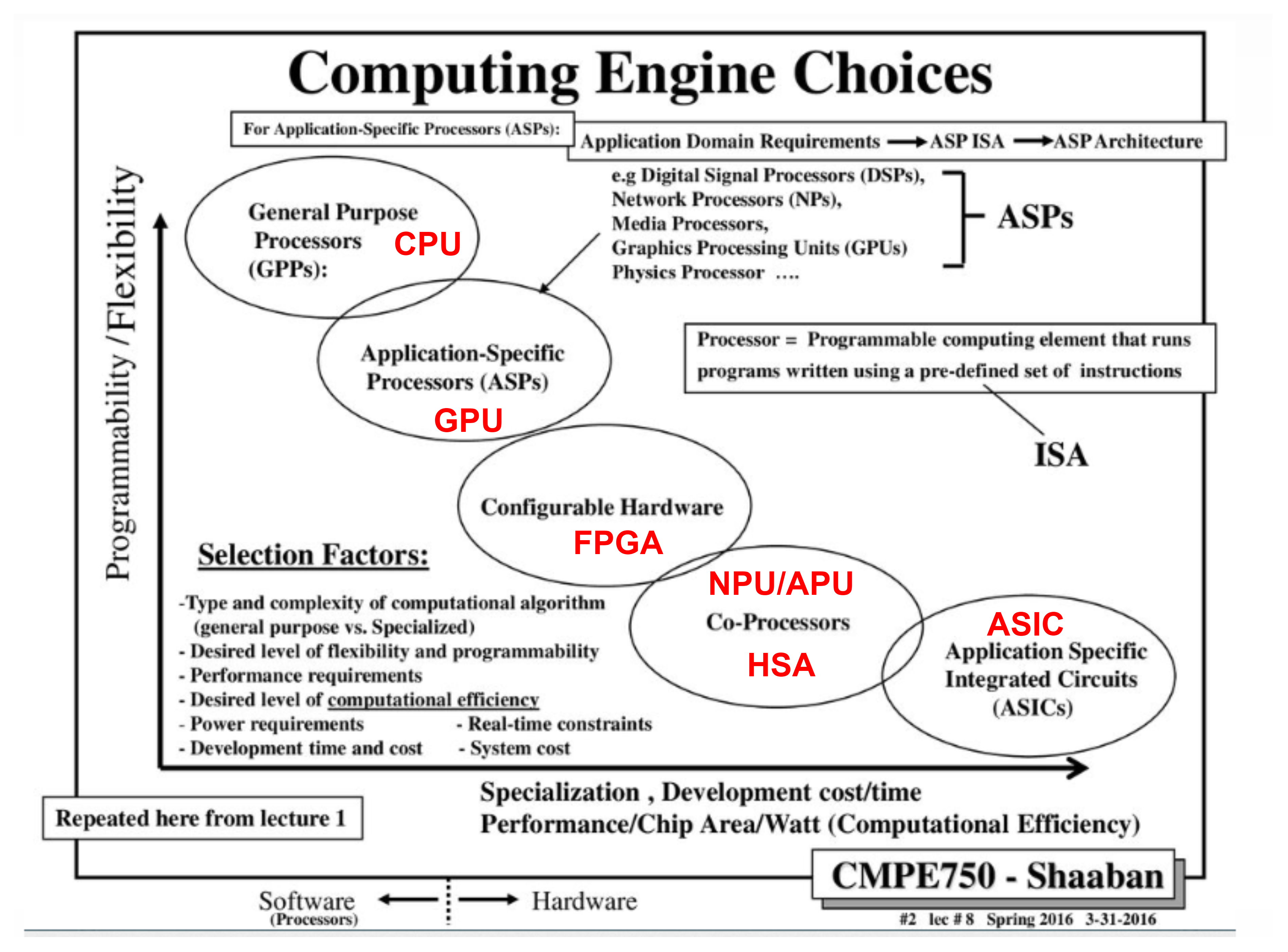

近些年,CPU等通用处理器的性能提升速度放缓,为了继续满足各行各业对高能效计算日益增长的需求,以FPGA,GPU,DSP,NPU等为代表的异构算例,一夜之间在众多的新型热点领域受到广泛关注。

首先结合市面上能够看到的具体的产品来分析这些异构核之间的差异。

多元化算力

除了上述比较通用的命名,还有一些公司为了强调某些方面的差异性,提出了不同的命名,比如VIP的PPU(Parallel Processing Unit)。条条大路通罗马,最终这些命名都强调了异构计算的一个明显特点----并行处理的特性,这一点和GPU,FPGA等类似的。

当前几种典型的计算机体系结构

以计算为中心还是以数据为中心。传统CPU是计算为中心,CPU是由指令流(程序)来驱动运行的,然后CPU作为一切的“主管”再驱动外围的GPU、其他加速模块、IO模块运行。而在超异构的DPU系统中,由于数据处理带宽性能的影响,必须是以数据为中心,靠数据驱动计算。

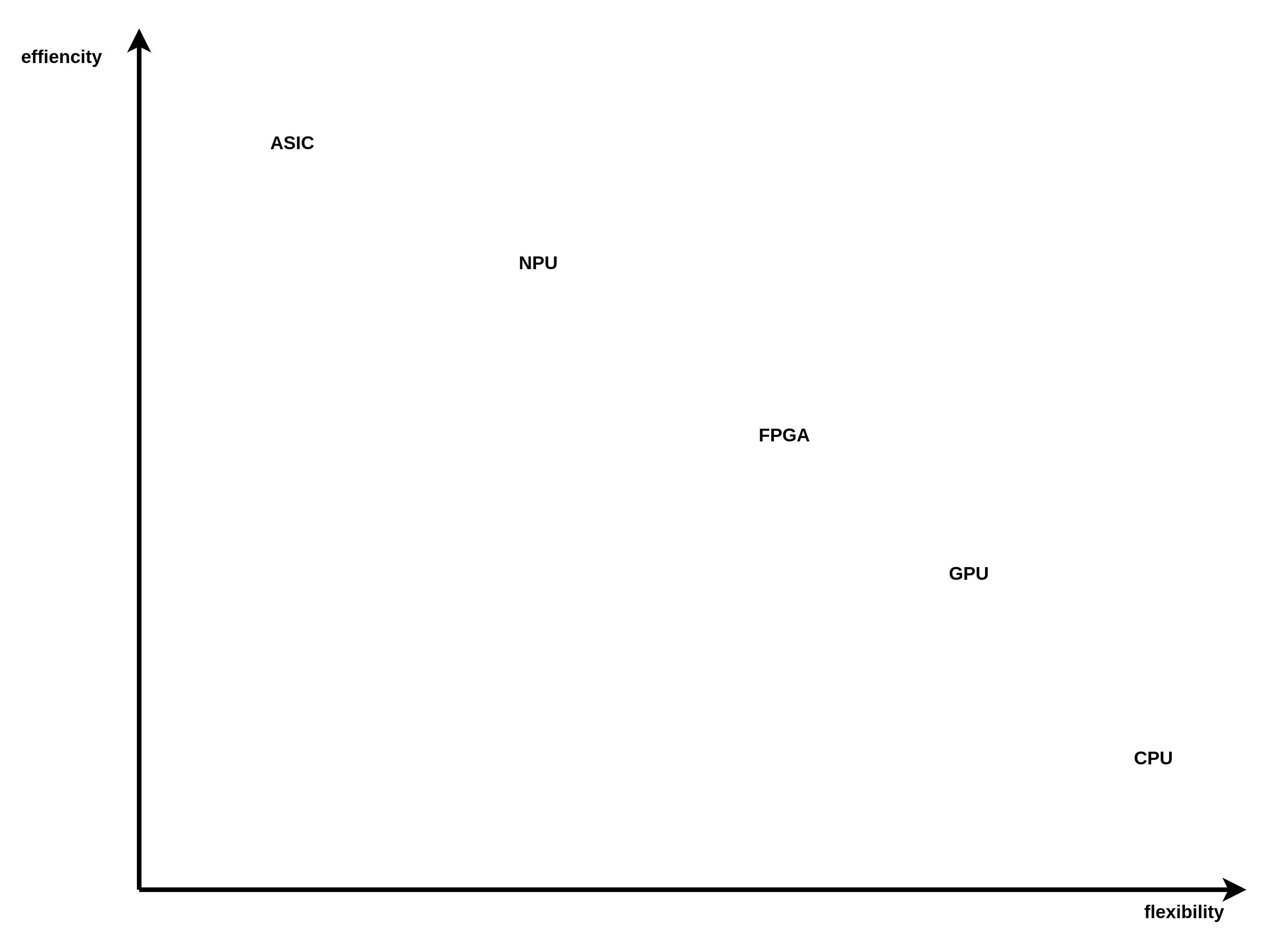

DSA的难以落地,使得行业不得不进行回调,GPGPU越来越多的受到重视。GPGPU的性能,比CPU好,比DSA差;其灵活可编程能力,比DSA好,比CPU差。GPGPU能平衡好性能和灵活性,是一个相对均衡的处理器平台。但是,选择GPGPU只是逃避的问题,并没有本质的解决问题。GPGPU虽然相比CPU性能要好,但受限于架构的原因,也即将在未来3-5年达到性能瓶颈。而上层软件对算力的需求永无止境,这个问题如何本质解决。

从冯诺依曼机以来,计算机体系结构设计重点关注在两个方面,能效和通用性,能效是指单位功耗内能做多少运算,通用性是指能覆盖多大的应用面。

体系结构研究有两个极端,专门定制的芯片ASIC和通用处理器CPU,ASIC的能效非常高,超过通用CPU多个数量级,但ASIC芯片通常只能支持一个特定的算法,而通用CPU理论上能够完成所有可计算的任务,但是能效非常小。这里面的主要原因是,CPU为了满足通用性,采用了非常繁重复杂的指令流水线,功能部件和缓存,运算器只占不到%10的芯片面积。而GPU的能效比比CPU高10-100倍,同时具有一定的通用性,CPU和GPU的算力可驾驭能力要强于ASIC。

NPU牺牲一定的灵活性,换来了对比GPU和CPU更高的性能比。

软件代表灵活性和低性能,硬件代表死板和高性能,矛盾双方互补,对立统一。

CPU,GPU,FPGA可以做成图灵完备的,自身具备取指执行的功能,可以作为系统的调度中心。

CPU、GPU 都属于冯·诺依曼结构,指令译码执行、共享内存。冯氏结构中,由于执行单元(如 CPU 核)可能执行任意指令,就需要有指令存储器、译码器、各种指令的运算器、分支跳转处理逻辑。由于指令流的控制逻辑复杂,不可能有太多条独立的指令流,因此 GPU 使用 SIMD(单指令流多数据流)来让多个执行单元以同样的步调处理不同的数据,CPU 也支持 SIMD 指令,但SIMD指令的支持只能算是CPU的一个锦上添花的功能,不构成CPU的主要功能,比如X86的SSE,MIPS/RISCV的向量指令,以及ARM 的NEON,都是CPU的可配置功能。

FPGA 之所以比 CPU 甚至 GPU 能效高,本质上是无指令、无需共享内存的体系结构带来的福利, FPGA 每个逻辑单元的功能在重编程(烧写)时就已经确定,不需要指令。

谷歌发布的人工智能芯片:Tensor Processing Unit(TPU),TPU的tensor cores在执行张量,矩阵运算时,更快更有效,因为在机器、深度学习中所处理的数据类型就是张量。TPU兼具了CPU与ASIC的特点,可编程,高效率,低能耗,还有多种多样的各类用于CNN深度学习的NPU,它们也都可以归为ASIC的一种。

虽然有专用的TPU,但一些最新的GPU也包含了许多张量核。

DSP有些类似于CPU,但是它拥有更强的并行计算能力,支持多发射,VLIW指令以及单精度,双精度浮点运算和专门用于SIMD加速的MAC阵列等,使其能耗比远高于CPU。

GPU的峰值性能要高于FPGA,PPA,性能功耗比也要更优一些,FPGA基本单元的计算能力有限。为了实现可重构特性,FPGA 内部有大量极细粒度的基本单元,但是每个单元的计算能力&