热门标签

热门文章

- 1python123题目——特殊数列求和_用户输入一个小于10的正整数n,求1 + 12 + 123 + 1234 + …… 的前n项的和。当

- 2软件测试常用的7种方法,最后一个是升职加薪关键!(零基础小白转行IT互联网高效进阶)_软件测试方法

- 3Mac m1安装AWVS

- 4USB Hub

- 5Data truncation: Incorrect datetime value: ‘0000-00-00 00:00:00.000‘ for column ‘createTime‘ at row

- 6倒计时3天!点击查看openGauss Summit 2023关键词

- 7wazuh4.7利用python脚本发送告警信息到飞书机器人_wazuh 配置告警

- 8python做数据查询系统_[Python实战] 功能简单的数据查询及可视化系统

- 9Golang入门

- 10[MySQL] error 1292 数据类型错误_truncated incorrect double value: 'a

当前位置: article > 正文

ZYNQ AXI4 FDMA内存读写

作者:Cpp五条 | 2024-05-30 07:47:07

赞

踩

ZYNQ AXI4 FDMA内存读写

1 概述

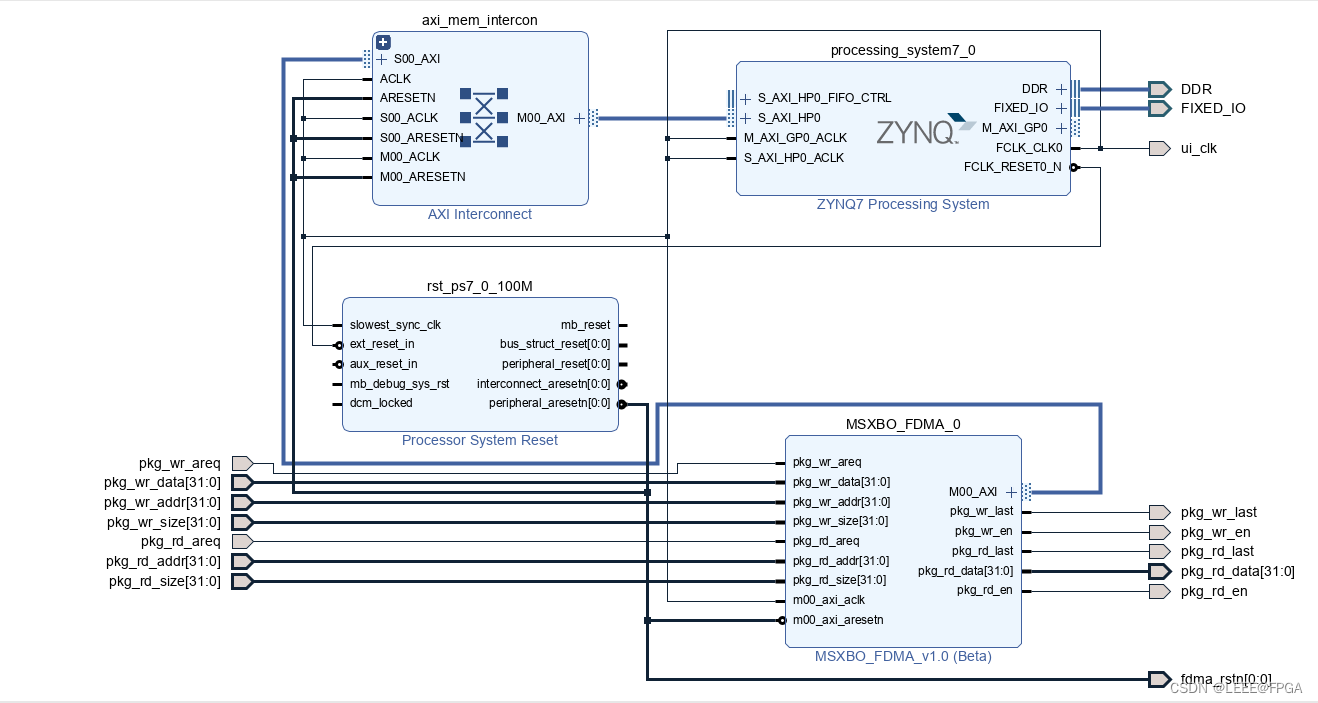

如果用过ZYNQ的都知道,要直接操作PS的DDR 通常是DMA 或者VDMA,然而用过XILINX 的DMA IP

和 VDMA IP,总有一种遗憾,那就是不够灵活,还需要对寄存器配置,真是麻烦。对于我们搞 FPGA

的人来说,最喜欢直接了当,直接用FPGA代码搞定。现在XILINX 的总线接口是AXI4总线,那么熟

练自定义AXI4 IP挂到总线上就非常方便了。基于这个目的,定义了一个基于AXI4 FULL MASTER

的IP,暂且取名为FDMA。

2 硬件搭建

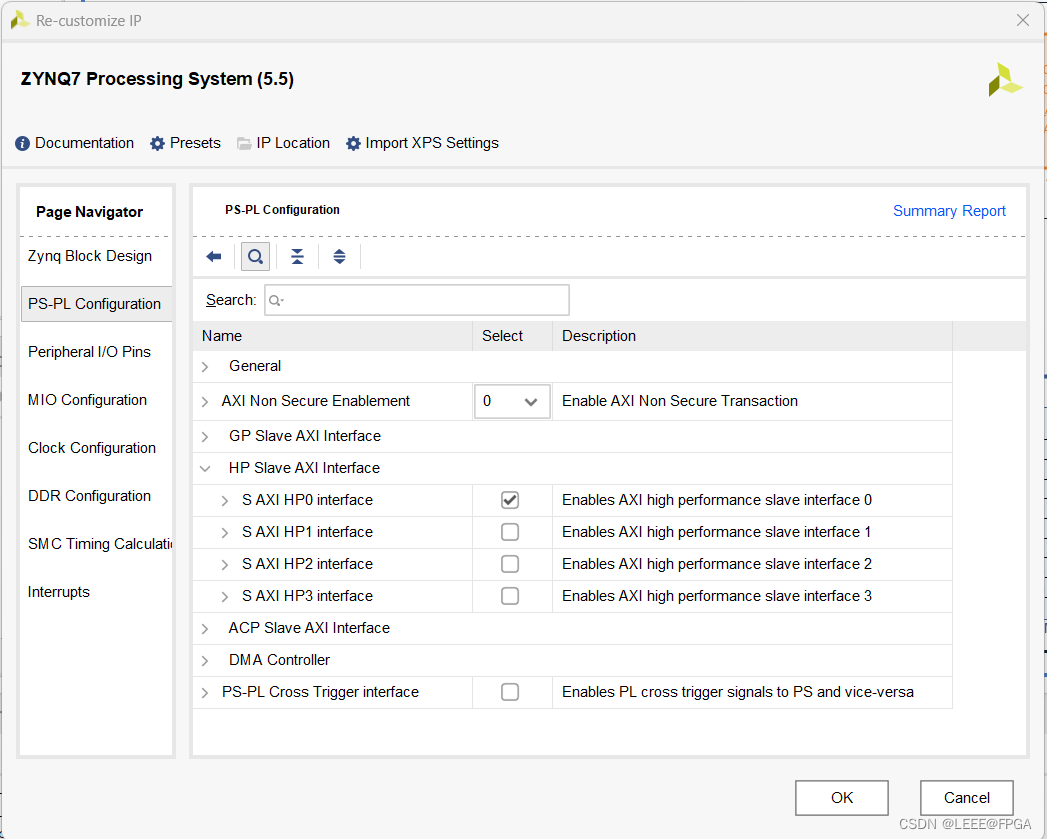

ZYNQ 配置

测试代码:

`timescale 1ns / 1ps

//

// Company:

// Engineer:

//

- 1

- 2

- 3

- 4

- 5

声明:本文内容由网友自发贡献,不代表【wpsshop博客】立场,版权归原作者所有,本站不承担相应法律责任。如您发现有侵权的内容,请联系我们。转载请注明出处:https://www.wpsshop.cn/w/Cpp五条/article/detail/645933

推荐阅读

相关标签