- 1ElasticSearch二进制单点部署_elasticsearch二进制部署

- 2头歌c语言实训项目-数组的使用_头歌第4关:最大数和最小数位置互换

- 3SpaCy 中文模型:助力自然语言处理的新利器

- 4CentOS下离线安装gcc_centos离线安装gcc

- 5FPGA学习-CORDIC算法详解_cordic quartus csdn

- 6【数据结构】顺序表详解_顺序表数据结构

- 7模拟电子技术基础(第四版)教材 电子版_模电课本电子版

- 8制作一个简单HTML个人网页网页(HTML+CSS)源码_个人网页代码

- 9测试用例设计思路_测试用例设计思维

- 10目标检测集 | ECCV 2020 论文大盘点(附论文&代码下载)

还是分不清非阻塞赋值与阻塞赋值吗?_testbench中阻塞和非阻塞有区别吗(3)

赞

踩

时序电路的时钟信号就如同这个节奏“一、二”一样,每当时钟的上升沿或者下降沿到来时,便会对电路的输入进行采样,然后根据逻辑关系进行对应的输出。而当时钟边沿没有到来的时候,则电路的输出保持在上一个状态不变。

为了实现这一特性,也会有一些小小的要求。

- 输入信号必须在时钟上升沿到来之前的一段时间内就保持稳定,因为在电路采样期间你输入信号不能左右横跳

- 同样的,在电路完成采样后的一段时间内,输入信号也必须保持稳定,也不能左右横跳影响下一个周期的信号采样

这两个时间就是触发器的建立时间和**保持时间,**触发器正常工作需要满足建立时间和保持时间的时序要求。

- 建立时间(Tsu:set up time):是指在触发器的时钟信号上升沿到来以前,数据稳定不变的时间,如果建立时间不够,数据将不能在这个时钟上升沿被稳定的打入触发器,Tsu就是指这个最小的稳定时间

- 保持时间(Th:hold time):是指在触发器的时钟信号上升沿到来以后,数据稳定不变的时间,如果保持时间不够,数据同样不能被稳定的打入触发器,Th就是指这个最小的保持时间

时序逻辑的核心就是触发器,触发器的输出不是瞬变的,而是需要一定的时间。这个参数就是触发器的**数据输出延时(Clock-to-Output Delay)----Tco,**这个时间指的是当时钟有效沿变化后,数据从输入端到输出端的最小时间间隔。

比如在10ns处,时钟上升沿到来,此时触发器输入采样值为1。由于Tco的存在,这个值1可能要在11ns处才会出现在触发器的输出端。了解这一点很重要,是后面搞懂非阻塞赋值与阻塞赋值区别的前提条件。

赋值区别

首先直接上结论:

- 时序逻辑电路用非阻塞赋值(<=)

- 组合逻辑电路用阻塞赋值(=)

阻塞赋值就是直接连线,其映射到具体电路,就是指定一个具体导向的wire,即线网;而非阻塞赋值就是触发器,映射到具体电路就是一个reg。根本就不需要管这两个赋值的名字,只要想想你到底要实现一个什么电路就行了。

下面是阻塞赋值的例子:

module test(

input clk,

input [1:0]din,

output reg [1:0]a,

output reg [1:0]b

);

always @(*)begin

a = din;

b = a;

end

endmodule

- 1

- 2

- 3

- 4

- 5

- 6

- 7

- 8

- 9

- 10

- 11

- 12

- 13

看到这里,你可能会想阻塞赋值是顺序执行的,也就是先执行这一句: a = din;然后才是: b = a。所以会把din的值赋给a,然后再把a的值赋给b。就好像第一句的结果会影响第二句的赋值一样,所以被称为阻塞赋值。

这个道理是没问题的,但是看起来非常的绕。如果把这个module直接映射到电路,你会发现这三个变量,根本就是三条总线互相连到了一起,如下:

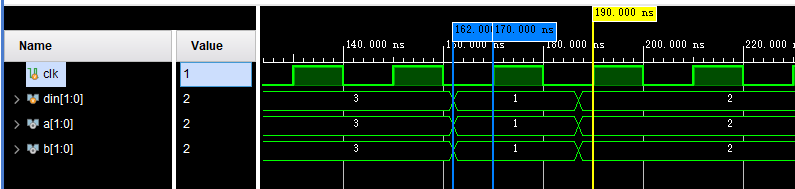

所以其结果就是,当输入din发生变化时,会立马同步到输出a、b。可以写一个简单的testbench验证一下:

`timescale 1ns/1ns module test_tb(); reg clk; reg [1:0]din; wire [1:0]a,b; initial begin din = 0; clk = 0; end always #({$random}%100) din = {$random}%4; //随机赋值0~3 always #10 clk = ~clk; test tb( .clk(clk), .din(din), .a(a), .b(b) ); endmodule

- 1

- 2

- 3

- 4

- 5

- 6

- 7

- 8

- 9

- 10

- 11

- 12

- 13

- 14

- 15

- 16

- 17

- 18

- 19

- 20

- 21

- 22

- 23

- 24

可以看到,输入、输出的变化是实时同步的,这也是组合逻辑的特点。

- 162ns:din=1;a=1;b=1;

- 170ns:din=1;a=1;b=1;

- 190ns:din=2;a=2;b=2;

下面是非阻塞赋值的例子:

module test(

input clk,

input [1:0]din,

output reg [1:0]a,

output reg [1:0]b

);

always @(posedge clk)begin

a <= din;

b <= a;

end

endmodule

- 1

- 2

- 3

- 4

- 5

- 6

- 7

- 8

- 9

- 10

- 11

- 12

- 13

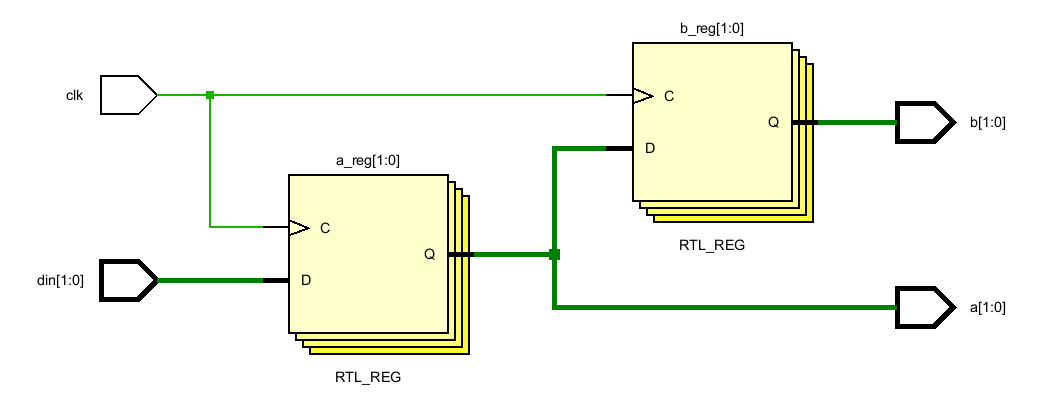

非阻塞赋值就是生成时序逻辑,输出a、b分别生成了2组2位宽的reg。其电路综合结果如下:

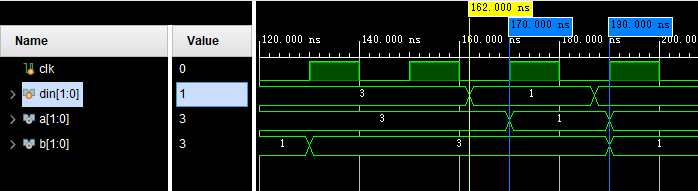

同样使用上面的testbench进行仿真,仿真结果如下:

- 162ns:din=1;a=3;b=3;

- 170ns:din=1;a=1;b=3;

上面的仿真结果中,寄存器的输出就是瞬发的,这与实际不符。比如在170ns的采样出,din的值为1,则输出a应该在一定的时间后(Tco)才会变为1,信号b同理。

为了更好地理解阻塞赋值的特性,我们可以调用时序仿真,或者简单地改一下RTL,模拟Tco(假设其值为1ns):

module test( input clk,    **既有适合小白学习的零基础资料,也有适合3年以上经验的小伙伴深入学习提升的进阶课程,涵盖了95%以上大数据知识点,真正体系化!** **由于文件比较多,这里只是将部分目录截图出来,全套包含大厂面经、学习笔记、源码讲义、实战项目、大纲路线、讲解视频,并且后续会持续更新** **[需要这份系统化资料的朋友,可以戳这里获取](https://bbs.csdn.net/topics/618545628)** 以上经验的小伙伴深入学习提升的进阶课程,涵盖了95%以上大数据知识点,真正体系化!** **由于文件比较多,这里只是将部分目录截图出来,全套包含大厂面经、学习笔记、源码讲义、实战项目、大纲路线、讲解视频,并且后续会持续更新** **[需要这份系统化资料的朋友,可以戳这里获取](https://bbs.csdn.net/topics/618545628)**

- 1

- 2

- 3

- 4

- 5

- 6

- 7

- 8

- 9

- 10

- 11

- 12

- 13

- 14

- 15

- 16

- 17

- 18

- 19

- 20