热门标签

热门文章

- 1事业单位【6】_正常儿童一时专注于一种或两种事情是常见的现象,比如学某部广告片里面的叮当声,或

- 2Jetson_yolov8_解决模型导出.engine遇到的问题、使用gpu版本的torch和torchvision、INT8 FP16量化加快推理_yolov8转engine

- 3基于STM32的数据采集+心率检测仪(二)_stn 32 a dc读取心率

- 4【人人都是算法专家】一文搞定AI算法竞赛(全网最详细)_ai+程序算法竞赛

- 5大数据大厂面试题_csdn hbase hive hdfs yarn spark相关面试题

- 6数组的应用_zmud 数组应用

- 7自注意力机制:深度解析与前沿探讨_自注意力机制的基本原理

- 8torch.nn模块

- 9论文笔记(11):文献翻译+想法记录:A Survey on Visual Transformer

- 10小红书API接口测试 | 小红书笔记详情 API 接口测试指南_小红书接口文档

当前位置: article > 正文

verilog阻塞和非阻塞语法

作者:Cpp五条 | 2024-06-14 18:14:55

赞

踩

verilog阻塞和非阻塞语法

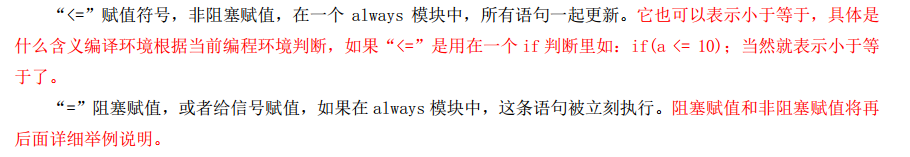

阻塞和非阻塞是FPGA硬件编程中需要了解的一个概念,绝大部分时候,因为非阻塞的方式更加符合时序逻辑设计的思想,有利于时钟和信号的同步,更加有利于时序收敛,所以除非特殊情况,尽量采用非阻塞方式。

1,非阻塞代码

非阻塞赋值,A和B是同时被赋值的,具体是说在时钟的上升沿来的时刻,A和B (或调换A和B)同时被置1。

always @(posedge clk)

begin

A <= 1'b1;

B <= 1'b1;

end

- module unblock

- (

- input clk_i, input rst_n_i, output [4:0]result_o, output [3:0]A, output [3:0]B

- );

- reg [3:0]A;

- reg [3:0]B;

- reg [4:0]result_o;

- always @(posedge clk_i )

- begin

- if(!rst_n_i)

- begin

- A <= 4'd0;

- B <= 4'd0;

- result_o = 5'd0;

- end

- else

- begin

- A <= 4'd2;

- B <= B + 1'b1;

- result_o <= A + B + 1'b1;

- end

- end

- endmodule

仿真

第一个周期上升沿后: A 输出 2 这是个常量; B 输出 1

声明:本文内容由网友自发贡献,不代表【wpsshop博客】立场,版权归原作者所有,本站不承担相应法律责任。如您发现有侵权的内容,请联系我们。转载请注明出处:https://www.wpsshop.cn/w/Cpp五条/article/detail/719077

推荐阅读

相关标签