热门标签

热门文章

- 1客制化机械键盘改键软件VIA介绍_via改键是什么意思

- 2FlinkJob提交和参数配置_jobmanager.rpc.address

- 3git clone --depth 1 --branch branch/tag_name remoteurl_turn off this advice by setting config variable ad

- 4SpringCloud和Dubbo比较_springcloud和dubbo协议相比

- 5OpenPLC文献翻译_openplc是完全开源的吗

- 62020 Vue 基于Element-UI开发 常用模板使用 【整理】_element ui作业模板

- 7启动kafka报错ERROR Fatal error during KafkaServer startup. Prepare to shutdown ,找到原因就要可以解决

- 8为什么编译原理被称为龙书?

- 9Mint Ubuntu 使用 docker compose 创建容器

- 10Git之拉取指定tag版本/切换指定tag代码_git clone 指定tag

当前位置: article > 正文

基于FPGA的光纤通信系统设计_fpga光纤设计方案

作者:Gausst松鼠会 | 2024-04-13 02:56:14

赞

踩

fpga光纤设计方案

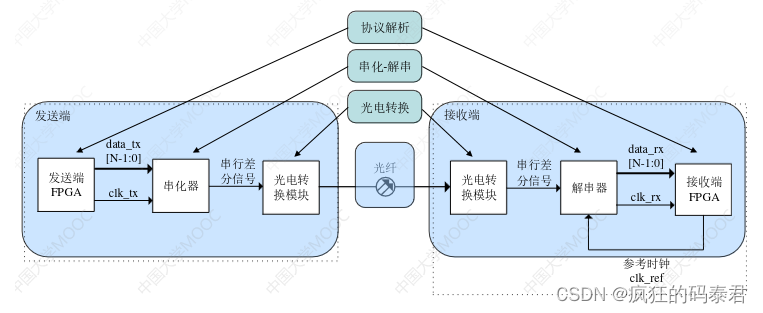

光纤通信系统的组成

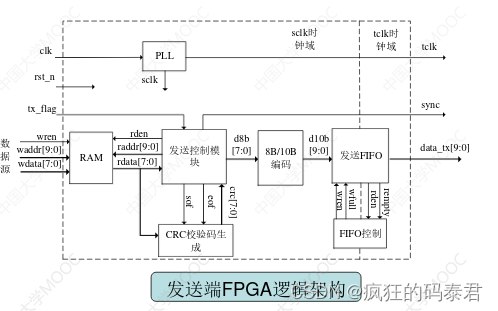

发送端FPGA

发送控制逻辑、数据编码、校验码生成、缓存控制、时钟控制

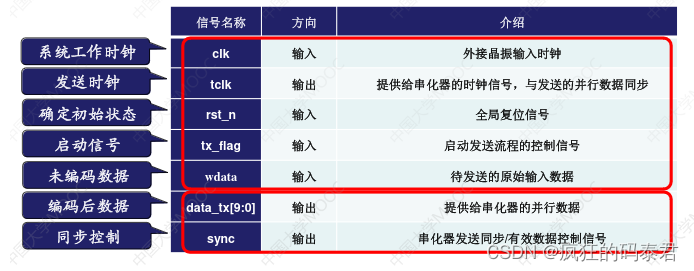

端口定义

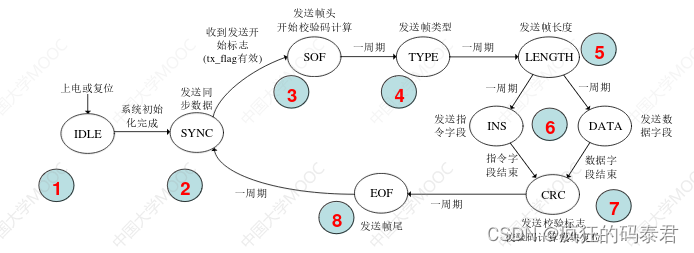

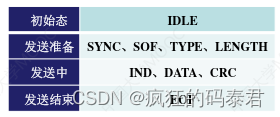

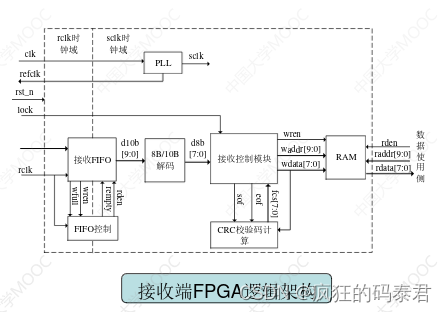

状态机设计

代码示例

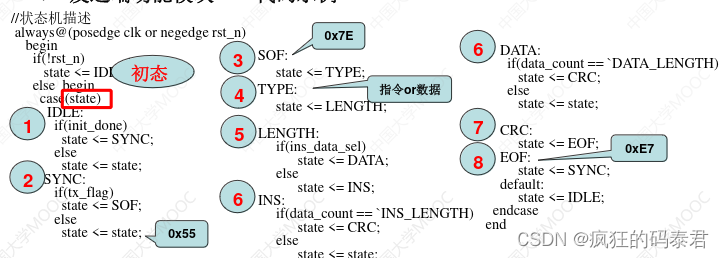

接收端功能模块

接收端控制逻辑、数据解码、检验计算、缓存控制、时钟控制

端口定义

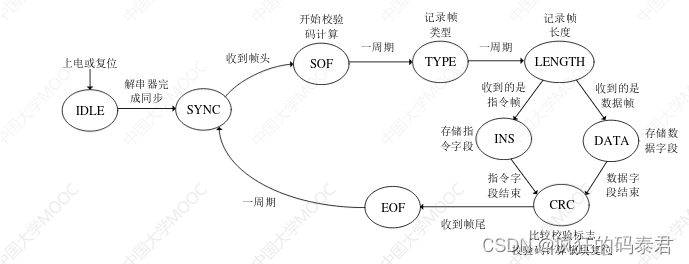

状态机设计

声明:本文内容由网友自发贡献,不代表【wpsshop博客】立场,版权归原作者所有,本站不承担相应法律责任。如您发现有侵权的内容,请联系我们。转载请注明出处:https://www.wpsshop.cn/w/Gausst松鼠会/article/detail/414035

推荐阅读

相关标签