- 1备战第15届蓝桥杯的同学注意了!蓝桥算法双周赛开始了!_第十五届蓝桥杯青少年

- 2git命令之fetch_your branch is up to date with 'origin/dev'.

- 3PyTorch小技巧:使用Hook可视化网络层激活(各层输出)

- 4【机器学习-周志华】学习笔记-第十二章

- 5大模型微调技术(Adapter-Tuning、Prefix-Tuning、Prompt-Tuning(P-Tuning)、P-Tuning v2、LoRA)_adapter tuning

- 6解决Expected all tensors to be on the same device, but found at least two devices, cuda:0

- 7全面解读:人工智能AI是什么_ai解读

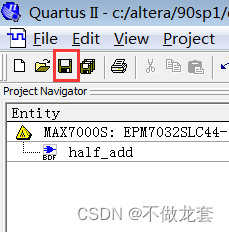

- 8《算法设计与分析》复习

- 9【团队协作开发】从Gitee中克隆项目到IDEA并实现代码更新提交教程(新手)_怎么从gitee上拉取项目到idea

- 10计算机网络基础知识(五)——什么是TCPUDP协议?图文并茂的方式对两大传输层协议进行从头到尾的讲解_什么是tcp/udp协议栈

Quartus-II 9.0版本实现半加器,1位全加器,4位加法器的设计(数字逻辑课程实验1—半加器设计,1位全加器设计,4位加法其设计)_半加器quartus

赞

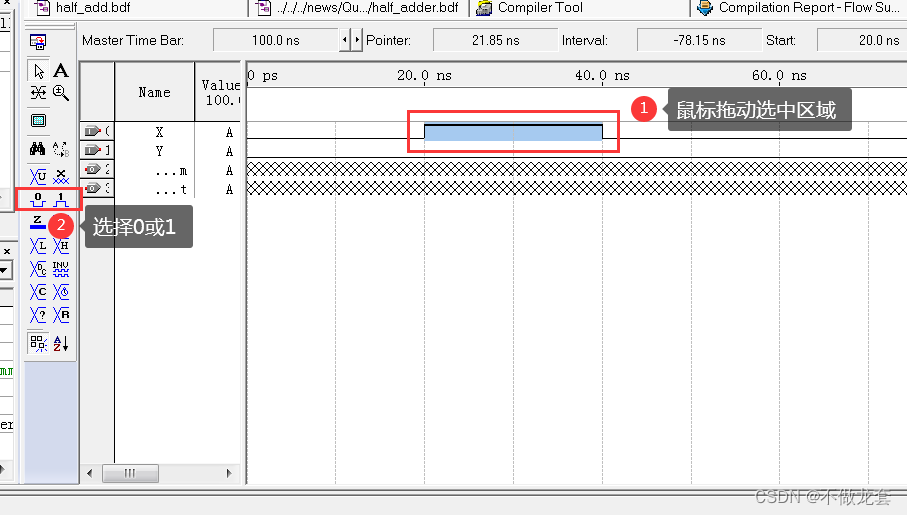

踩

下面的设计均采用Quartus-II 9.0版本实现,包括时序仿真和功能仿真。

目录

一、半加器设计

1.实验原理

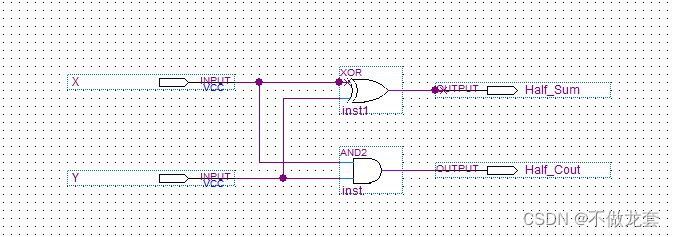

半加器的设计由两个基本逻辑门元件组成,包括与门和逻辑门。

半加器的逻辑表达式:S = A ⊕B; C = A ● B;

就是S等于A异或B,C等于A与B。其中S是和值端口,C是进位端口,A、B是数据输入端口。

半加器真值表:

| A | B | S | C |

|---|---|---|---|

| 0 | 0 | 0 | 0 |

| 0 | 1 | 1 | 0 |

| 1 | 0 | 1 | 0 |

| 1 | 1 | 0 | 1 |

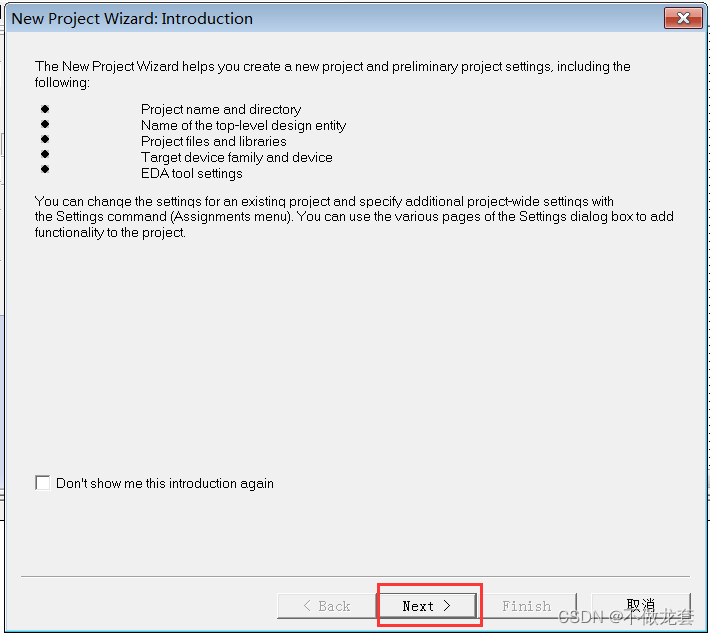

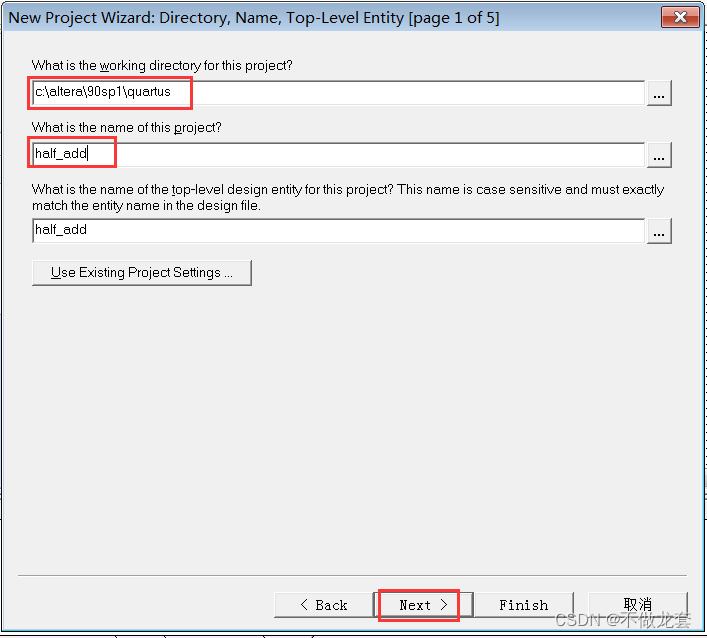

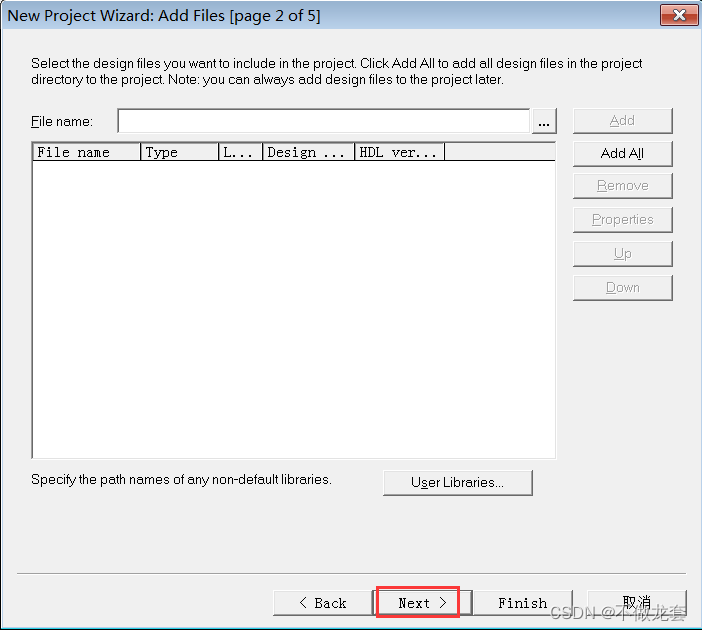

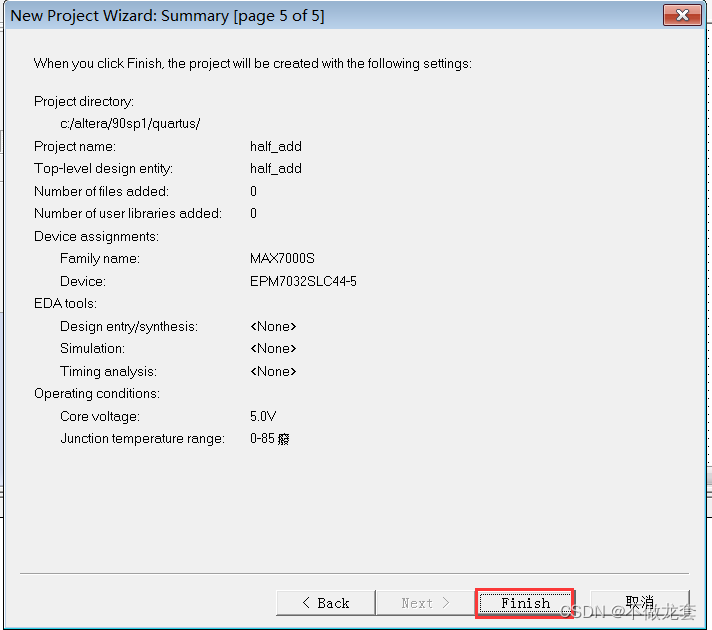

2.Quartus建立工程

(1)打开Quartus软件,开始一个新项目,依次点击File->New Project Wizard->next

(2)选择项目保存位置以及命名,依次点击next

(3)根据设计要求选择相应的芯片类型,继续点击next ,直到Finish

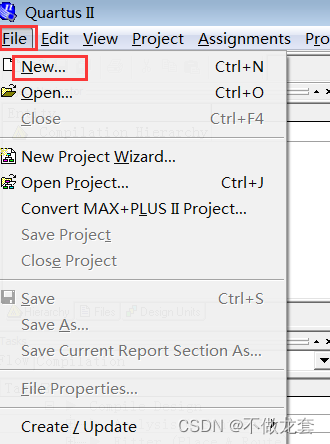

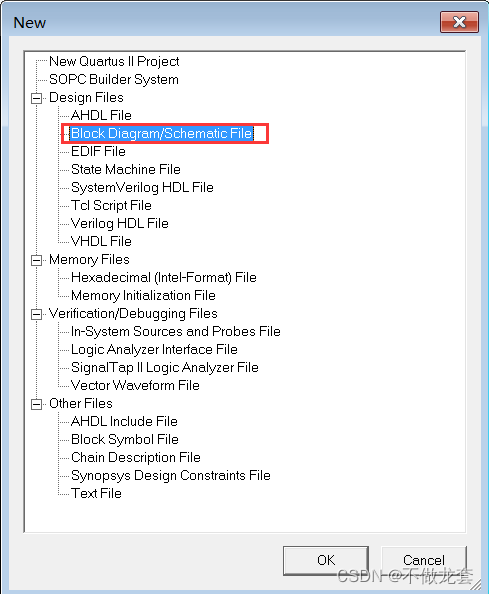

(4)依次点击New->Block Dicgram/Schematic File,进入原理图编辑窗口

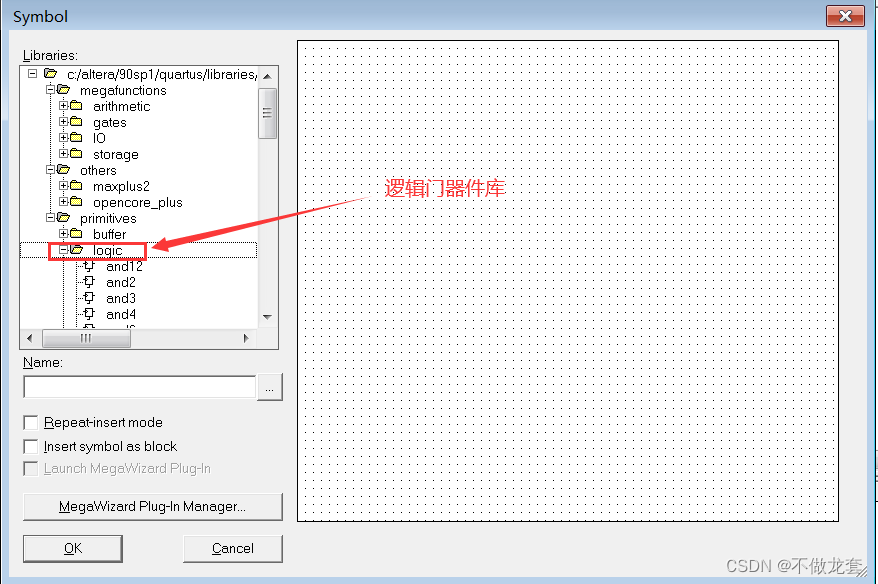

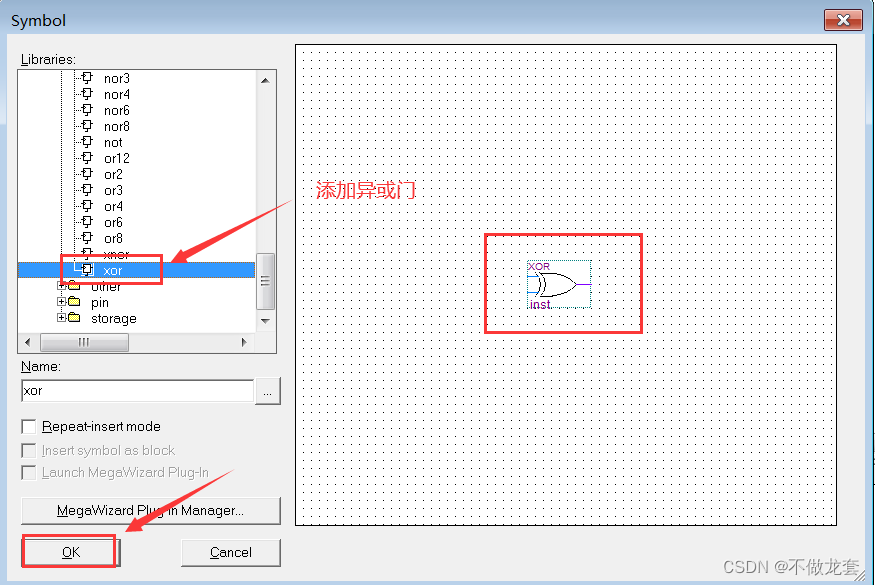

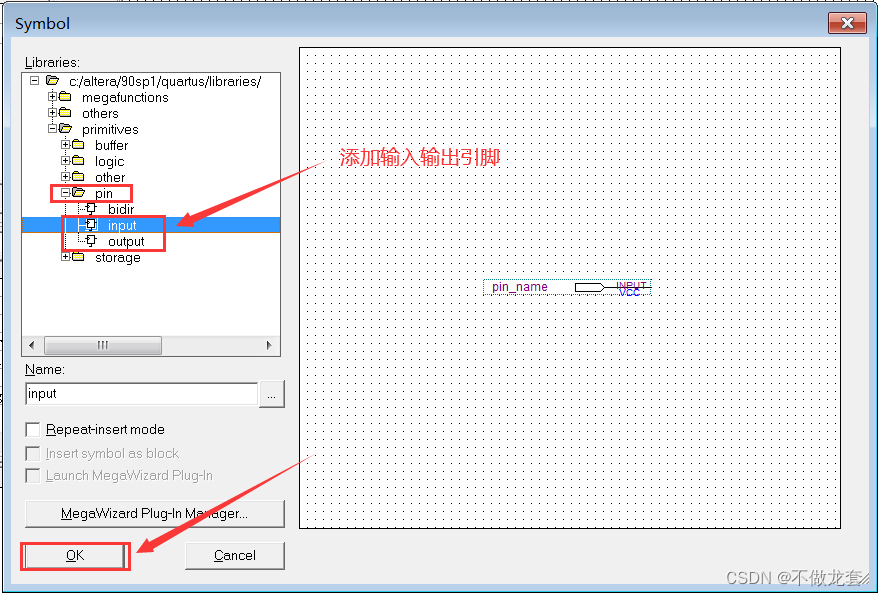

(5)双击原理图编辑窗口,选择相应电路元器件,这里我们依次选择异或门,与门,输入和输出引脚 ,按照设计好的原理图进行设计

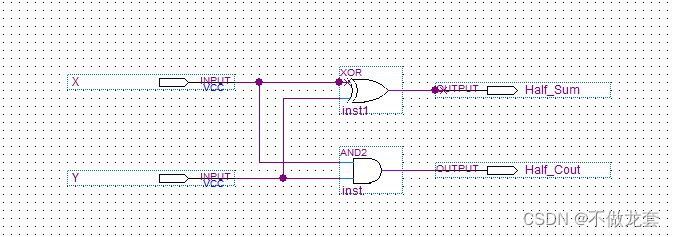

(6)按照设计好的半加器原理图进行设计连线

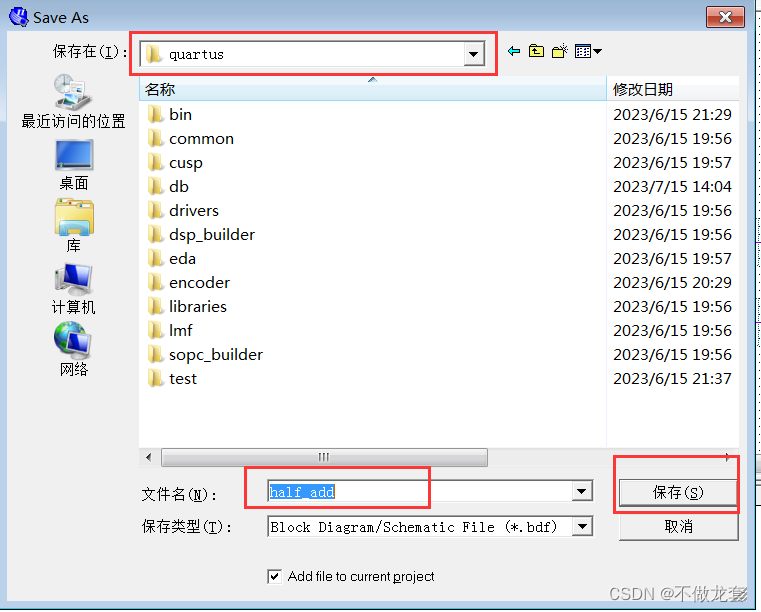

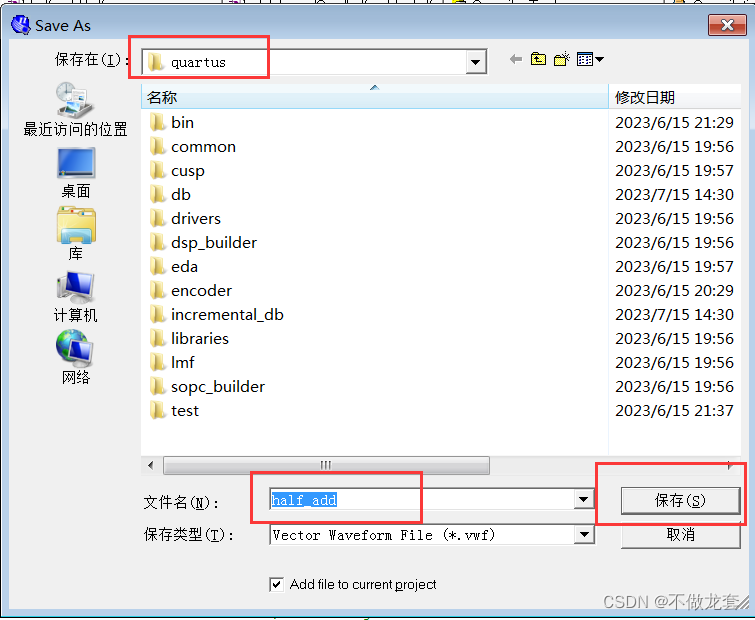

(7)设计完成后保存(这里必须保存,如果你直接用别人已经完成好的文件,则需要另存)

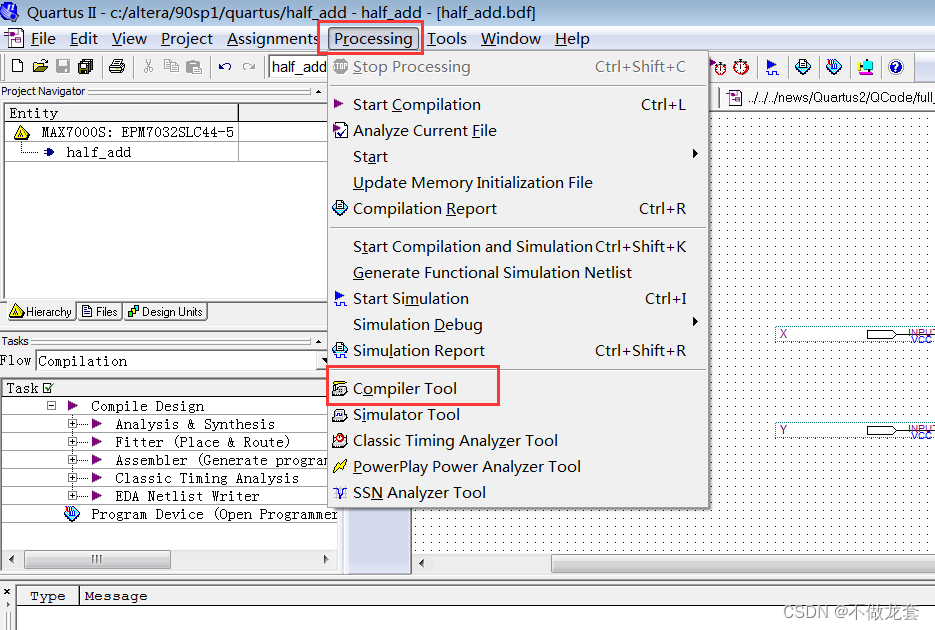

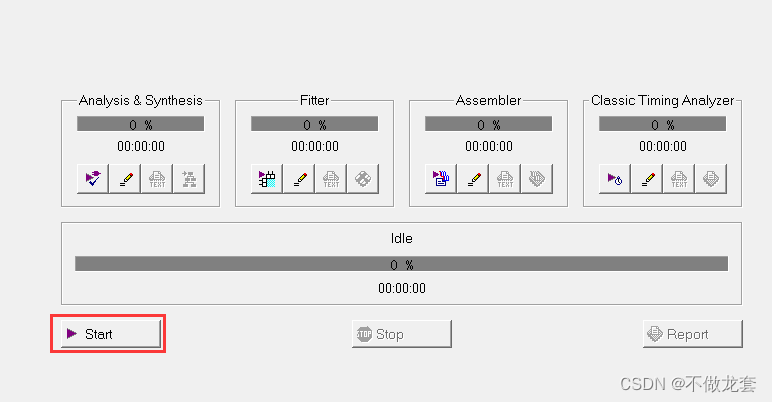

(8)接下来使用编译工具进行编译,依次点击Processing->Compiler Tool->Start

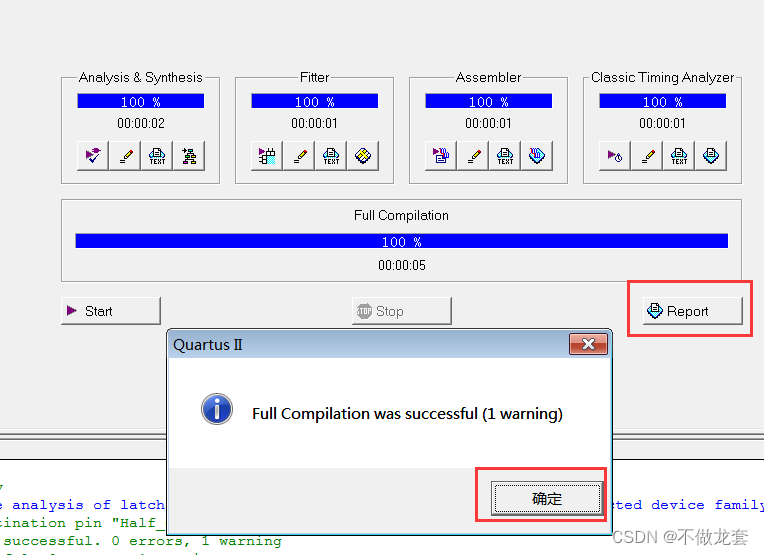

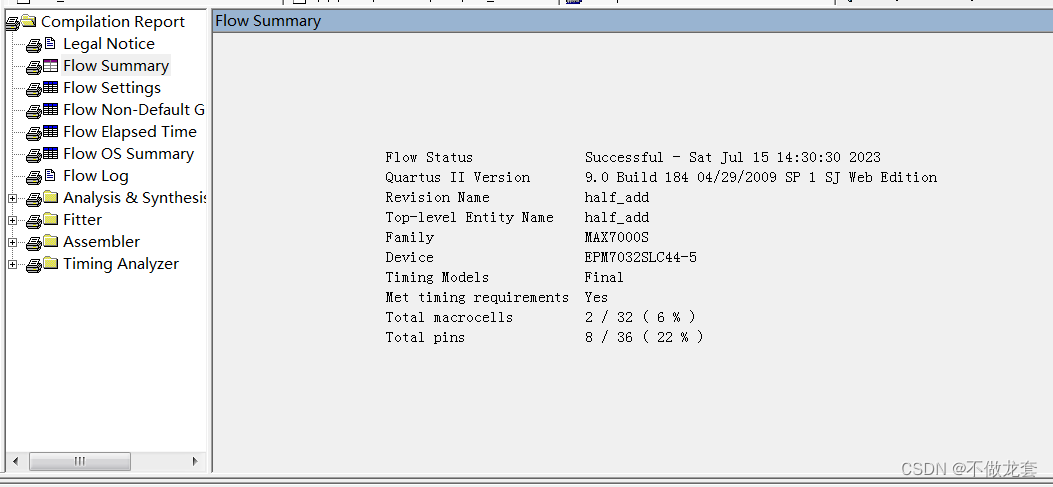

(9)编译成功后得到如下结果

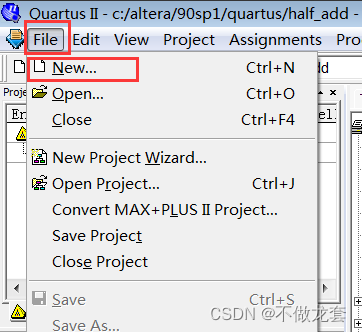

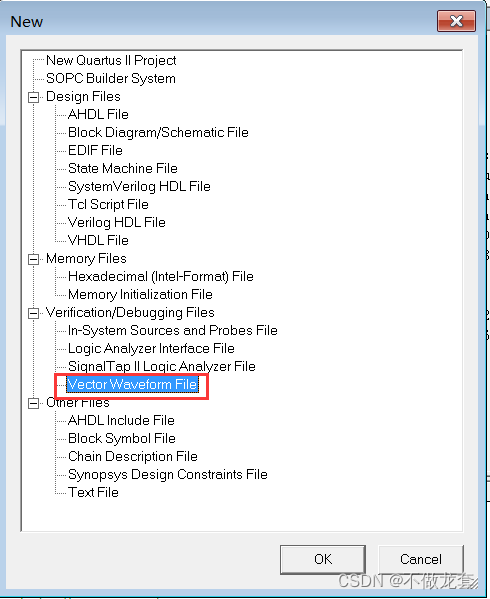

(10)接下来进行网表设计,依次点击File->New->Vector Waveform File,进入网表设计界面

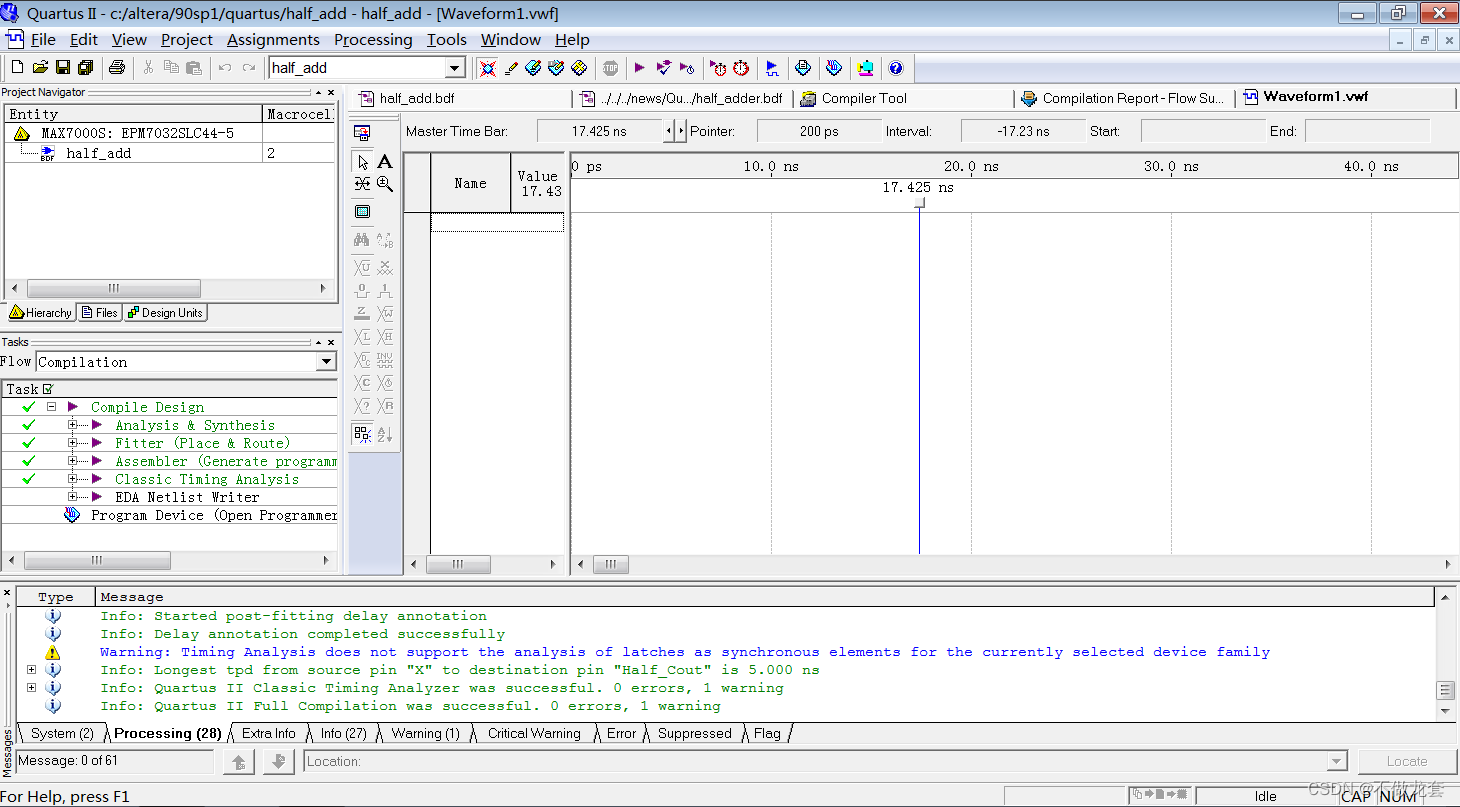

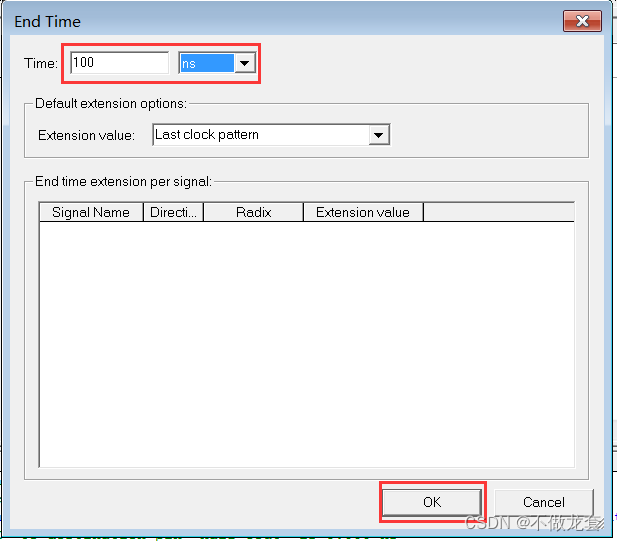

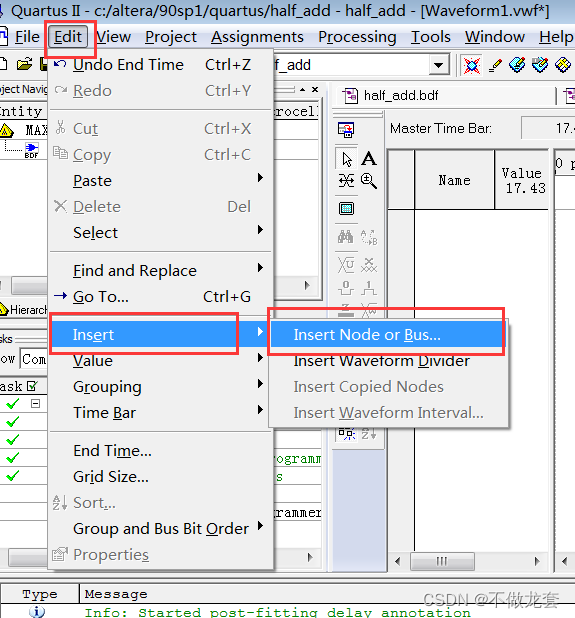

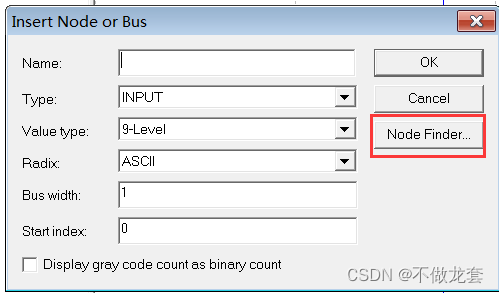

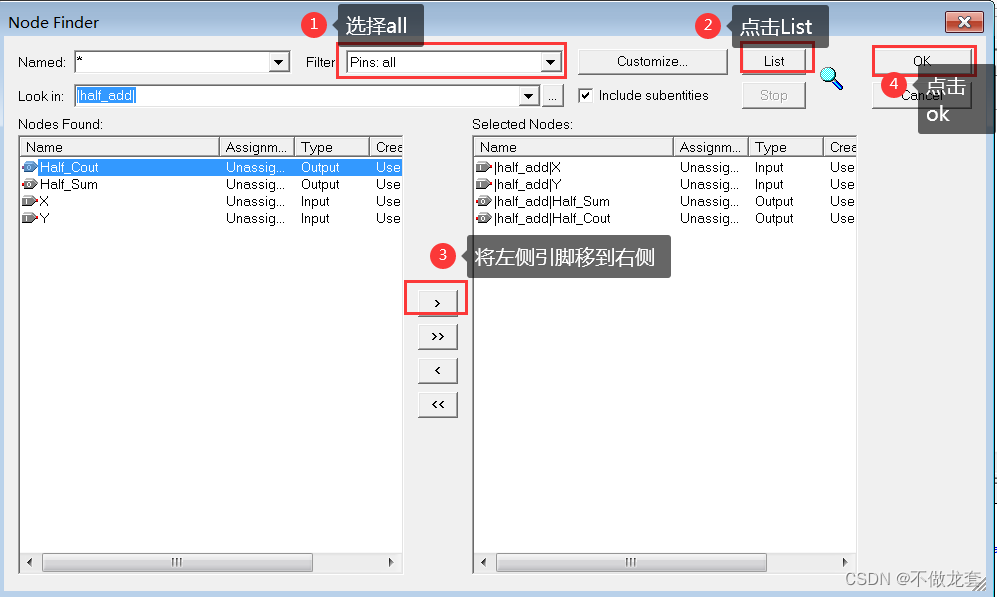

(11)依次选择Edit->End Time设置截止时间,Edit->Insert->Insert Node Bus设置测试向量文件

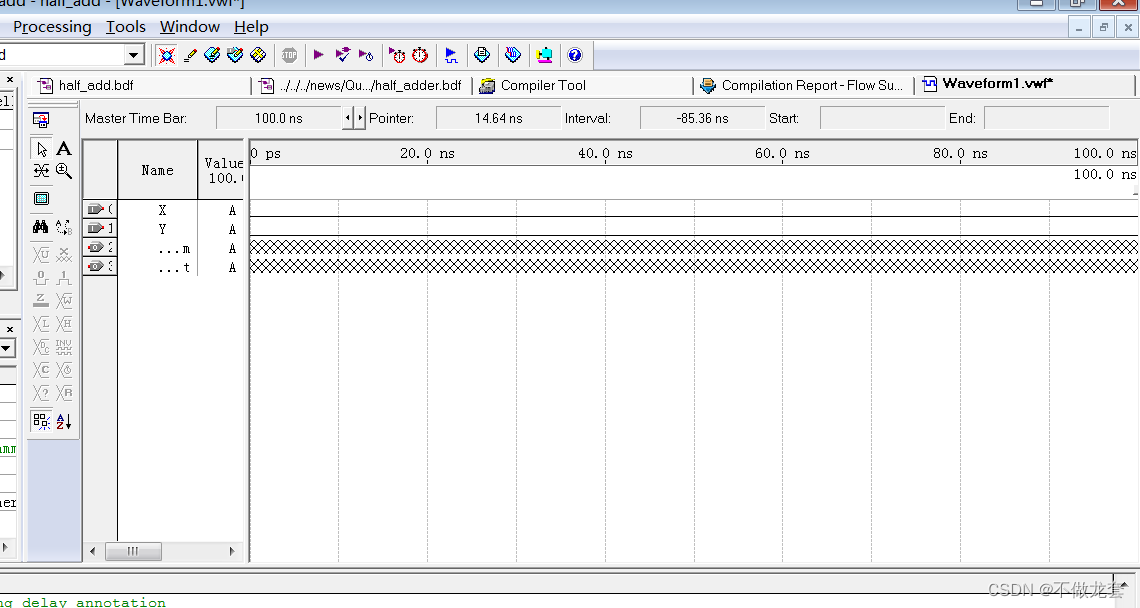

(12)设置输入引脚X,Y激励波形,设置完成后保存(这里也必须保存,与之前文件保存在同一目录下)

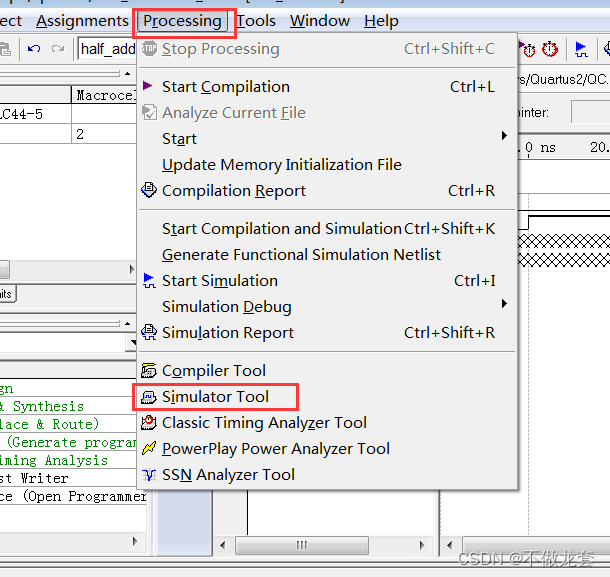

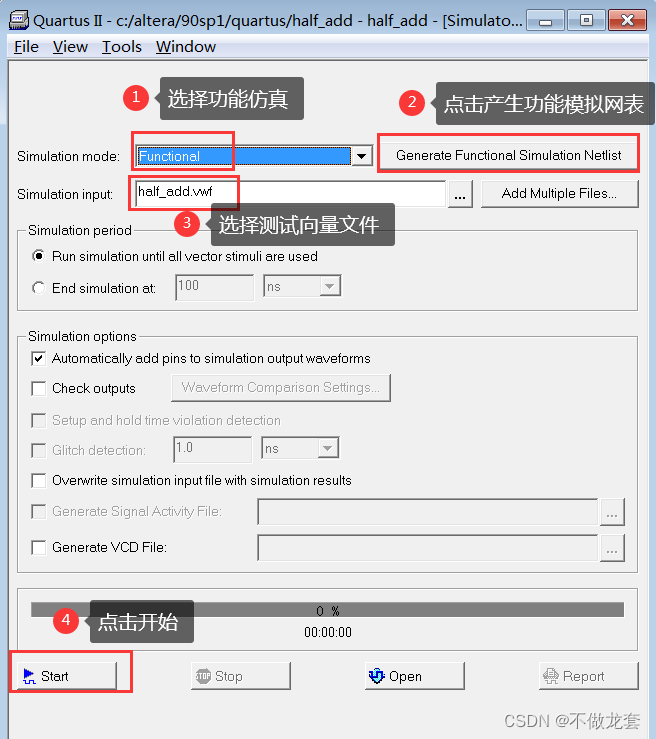

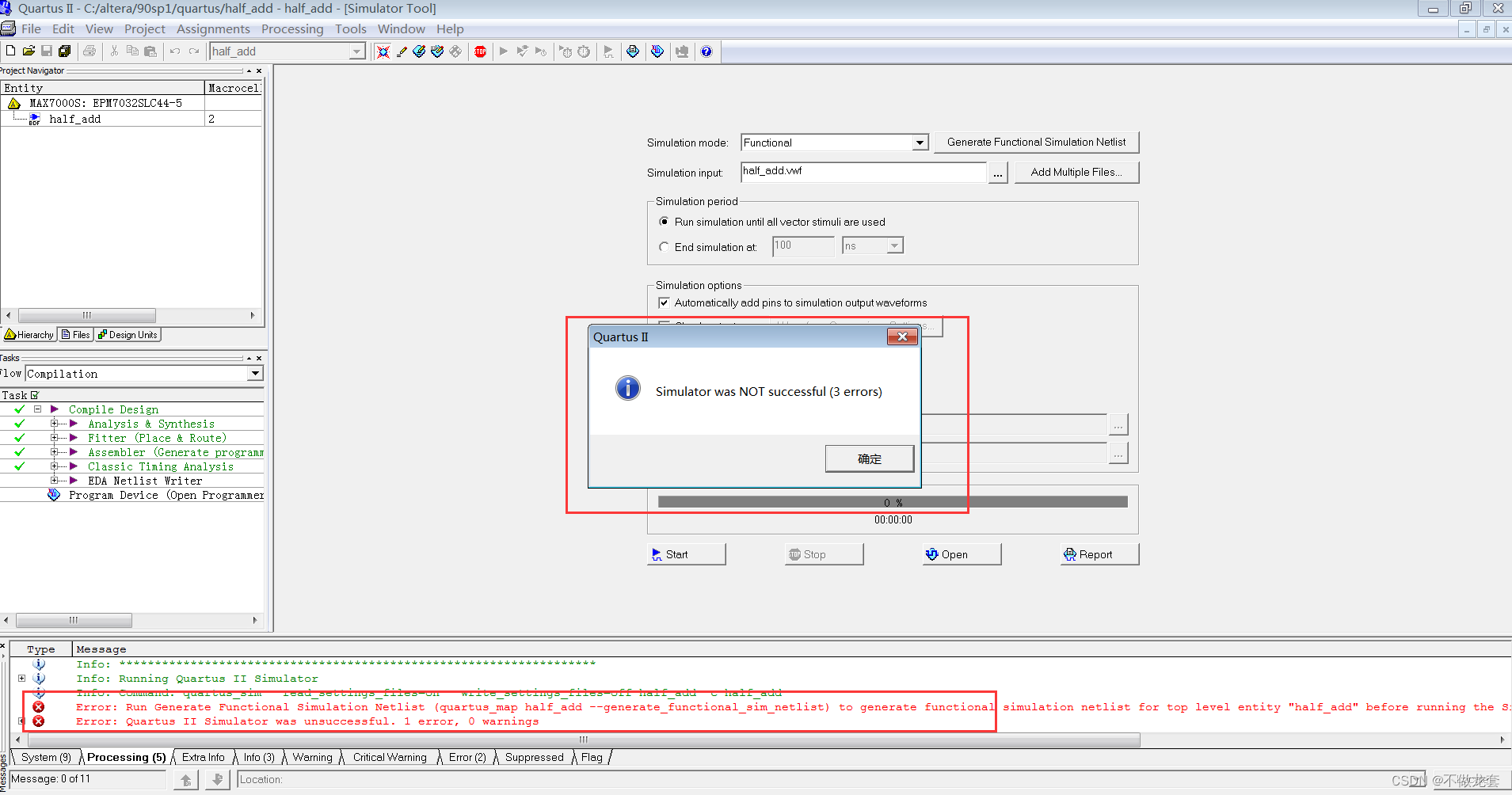

(13)接下来进行功能仿真,依次点击Processing->Simulator Tool,在模拟器窗口中必须点击Generate Functional Simulation Netlist,否则会出现报错

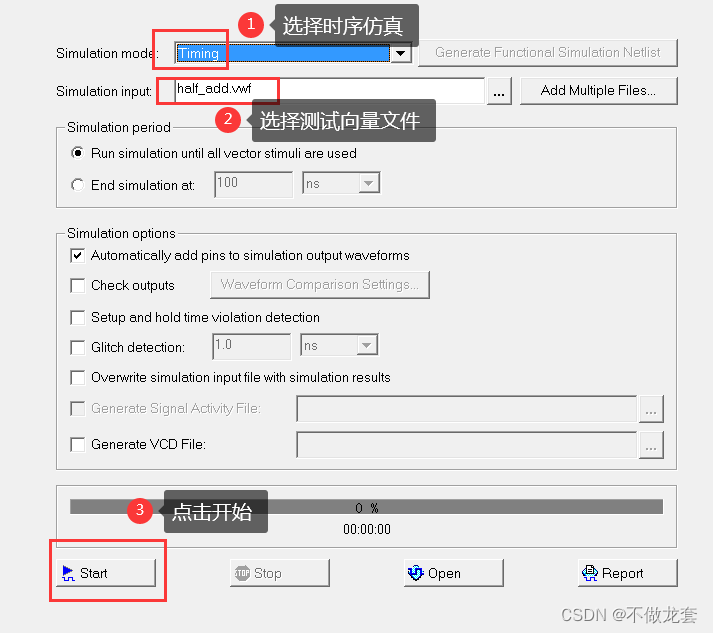

(14)接下来进行时序仿真,依次点击Processing->Simulator Tool

3.实验结果展示

半加器原理图

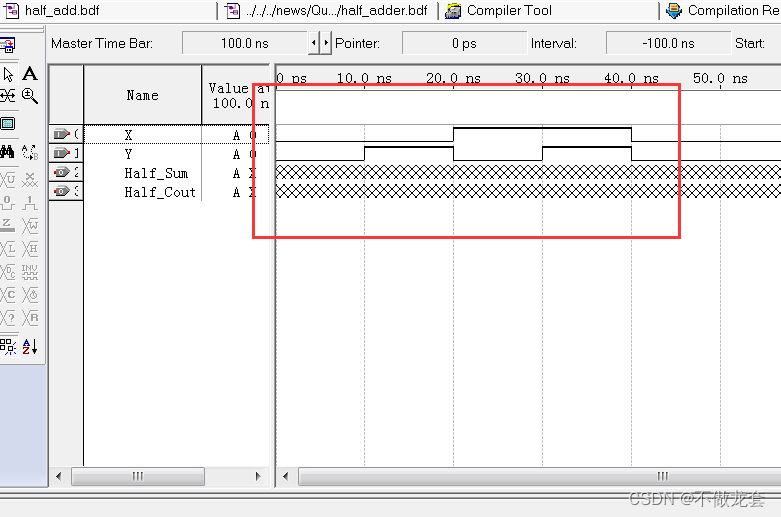

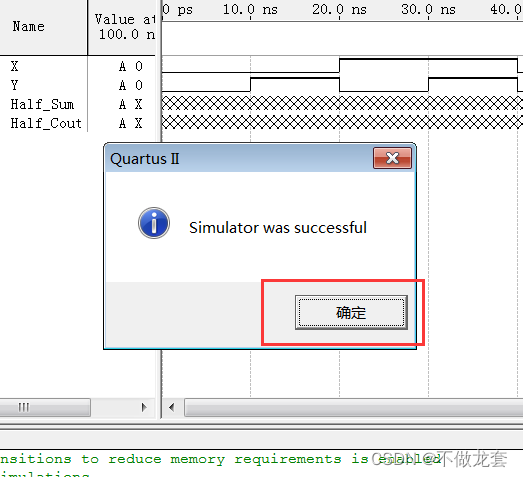

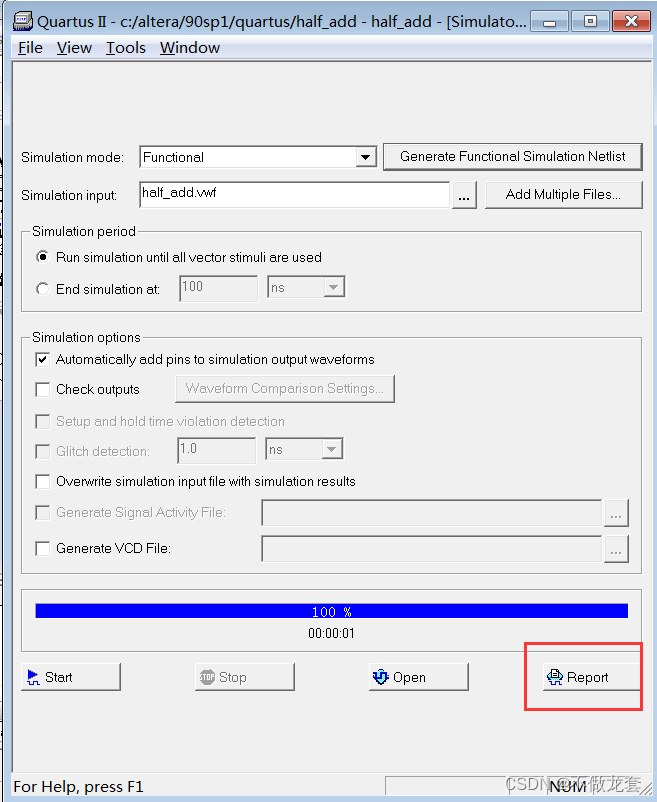

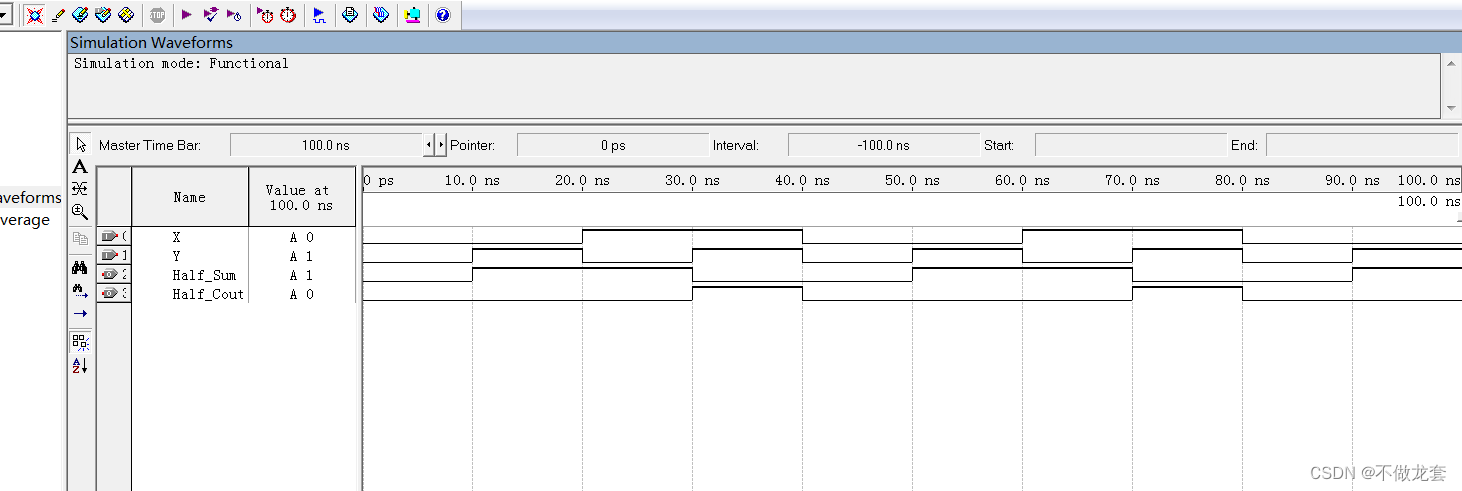

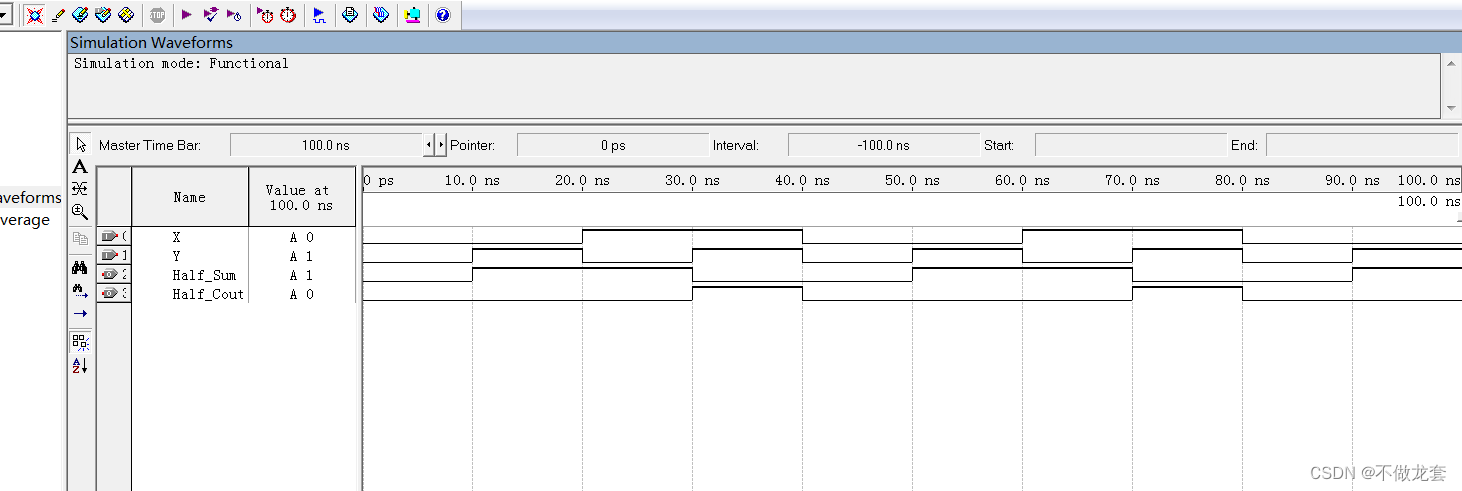

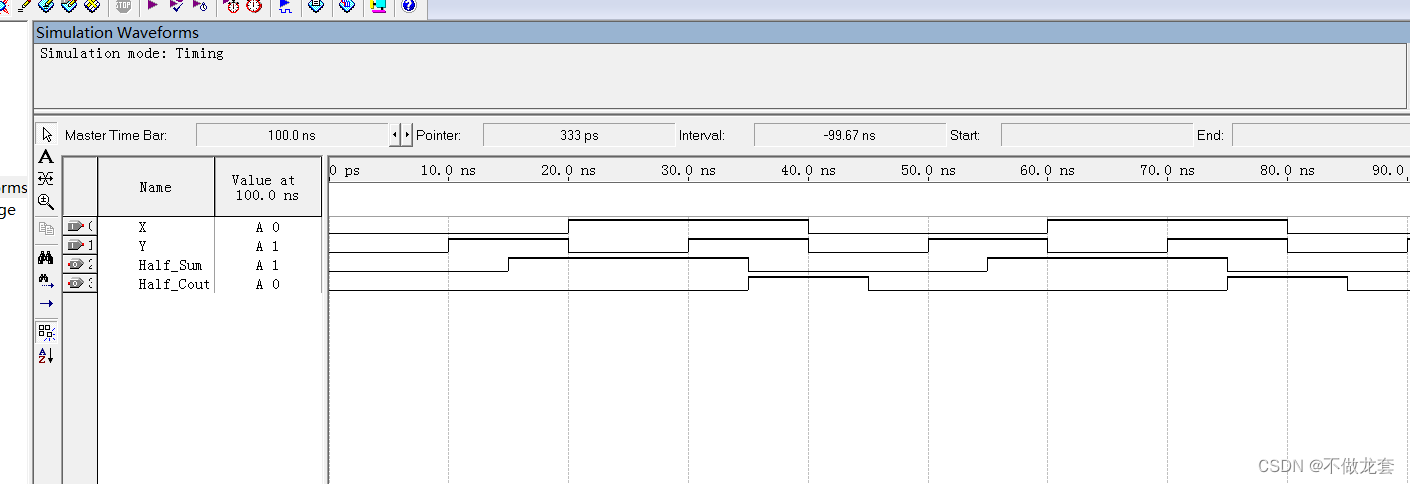

半加器功能仿真结果图

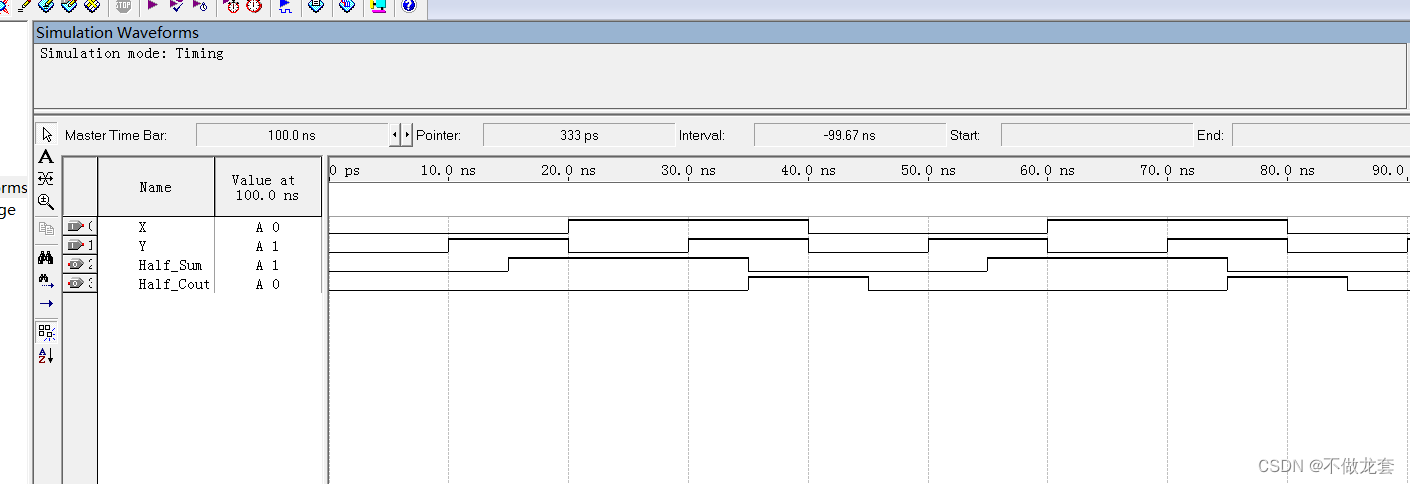

半加器时序仿真结果图

4.补充说明

注意,如出现如下报错,原因是没有在模拟器窗口中点击Generate Functional Simulation Netlist,解决方法是返回该窗口点击即可

二、1位全加器设计

1.实验原理

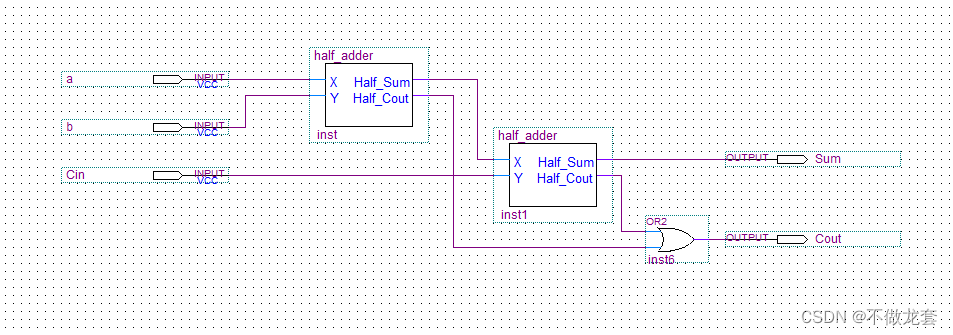

全加器的设计由两个半加器元件组成

2.Quartus建立工程

同半加器工程设计相同,这里省略

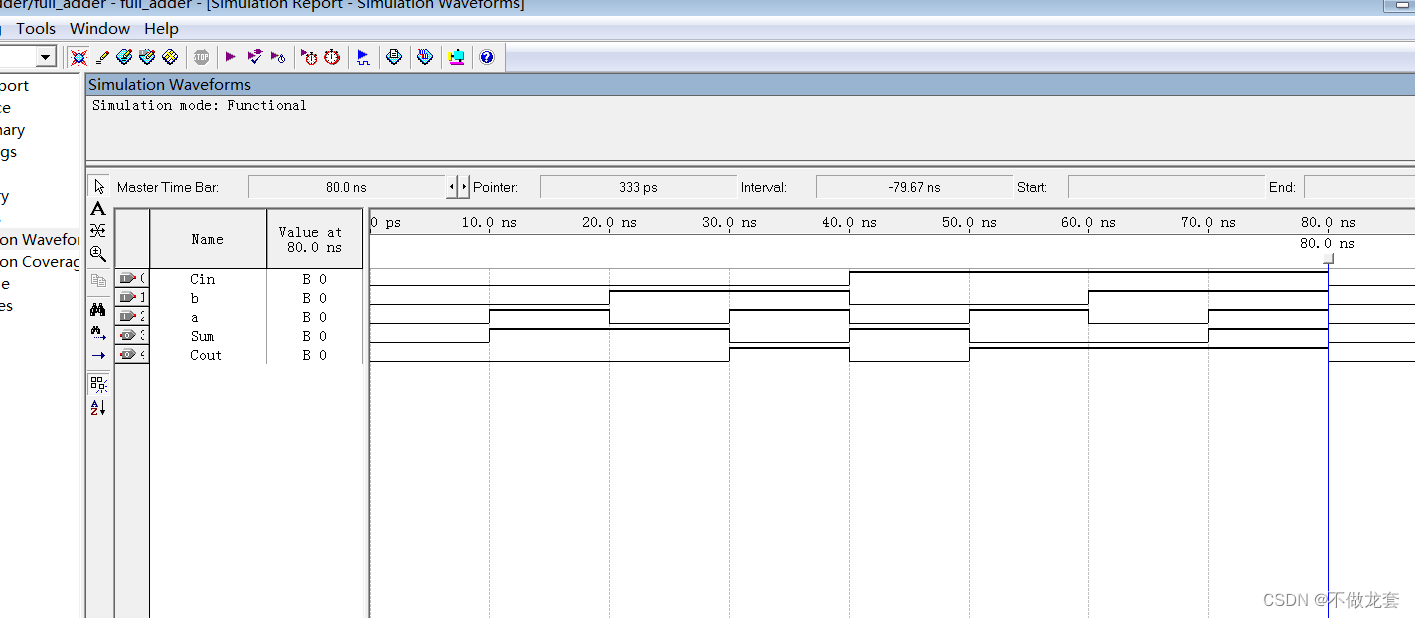

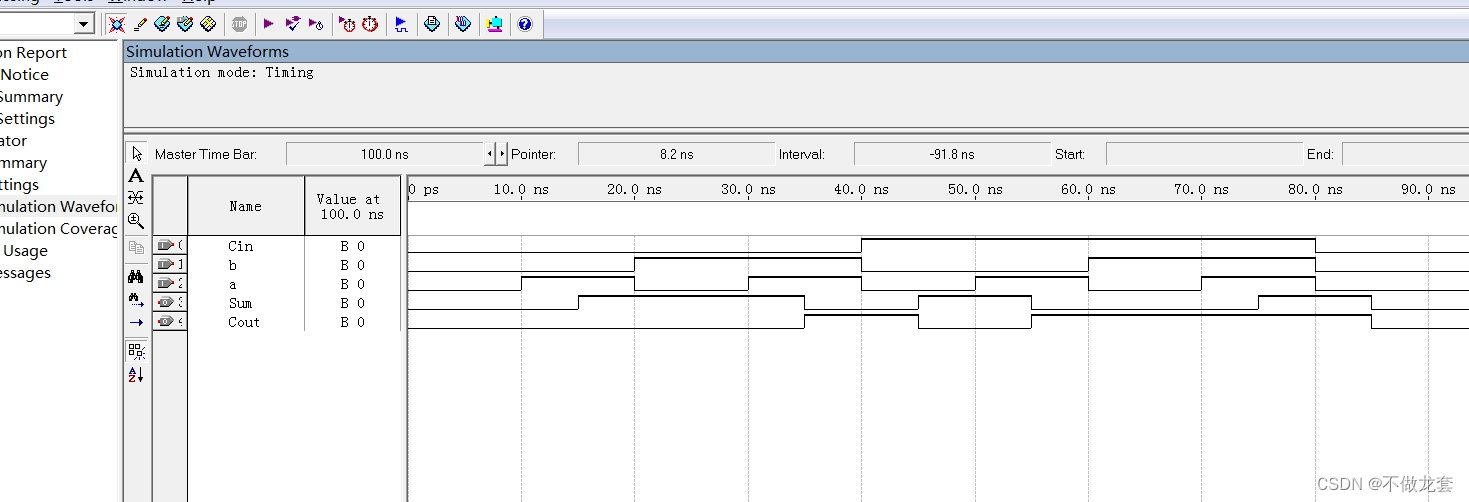

3.实验结果展示

全加器原理图

全加器功能仿真结果图

全加器时序仿真结果图

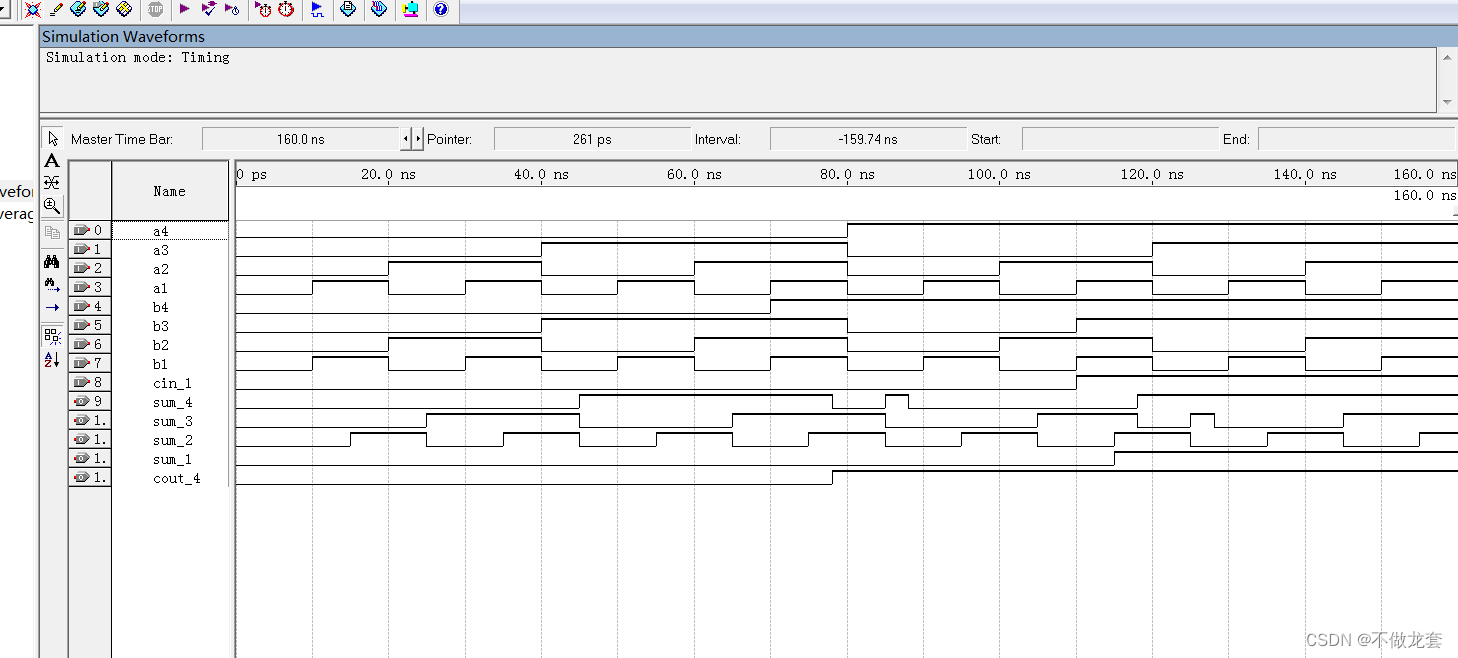

三、4位加法器设计

1.实验原理

4位加法器的设计由4个全加器元件组成

2.Quartus建立工程

同半加器工程设计相同,这里省略

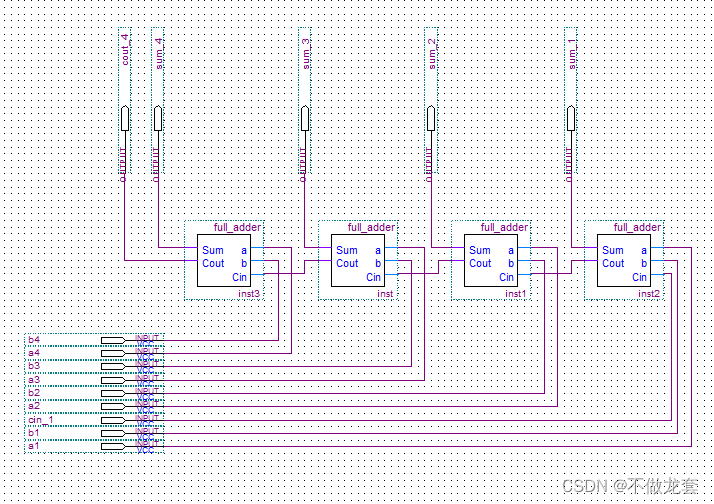

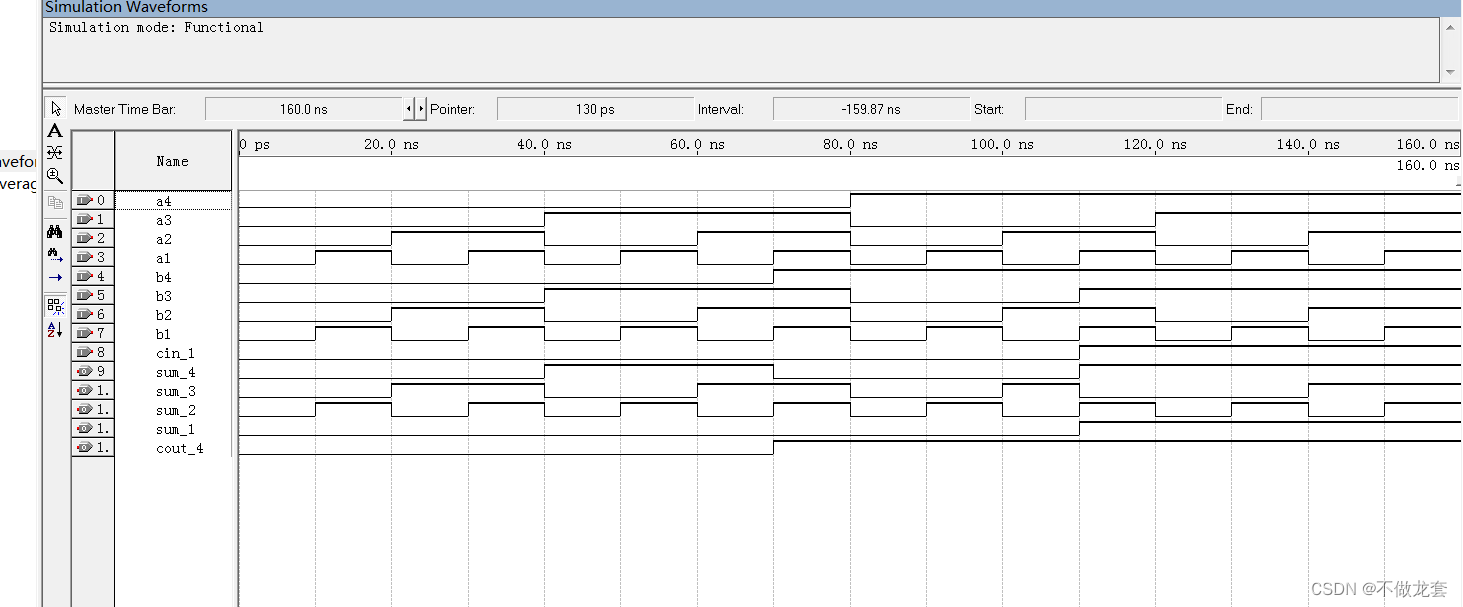

3.实验结果展示

4位加法器原理图

4位加法器功能仿真结果图

4位加法器时序仿真结果图