热门标签

热门文章

- 1项目经理应该具备的技能和素质是什么?_作为智能家居项目经理,我们需要具备哪些知识、技能和职业素养?

- 2Python:基于Python爬虫技术的抢票程序及其实现_python抢票程序代码

- 3常见的 NoSQL 数据库有哪些?一篇详尽(图表展示)_nosql有哪些

- 4Oracle分页查询:优化大数据集的结果集返回_oracle大数据分页查询

- 5详述GPS原理及RTK技术应用_rtk与gps数据的融合过程

- 6微软如何打造数字零售力航母系列科普01 --- Azure顾问(AZURE Advisor)简介

- 7Typecho主题 - 一款视频ZeVideo开源主题

- 8机器学习系统的设计

- 9从零开始!Jupyter Notebook的安装教程(附带pip和Python的安装教程)_jupyter notebook安装教程

- 10数据库SQL Server实验报告 之 SQL语言进行复杂查询(4/8)_1. 查找cs系所有女生的信息; n 2. 列出所有不姓王的学生的学号和姓名;

当前位置: article > 正文

Quartus II的基本使用及仿真_quartus仿真

作者:Gausst松鼠会 | 2024-04-23 06:38:39

赞

踩

quartus仿真

1.概述

本文描述的是如何利用QuartusII建立工程并进行基本的仿真操作。

2.建立工程及添加Vreilog文件

2.1 建立工程

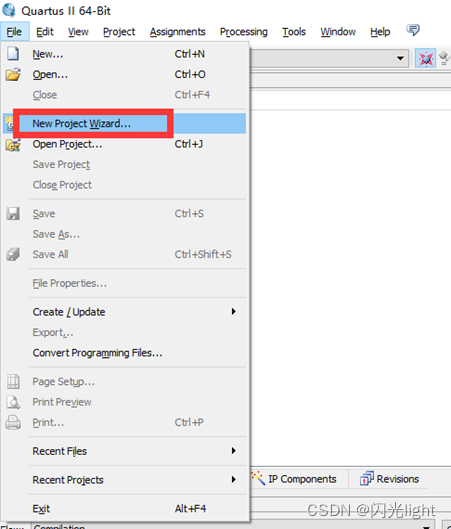

1.打开Quartus II,File>>New proje Wizard…

2. 设置工程路径和工程名。

3.是否要添加verilog文件?否的话直接点击next。

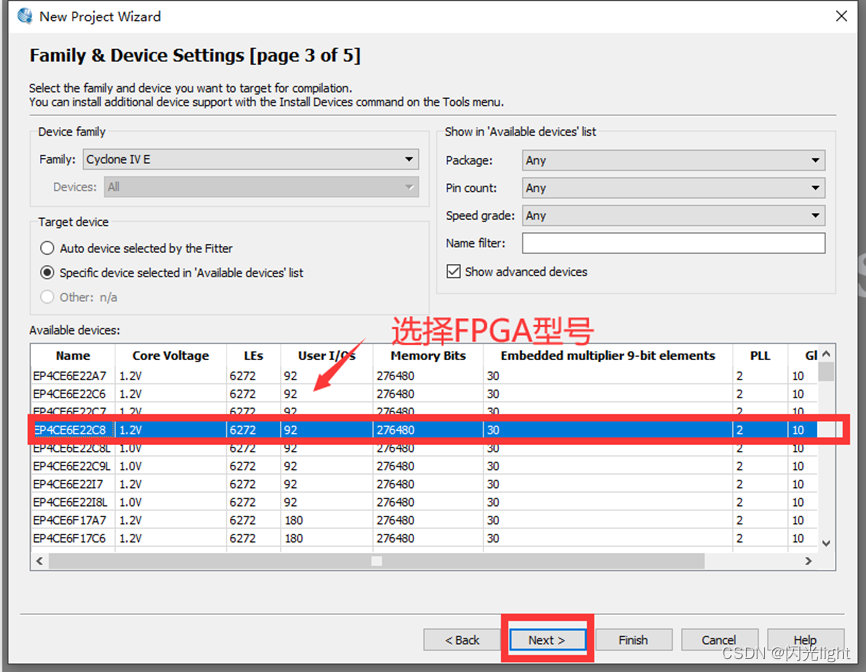

4.选择FPGA型号>>NEXT。

5.选择仿真工具和仿真语言,有的是Modelsim-Altera,有的是Modelsim,这个要视情况选择。

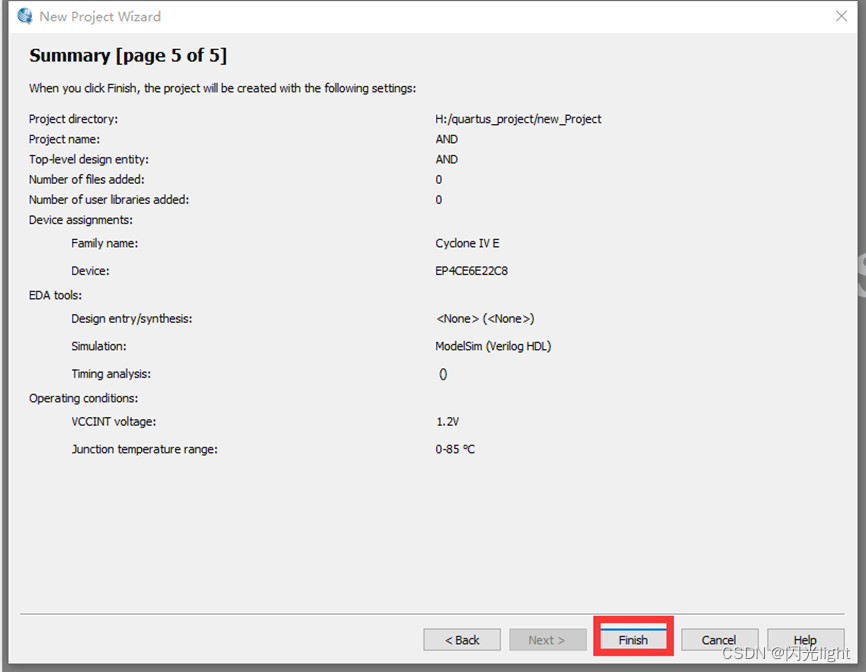

6.Finish。

2.2 添加和编写Verilog。

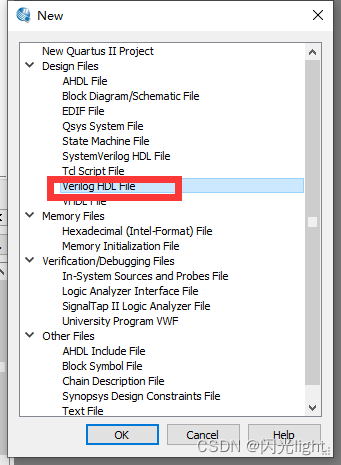

1. File>>New>>Verilog HDL>>OK;

2. 编写代码。

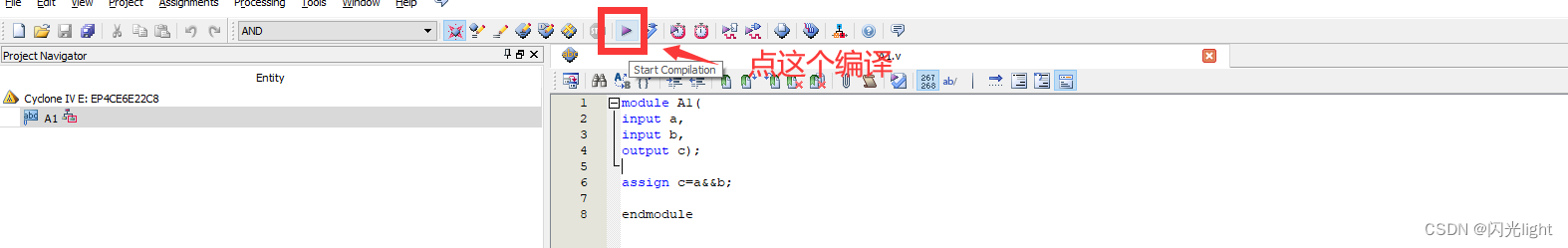

3. 编译。

4. 保存,注意模块名和文件名相同。

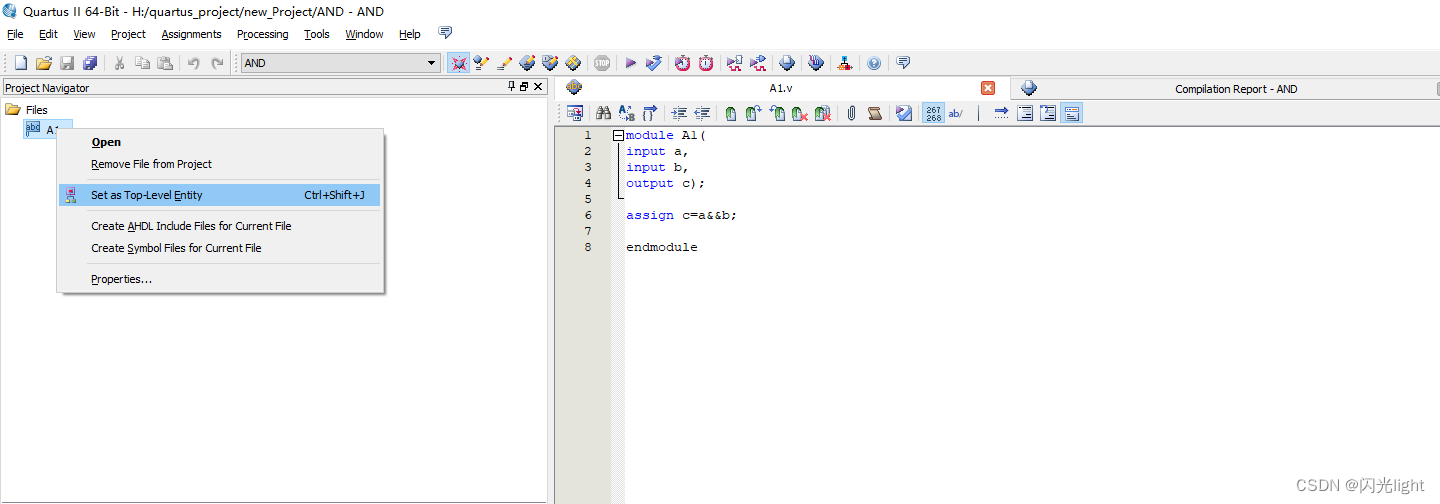

5. 设置顶层模块:右键点击你要设置为顶层模块的verilog文件,Set as Top-Level Entity即可将其设置为顶层模块。

3.仿真

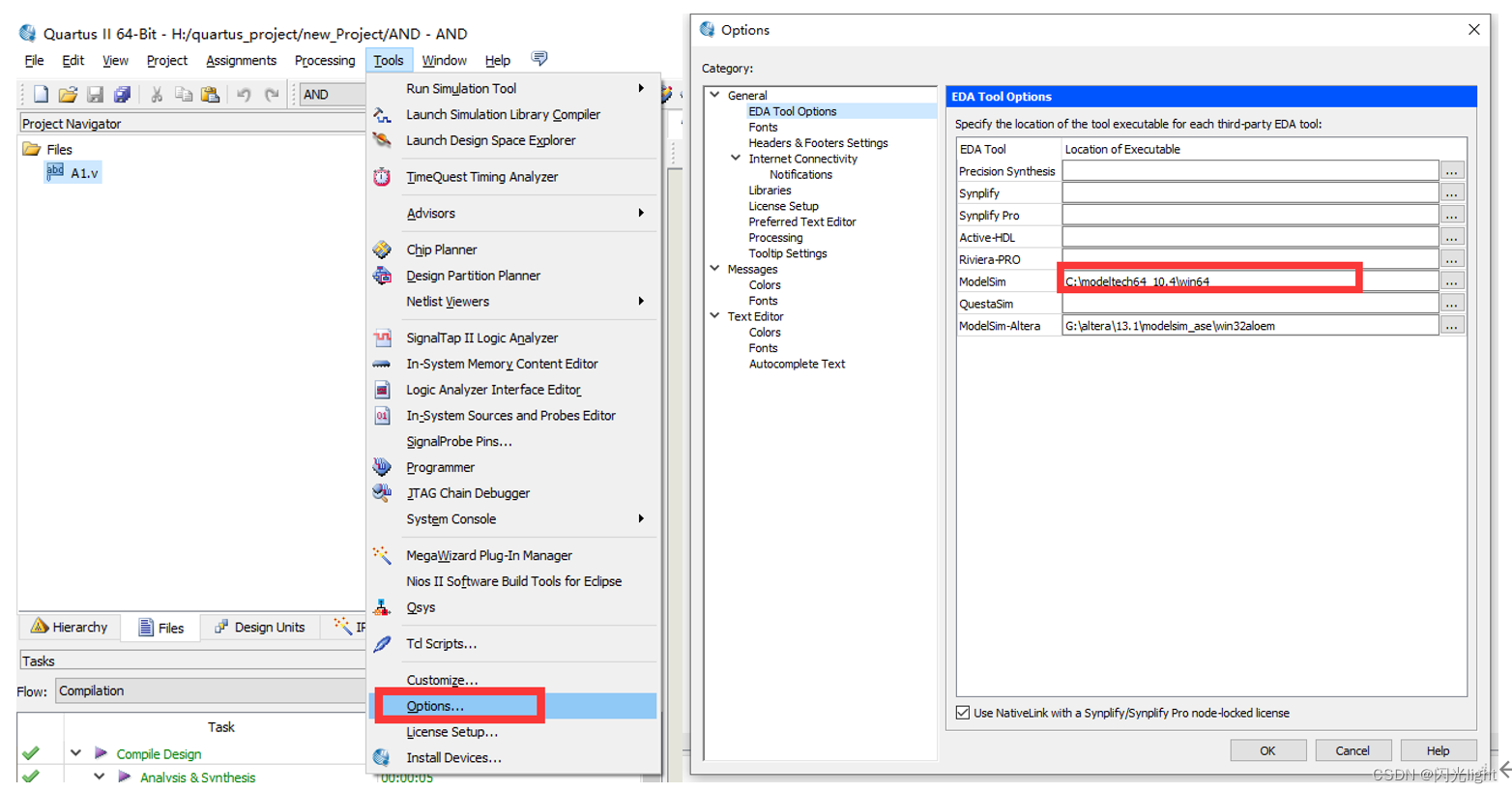

1.第⼀次⽤modelsim+quartus的时候需要在quartus中设置modelsim的路径,quartus->tools->Options…>EDA tool options ,在右边选择modelsim的安装路径,如下图:

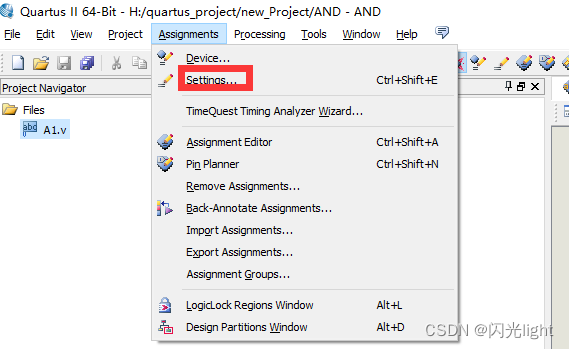

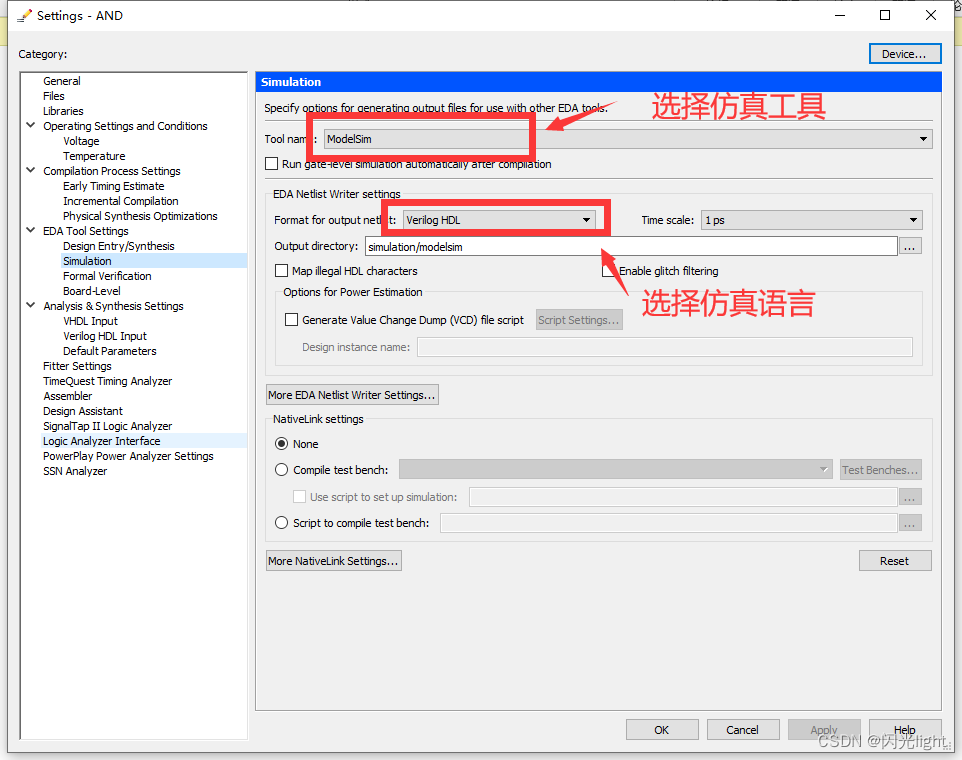

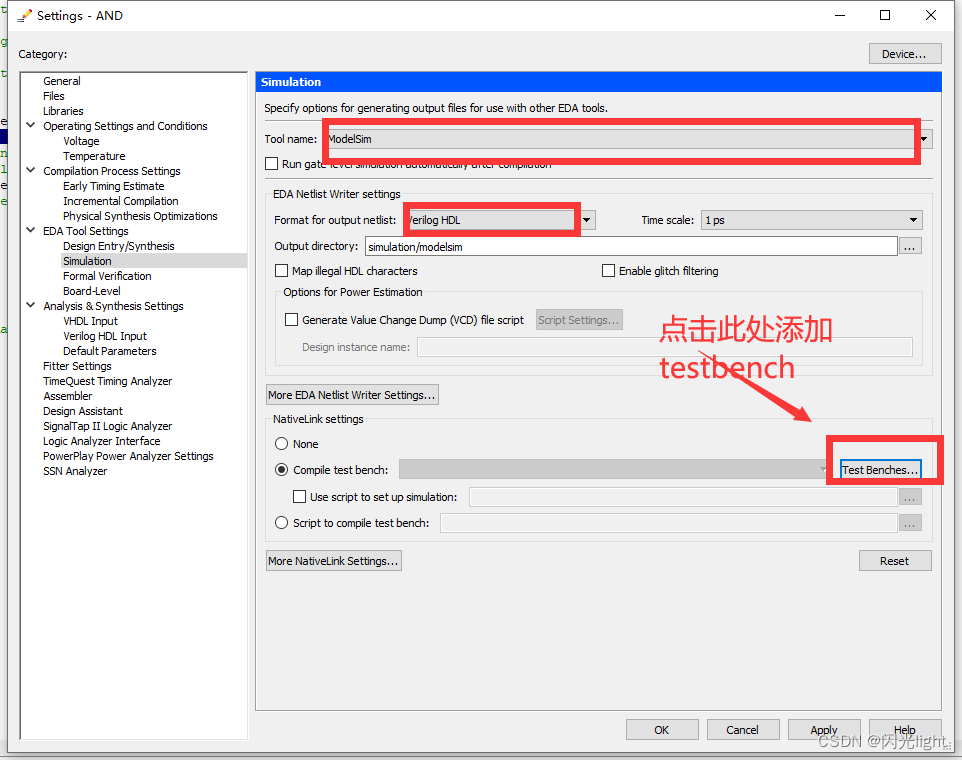

2.然后选择仿真工具和仿真语言,Assignments>>Settings>>Simulation:

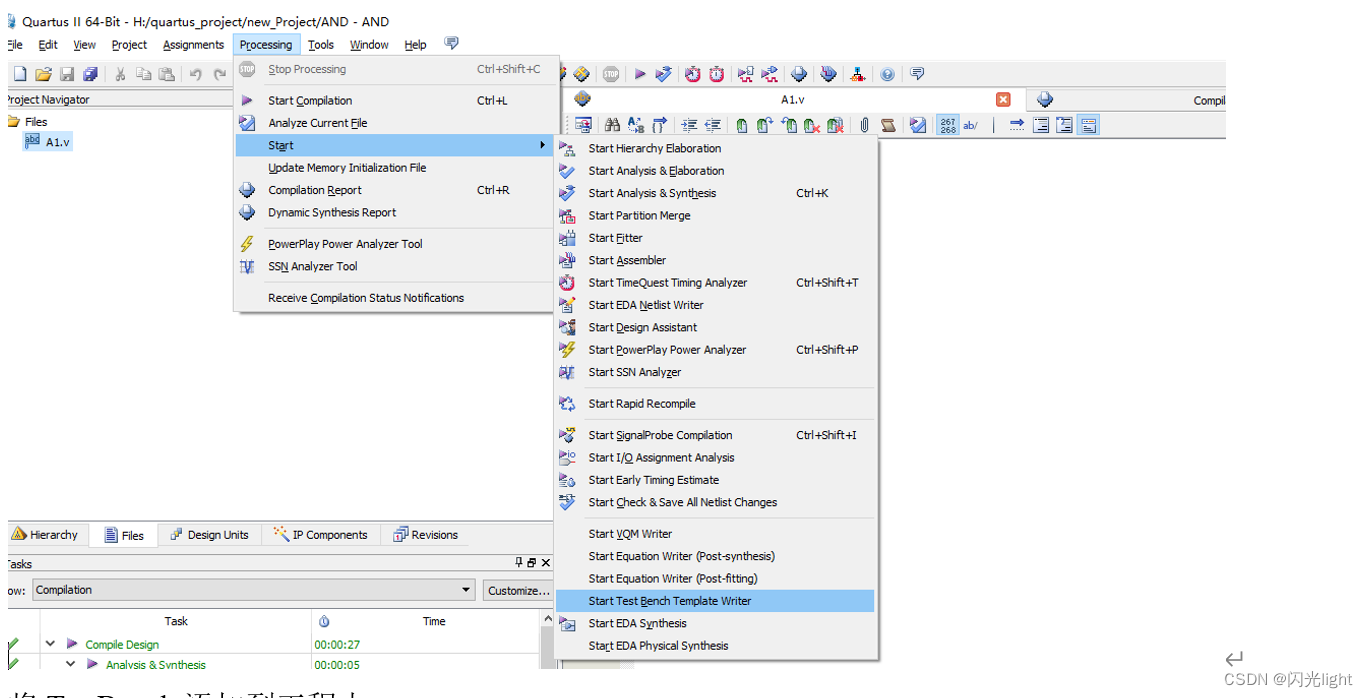

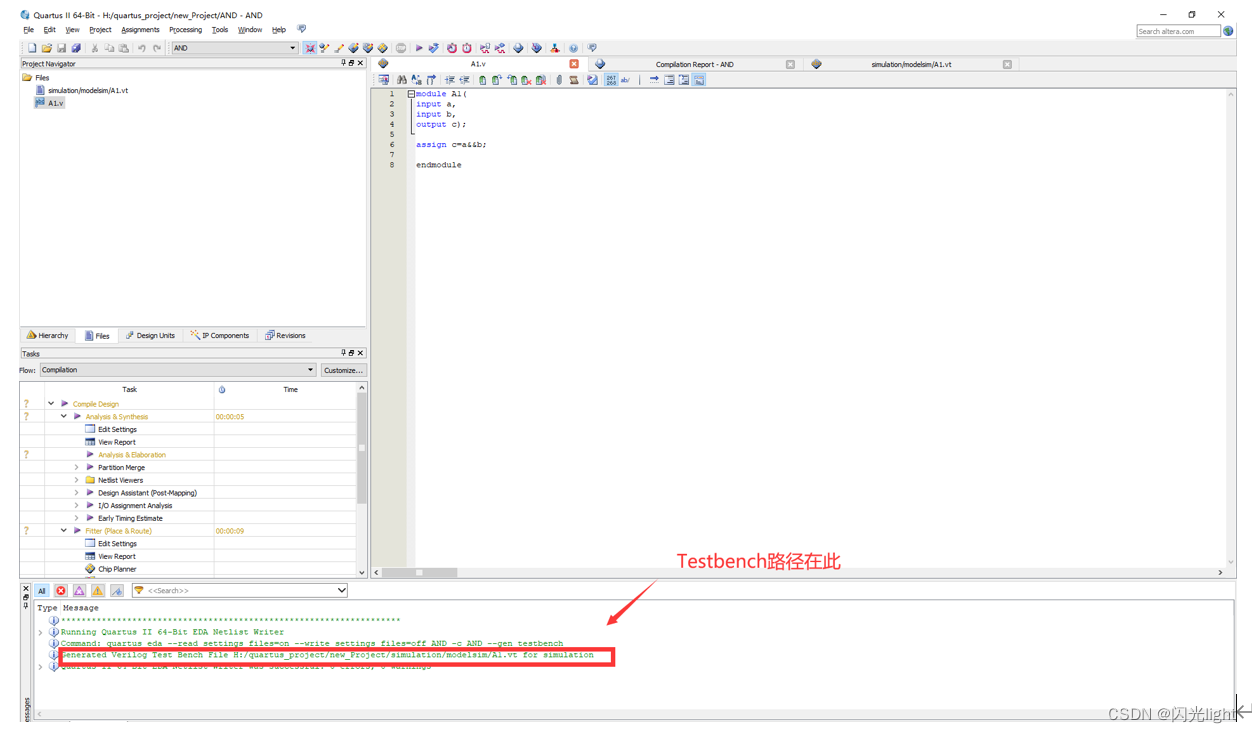

3.生成Testbench模板:点击Start Test Bench Template Writer即可自动生成Testbench。

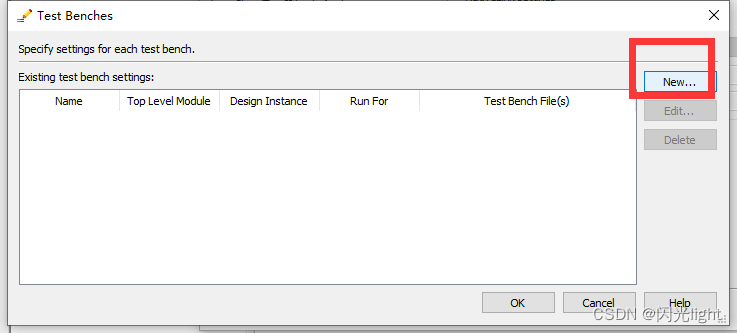

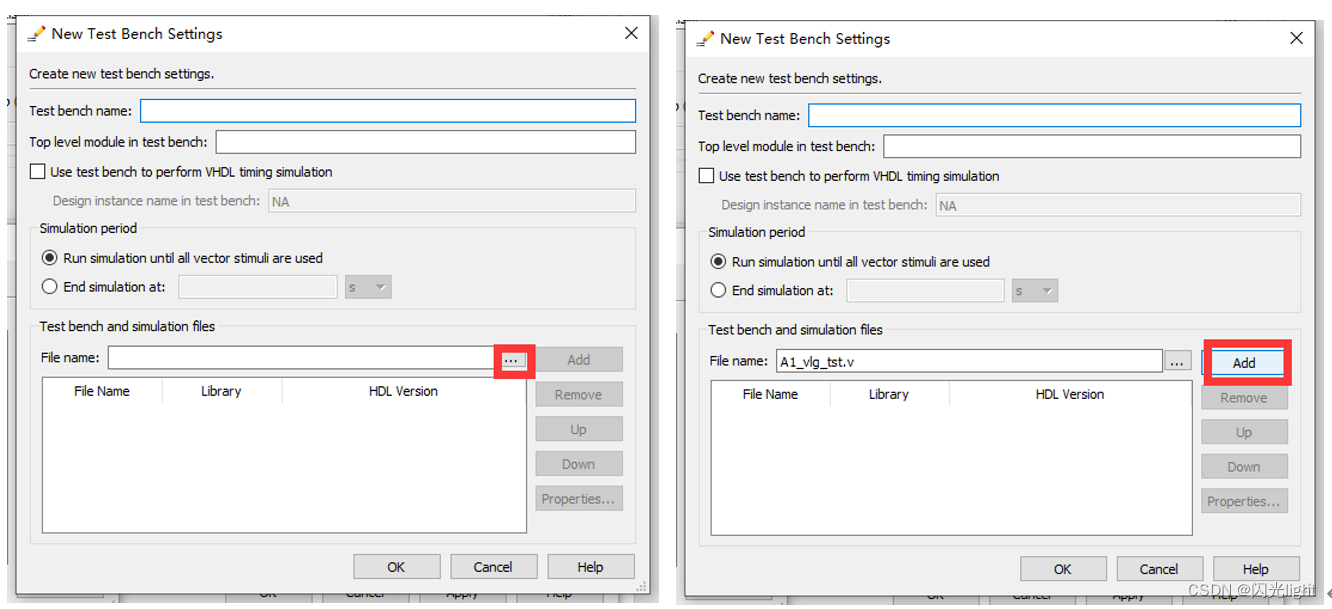

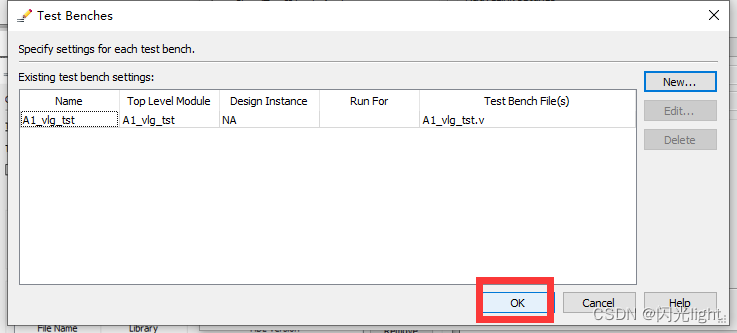

4.将TestBench添加到工程中:

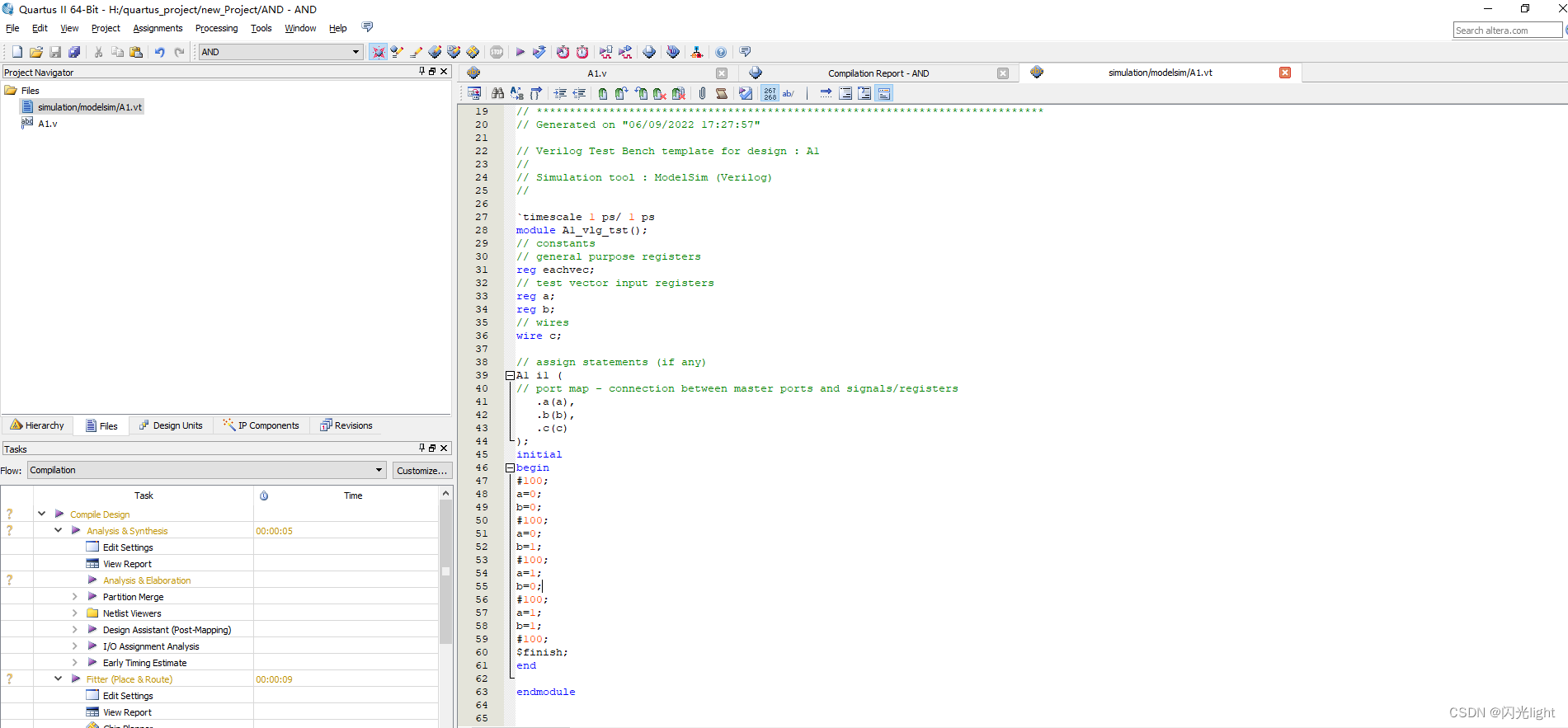

5.打开testbench文件,编写testbench;编写完后保存,记得模块名要和文件名一致。

6.点击Assignment -> Settings,添加编写完的testbench:

7.仿真

声明:本文内容由网友自发贡献,不代表【wpsshop博客】立场,版权归原作者所有,本站不承担相应法律责任。如您发现有侵权的内容,请联系我们。转载请注明出处:https://www.wpsshop.cn/w/Gausst松鼠会/article/detail/472633

推荐阅读

相关标签