- 1【Spring Boot 源码学习】SpringApplication 的 run 方法核心流程介绍

- 2鸿蒙OpenHarmony HDF 驱动开发_openharmony 驱动开发

- 3Git管理神器SourceTree使用教程详解(连接远程仓库,克隆,拉取,提交,推送,新建/切换/合并分支,冲突解决,提交PR)...

- 4来自字节大佬首发:基于Flutter的Hybrid Webview容器实践

- 5【计算机毕业设计】旅游信息管理系统

- 6大学英语综合教程四 Unit 5 课文内容英译中 中英翻译_mymisspentyouth课文翻译综合教程

- 7【网络安全 --- 文件包含漏洞】文件包含漏洞详解_4zus6zcr4

- 8谷歌浏览器的防火墙怎么关闭?_怎么解除谷歌浏览器的防火墙

- 9在线考试系统的设计与实现_在线考试系统设计与实现

- 10七天入门大模型 :大模型自动评估理论和实战_大模型自动生成 评价方法

FPGA实现LVDS视频输出,纯verilog代码驱动,提供2套工程源码和技术支持_fpga lvds

赞

踩

FPGA实现LVDS视频输出,纯verilog代码驱动,提供2套工程源码和技术支持

1、前言

LVDS协议作为中等速率的差分信号,在笔记本电脑和手机等消费电子领域应用广泛,FPGA实现LVDS视频协议也有广泛应用,一般在军工和医疗领域,LVDS视频相比RGB并行视频传输而言,图像质量和IO数量都有优势,对于做FPGA图像领域的工程师而言,LVDS是迈不过的坎儿,是必须掌握的技能;

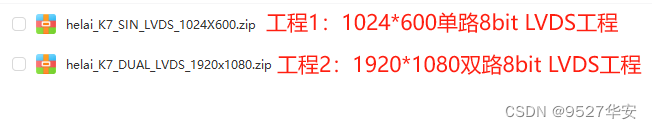

本设计基于Xilinx的 Kintex7 开发板,用verilog写了一个彩条作为视频源,利用Xilinx的OSERDESE2源语实现差分LVDS的产生,将并行的GRB888视频转换为差分LVDS视频输出显示器;提供2套vivado2019.1版本的工程,第一套工程的视频分辨率为1024600,单路8位LVDS输出;第二套工程的视频分辨率为19201080,双路8位LVDS输出;工程代码编译通过后上板调试验证,可直接项目移植,适用于在校学生做毕业设计、研究生项目开发,也适用于在职工程师做项目开发,可应用于医疗、军工等行业的数字成像和图像传输领域;

提供完整的、跑通的工程源码和技术支持;

工程源码和技术支持的获取方式放在了文章末尾,请耐心看到最后;

免责声明

本工程及其源码即有自己写的一部分,也有网络公开渠道获取的一部分(包括CSDN、Xilinx官网、Altera官网以及其他开源免费获取渠道等等),若大佬们觉得有所冒犯,请私信批评教育;部分模块源码转载自上述网络,版权归原作者所有,如有侵权请联系我们删除;基于此,本工程及其源码仅限于读者或粉丝个人学习和研究,禁止用于商业用途,若由于读者或粉丝自身原因用于商业用途所导致的法律问题,与本博客及博主无关,请谨慎使用。。。

2、目前我这里已有的图像处理方案

目前我这里已有的图像处理方案有很多,包括图像缩放、图像拼接、图像旋转、图像识别跟踪、图像去雾等等,所有工程均在自己的板子上跑通验证过,保证代码的可靠性,对图像处理感兴趣或有项目需求的兄弟可以参考我的图像处理专栏,里面包含了上述工程源码的详细设计方案和验证视频演示:直接点击前往

3、本 LVDS 方案的特点

1:纯verilog代码实现,利用Xilinx的OSERDESE2源语实现差分LVDS的产生,所以目前该源码只适用于Xilinx系列FPGA;

2:代码中文注释详细,若你打开注释乱码,请用NotePad++打开即可;

3:提供2套方案,单路8位LVDS和双路8位LVDS,实用性广泛;

4、详细设计方案

提供2套vivado2019.1版本的工程,第一套工程的视频分辨率为1024600,单路8位LVDS输出;第二套工程的视频分辨率为19201080,双路8位LVDS输出;

设计原理框图

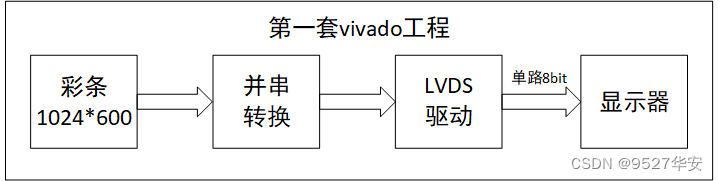

第一套工程设计原理框图如下:

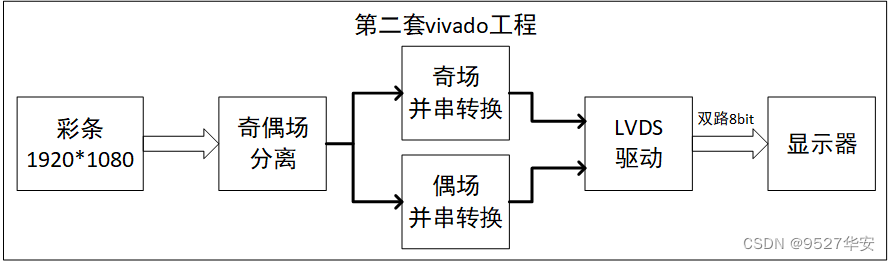

第二套工程设计原理框图如下:

彩条视频

用verilog写了一个彩条作为视频源,工程一的彩条分辨率为1024600;工程二的彩条分辨率为19201080;彩条本身很简单,这里不再赘述;

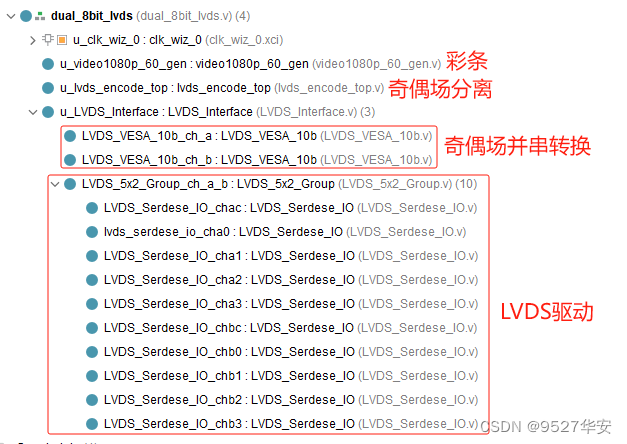

奇偶场分离

奇偶场分离模块在工程二中才有,双路的LVDS将视频分为奇偶场发送,奇偶场是模拟视频中的概念,对于入门较晚的兄弟而言比较陌生,这块可以在CSDN或知乎等平台搜索学习一下;奇偶场分离模块就是将1920*1080@60Hz的视频分为奇场和偶场偶;

并串转换

并串转换模块是把并行数据转成7bit的lvds 串行数据,怎么组合成串行,具体要看屏的规格书,如果不是用来点屏,用来做通信或者链接工业相机的,也可以更改这里调整他们的相对位置;

LVDS驱动

利用Xilinx的OSERDESE2源语实现差分LVDS的产生,这个就是调用源语,也没啥好说的,具体看代码;

5、vivado工程1:单路8bit LVDS

开发板FPGA型号:xc7k325tffg676-2;

开发环境:Vivado2019.1;

输入:verilog实现的彩条;

输出:单路8bit LVDS;

应用:FPGA实现LVDS视频输出;

工程代码架构如下:

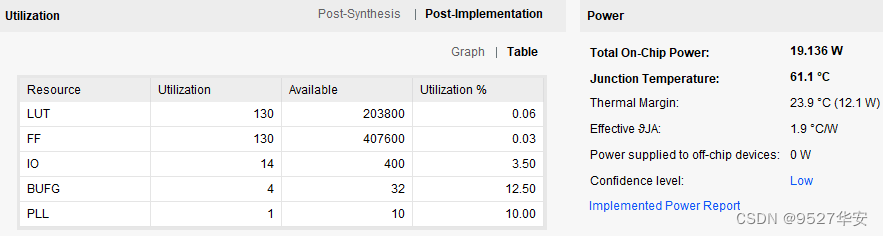

综合编译完成后的FPGA资源消耗和功耗预估如下:

6、vivado工程2:双路8bit LVDS

开发板FPGA型号:xc7k325tffg676-2;

开发环境:Vivado2019.1;

输入:verilog实现的彩条;

输出:双路8bit LVDS;

应用:FPGA实现LVDS视频输出;

工程代码架构如下:

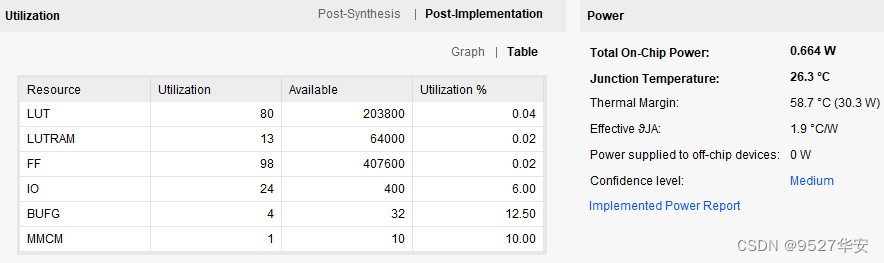

综合编译完成后的FPGA资源消耗和功耗预估如下:

7、工程移植说明

vivado版本不一致处理

1:如果你的vivado版本与本工程vivado版本一致,则直接打开工程;

2:如果你的vivado版本低于本工程vivado版本,则需要打开工程后,点击文件–>另存为;但此方法并不保险,最保险的方法是将你的vivado版本升级到本工程vivado的版本或者更高版本;

3:如果你的vivado版本高于本工程vivado版本,解决如下:

打开工程后会发现IP都被锁住了,如下:

此时需要升级IP,操作如下:

FPGA型号不一致处理

如果你的FPGA型号与我的不一致,则需要更改FPGA型号,操作如下:

更改FPGA型号后还需要升级IP,升级IP的方法前面已经讲述了;

其他注意事项

1:由于每个板子的DDR不一定完全一样,所以MIG IP需要根据你自己的原理图进行配置,甚至可以直接删掉我这里原工程的MIG并重新添加IP,重新配置;

2:根据你自己的原理图修改引脚约束,在xdc文件中修改即可;

3:纯FPGA移植到Zynq需要在工程中添加zynq软核;

8、上板调试验证

工程1的1024600输出单通道8bit LVDS屏输出演示,输出如下:

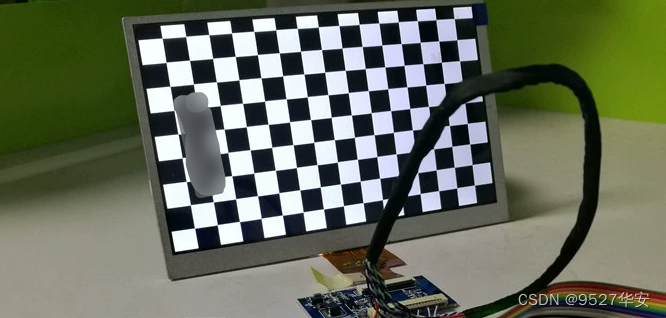

工程2的19201080输出双通道8bit LVDS屏输出演示,输出如下:

9、福利:工程代码的获取

福利:工程代码的获取

代码太大,无法邮箱发送,以某度网盘链接方式发送,

资料获取方式:私,或者文章末尾的V名片。

网盘资料如下: