引子:

HP中的DDR需要sys_clk和clk_ref两路输入,HR用户功能也需要usr_clk时钟输入。

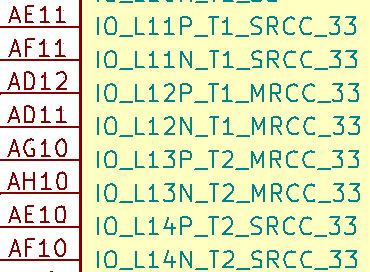

但是HR资源IO被完全占用,HP中只有bank33的MRCC/SRCC可以作为fpga的时钟输入。以及为了尽量减少差分晶振的数量,需要合理利用内部时钟资源。

一、先弄清楚DDR_controller的clk需求

调用MIG IP,选择DDR3 32位宽4GB。

System Clock给DDR控制器逻辑和接口提供时钟;Reference Clock单独给Delay单元提供时钟,用来调整DDR信号时序。