vivado和modelsim联合仿真_modelsim和vivado联合仿真

赞

踩

引言

虽然vivado自带了仿真工具,但是还是更加希望能用modelsim进行仿真,为后续的图像处理算法仿真作铺垫,所以查了相关资料搭建相关环境并熟悉相关使用方法。

软件版本

需要正确安装如下软件:vivado 2018.3、modelsim 22.04(这个最好是新版本,至少不能低于10.6c)

当你编译仿真库时,vivado会有提示的。

交叉编译仿真库

这个需要正常安装modelsim,并且将modelsim添加到环境变量中。

这一步是为了能让modelsim可以调用xilinx的一些特殊硬件结构(如IP核)进行仿真。

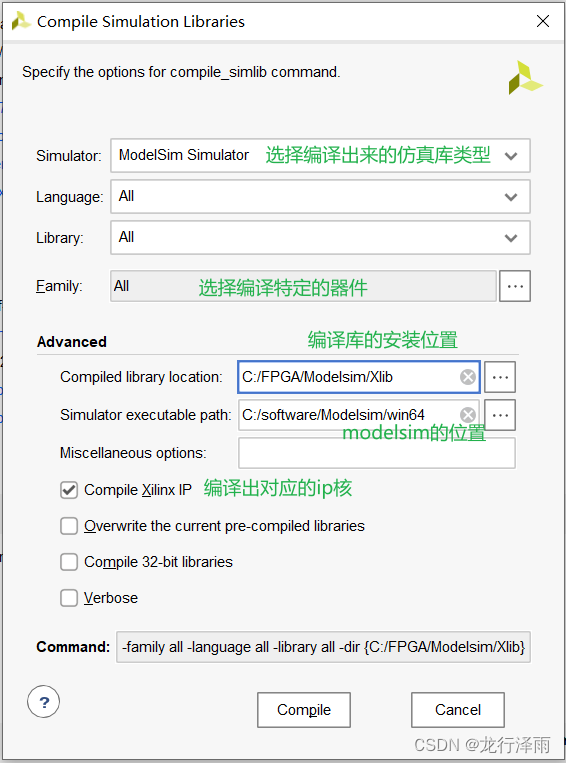

打开vivado工程,点击上面的tools,选择Compile Simulation Libraries,

如果只是开发不涉及Virtex-7、zynq、Artix-7等系列中的某一些,可以在这里选择对应的系列编译,减少生成库的空间和减少编译时间;Language可以选择VHDL、verilog或者两者都编译出来,Compile Xilinx IP则是对所有的IP核都生成仿真库,但有时候仿真的都是自己写的代码,不涉及IP核的话,也可以不编译。,最后点击Compile,等待数十分钟。编译完成后可以去到对应的目录下,发现里面存在一个modelsim.ini的文件,打开我的电脑设置环境变量如下:

这里的变量名设置为MODELSIM,值设置为刚刚编译出来的安装位置下的modelsim.ini,至此环境就搭建好了。

联合仿真

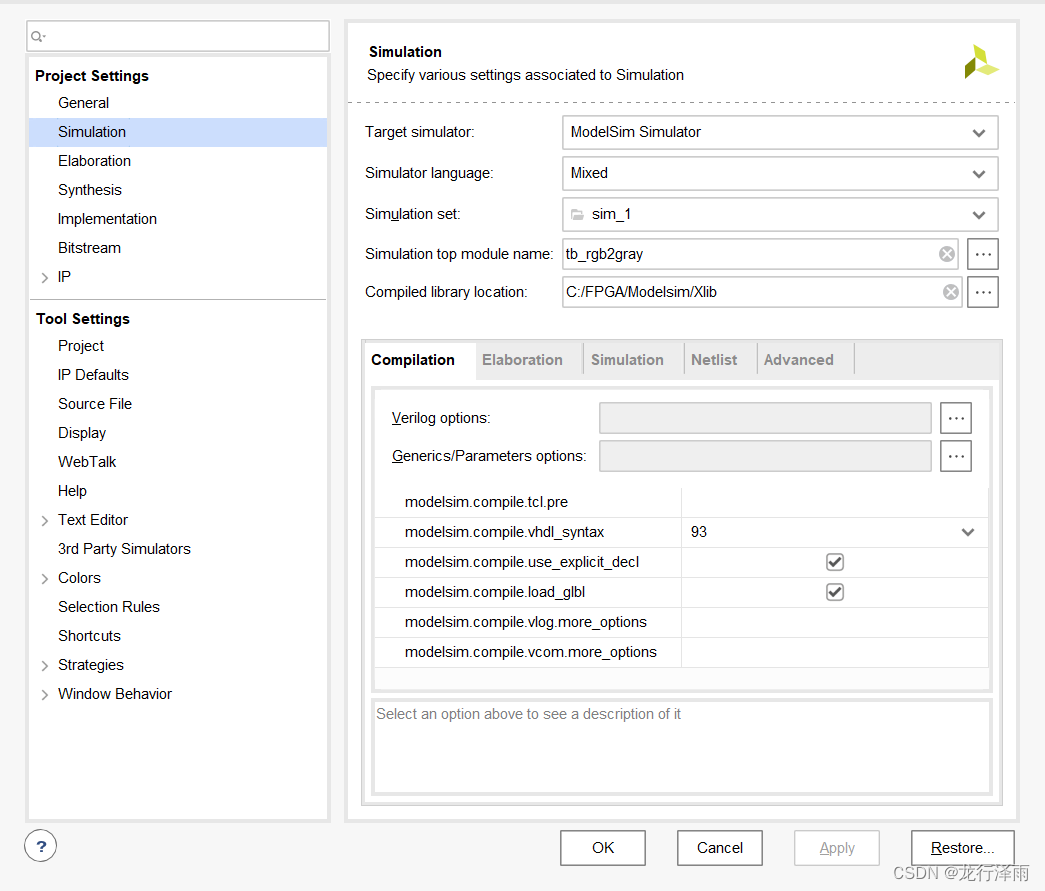

正常在vivado打开或者创建工程,然后修改仿真工具为modelsim和指定上述编译好的仿真库位置:点击tools->setting,将Simulation选择为modelsim。

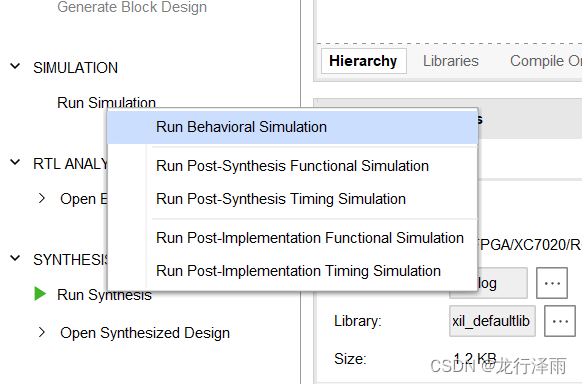

建议现在vivado上进行综合,检测语法错误,然后点击simulation->Run Simulation->Run Behavioral Simulation即可自动弹出modelsim,如果不能自动弹出可以检查是否已经将modelsim加入环境变量。

使用技巧

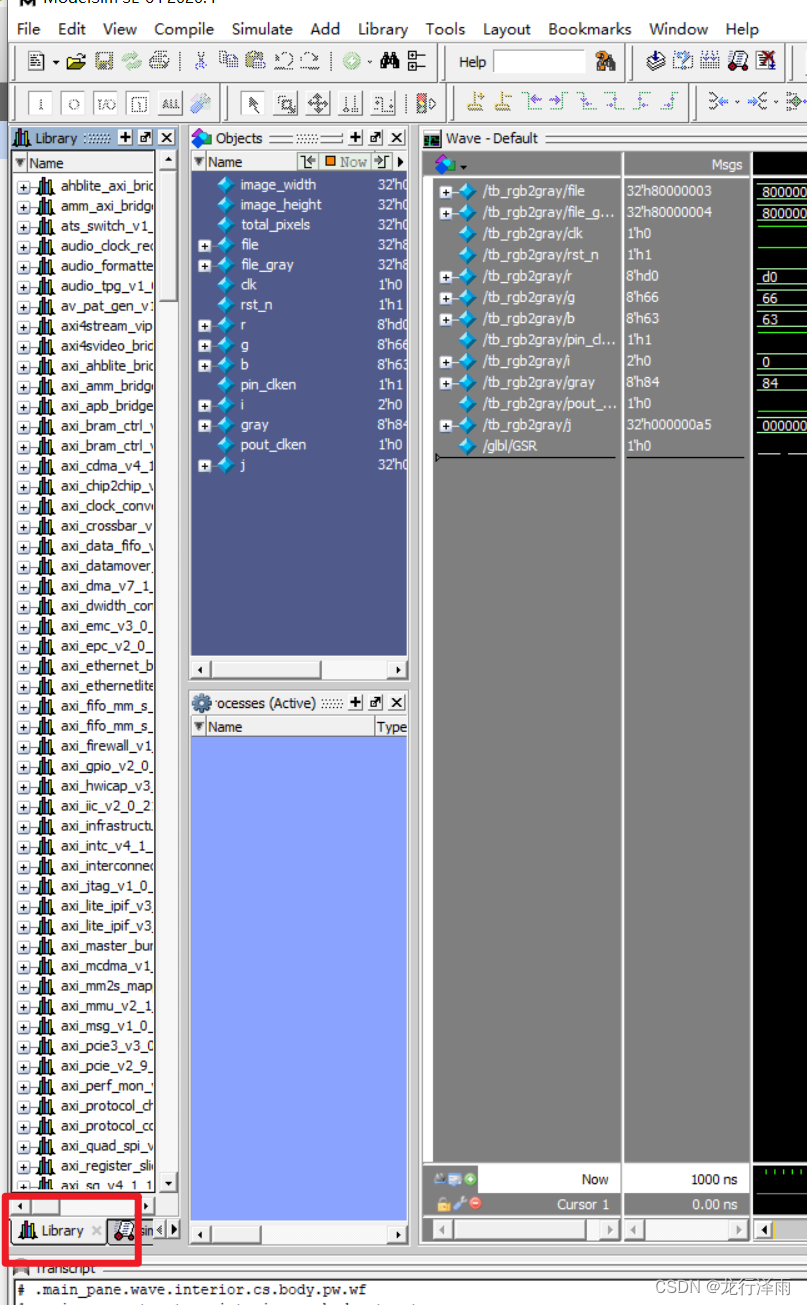

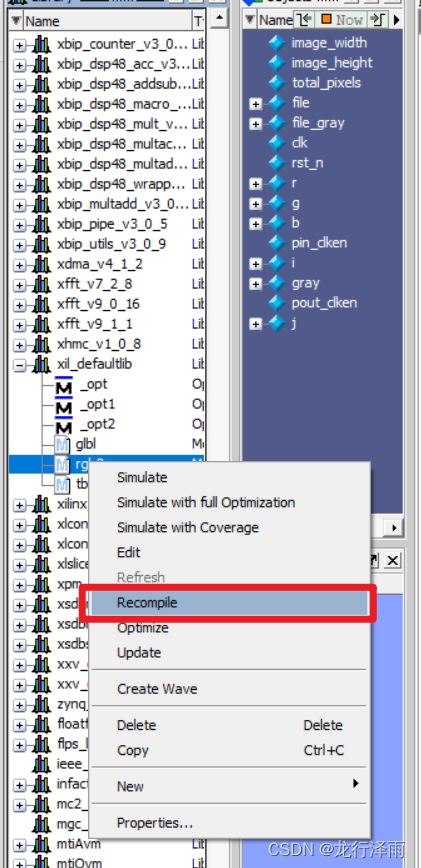

- 在弹出modelsim后,即可查看波形图,但如果后续修改了verilog源码,此时不需要关闭modelsim,点击Library

如果不小心关闭了这个窗口,可以在view->library重新开启:

找到xil_defaultlib,里面就是本次仿真的源码所在,修改了哪个文件就对相应的文件进行recompile即可。

重新编译完成后,依次点击Restart重置波形图像,Run All重新生成波形图像,通过上述步骤即可在不关闭modelsim的前提下,仿真已被修改的源码。

- 如果没有修改源码,只是对仿真显示的信号波形进行更改(如增加显示内部模块的信号波形),则不需要Recompile,直接Restart、Runall即可。

- 如果仿真过程中设计文件的读写,如进行图像处理算法仿真的时候需要读入图像数据,此时就需要将相关文件拷贝到modelsim工程目录,对于vivado和modelsim联合仿真,其工程目录位于:

里面的\sim_1\behav\modelsim,既不是在被仿真模块源码的同级目录,也不是在TestBench源码的同级目录,所以需要将相关文件拷贝到此处,生成的文件也存放在此处。