- 1图解缓存淘汰算法 LRU、LFU | 最近最少使用、最不经常使用算法 | go语言实现_lfu什么时候插入新元素

- 2小红书内容数据抓取新方式:笔记详情API助力高效获取与分析_小红书爬虫笔记

- 3重磅!金融监管总局出台《银行保险机构数据安全管理办法》!金融行业安全迎来新变革?_银行业保险业网络安全监管办法

- 4堆排序及其时间复杂度(C语言)_一个堆排序的时间复杂度

- 5多个hackrf one可以做什么科研_hackrf能干什么

- 6vTestStudio保姆教程之从0到1搭建软件环境_vteststudio教程

- 7树莓派 Putty远程登录+远程桌面连接_树莓派远程密码是什么

- 8Linux下相关的基础配置(第一篇)

- 9大数据学习之ZooKeeper——集群搭建

- 10基于 VScode 的 git 详细使用指南【保姆级!建议收藏!】_vscode使用git需要电脑安装git吗_vscode git

AD936x 配置软件介绍 中(AD936x Evaluation Software)_ad936x软件的delay cell control选项配置

赞

踩

MGC、Slow AGC、Fast AGC补充: AD9361 补充(上)

二、使用介绍

2.7 数据接口详细设置

2.7.1 LVDS Setting

如下表所示,通过对0x03D和0x03E这两个寄存器中的位置1,可以将任何LVDS差分对的相位从默认配置反转。默认配置下数据位是反转的,时钟和帧信号不反转。设置0x03D = 0xFF和0x03E = 0x0F以防止数据反转。需要在软件中将端口数据勾选。

Enable LVDS On chip termination :使能LVDS模式,勾选

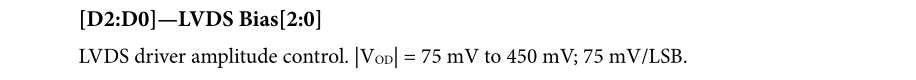

RX LVDS amplitude : 后续使用zc706,选取150mv

2.7.2 General Setting

都不勾选

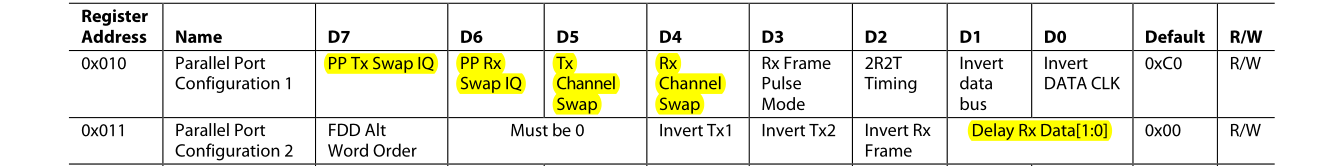

- 2R2T Timing : 勾选时,数据端口使用2R2T时序,与启用的发射和接收通道数量无关。不勾选时,时序反映使能信号通道的数量。

- Invert DATACLK : 勾选时会反转DATA_CLK。

- Invert Bus P0 : 将数据端口P0从[11:0]反转到[0:11]

2.7.3 Tx/Rx DATA Setting

-

Tx Swap IQ : 不勾选时会交换Tx通道I和Q(执行频谱反转),勾选

-

Rx Swap IQ : 不勾选时会交换Rx通道I和Q(执行频谱反转),勾选

-

Tx Swap Channel : 勾选时会交换Tx1和Tx2通道样本,不勾选

-

Rx Swap Channel : 勾选时会交换Rx1和Rx2通道样本,不勾选

-

Rx Data delay : 设置接收数据相对于Rx frame的延迟,以DDR时1/2 DATA_CLK周期和SDR时一个DATA_CLK周期来测量。默认不延迟

2.7.4 Rx Frame Setting

- Rx Frame Pulse : 详见 AD9361 介绍 (终) 11.1 Rx_FRAME部分,我们采用脉冲序列(50%占空比)模式,本次勾选

- Invert Rx Frame : 勾选会反转 Rx frame ,本次不勾选

2.7.5 Delay Cell Control

详见 AD9361 介绍 (终) 11.3 双端口全双工 时序分析,需要根据实际情况调整Rx Data与DATACLK 和 Tx Data与FBCLK 之间的相位,满足对信号建立时间和保持时间的要求。如果时序不合适,AD9361就不能采样到正确的Tx Data信号,FPGA也不能采样到正确的Rx Data信号。

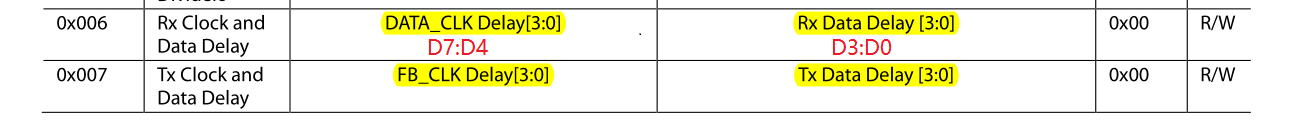

寄存器 0x006和0x007这些位影响DATA和CLK的延时,典型延时约为0.3 ns/LSB。Frame 的延迟量与 data 相同。最小延迟为0x0,最大延迟为0xF。

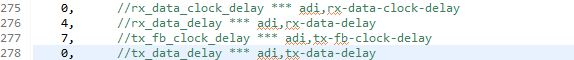

根据ADI官方给的zc706 例程,设置如下

- DATACLK delay : 0

- Rx Data /Frame delay : 4

- FBCLK delay : 7

- Tx Data /Frame delay : 0

2.8 ENSM

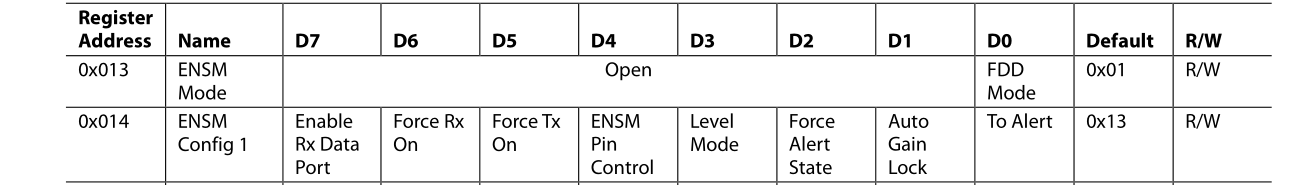

ENSM详见AD9361 介绍 (中) 第八部分,选取FDD模式,ENSM由SPI 来控制,通过上图中对寄存器0x014进行SPI写来控制ENSM状态,不使用FDD独立控制模式,Enable Pin 采用电平模式。

2.9 增益控制

增益控制详见AD9361 介绍 (中) 第六部分

2.9.1 增益控制快速设置

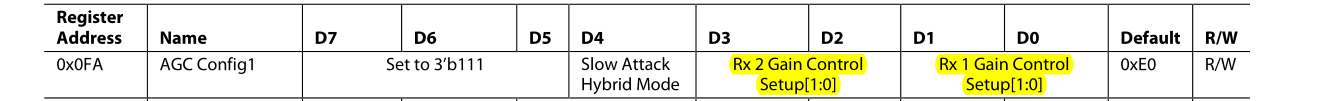

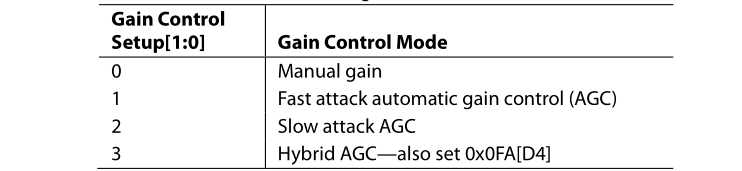

FDD模式下,我们选择AGC ,Slow attack 模式,暂不选手动增益控制模式。

相应寄存器如下图所示:

2.9.2 增益控制详细设置

完成增益控制快速设置后,可以再次运行下图所示的 RX Gain Contral Wizard,所有设置可以根据需要进行调整。

下图为AGC Fast Attack 、 AGC Slow Attack 和 MGC配置步骤框图

下图增益表具体介绍在AD9361 介绍 (中) 6.1

AGC Attack Delay :寄存器 0x022,用于fast AGC,AGC Attack Delay防止AGC在接收路径稳定之前启动其算法。当ENSM进入接收状态时,延迟计数器开始计时。单位:微秒,分辨率:1µs/LSB,范围:0到31微秒。 先采用默认值10µs。

到这步可以适用大部分应用,可以点击上图黑色框部位,先把设置好的值加载进去,再点击Finsh按钮,退出增益控制向导。

或者点击 Next 继续配置,由于选取的模式不同,配置内容不同,AGC Fast Attack 、 AGC Slow Attack 和 MGC具体详细配置见AD936x 配置软件介绍 下

2.10 Receive

设置 RX Frequency 2.4GHz ,Gain Index在AD9361 介绍 (中) 介绍 ,RSSI在 AD9361 补充(中)介绍。

2.11 Trainsmit

设置 TX Frequency 为 2.5GHz ,TX Attenuation 详见 AD9361 补充(中)。

三、脚本

3.1 生成脚本

对各项配置完成后,点击Create Init Script 按钮。有两种生成方式:1)Low Level Scripting ,2)High Level Scripting

3.1.1 Low Level Scripting

该方式得到的脚本仅使用 SPIRead/SPIWrites,部分脚本如下:

//************************************************************ // AD9361 R2 Auto Generated Initialization Script: This script was // generated using the AD9361 Customer software Version 2.1.3 //************************************************************ // Profile: Custom // REFCLK_IN: 40.000 MHz RESET_FPGA RESET_DUT BlockWrite 2,6 // Set ADI FPGA SPI to 20Mhz SPIWrite 3DF,01 // Required for proper operation ReadPartNumber SPIWrite 2A6,0E // Enable Master Bias SPIWrite 2A8,0E // Set Bandgap Trim REFCLK_Scale 40.000000,1,2 // Sets local variables in script engine, user can ignore SPIWrite 292,08 // Set DCXO Coarse Tune[5:0]. Coarse and Fine nominal values used with eval system. Other nominal values may be needed in a customer system SPIWrite 293,80 // Set DCXO Fine Tune [12:5] SPIWrite 294,00 // Set DCXO Fine Tune [4:0] SPIWrite 2AB,07 // Set RF PLL reflclk scale to REFCLK * 2 SPIWrite 2AC,FF // Set RF PLL reflclk scale to REFCLK * 2 SPIWrite 009,07 // Enable Clocks WAIT 20 // waits 20 ms //************************************************************ // Set BBPLL Frequency: 983.040000 //************************************************************ SPIWrite 045,00 // Set BBPLL reflclk scale to REFCLK /1 SPIWrite 046,03 // Set BBPLL Loop Filter Charge Pump current SPIWrite 048,E8 // Set BBPLL Loop Filter C1, R1 SPIWrite 049,5B // Set BBPLL Loop Filter R2, C2, C1 SPIWrite 04A,35 // Set BBPLL Loop Filter C3,R2 SPIWrite 04B,E0 // Allow calibration to occur and set cal count to 1024 for max accuracy SPIWrite 04E,10 // Set calibration clock to REFCLK/4 for more accuracy SPIWrite 043,29 // BBPLL Freq Word (Fractional[7:0]) SPIWrite 042,5C // BBPLL Freq Word (Fractional[15:8]) SPIWrite 041,12 // BBPLL Freq Word (Fractional[23:16]) SPIWrite 044,18 // BBPLL Freq Word (Integer[7:0]) SPIWrite 03F,05 // Start BBPLL Calibration SPIWrite 03F,01 // Clear BBPLL start calibration bit SPIWrite 04C,86 // Increase BBPLL KV and phase margin SPIWrite 04D,01 // Increase BBPLL KV and phase margin SPIWrite 04D,05 // Increase BBPLL KV and phase margin WAIT_CALDONE BBPLL,2000 // Wait for BBPLL to lock, Timeout 2sec, Max BBPLL VCO Cal Time: 345.600 us (Done when 0x05E[7]==1)

- 1

- 2

- 3

- 4

- 5

- 6

- 7

- 8

- 9

- 10

- 11

- 12

- 13

- 14

- 15

- 16

- 17

- 18

- 19

- 20

- 21

- 22

- 23

- 24

- 25

- 26

- 27

- 28

- 29

- 30

- 31

- 32

- 33

- 34

- 35

- 36

- 37

- 38

- 39

- 40

- 41

- 42

- 43

- 44

- 45

3.1.2 High Level Scripting

该方式得到的脚本还使用 ADI Script functions,部分脚本如下:

//************************************************************ // AD9361 R2 Auto Generated Initialization Script: This script was // generated using the AD9361 Customer software Version 2.1.3 //************************************************************ // Profile: Custom // REFCLK_IN: 40.000 MHz RESET_FPGA RESET_DUT BlockWrite 2,6 // Set ADI FPGA SPI to 20Mhz SPIWrite 3DF,01 // Required for proper operation ReadPartNumber SPIWrite 2A6,0E // Enable Master Bias SPIWrite 2A8,0E // Set Bandgap Trim REFCLK_Scale 40.000000,1,2 // Sets local variables in script engine, user can ignore SPIWrite 292,08 // Set DCXO Coarse Tune[5:0]. Coarse and Fine nominal values used with eval system. Other nominal values may be needed in a customer system SPIWrite 293,80 // Set DCXO Fine Tune [12:5] SPIWrite 294,00 // Set DCXO Fine Tune [4:0] SPIWrite 2AB,07 // Set RF PLL reflclk scale to REFCLK * 2 SPIWrite 2AC,FF // Set RF PLL reflclk scale to REFCLK * 2 SPIWrite 009,07 // Enable Clocks WAIT 20 // waits 20 ms BBPLL_Freq 983.040000 // Set BBPLL Frequency WAIT_CALDONE BBPLL,2000 // Wait for BBPLL to lock, Timeout 2sec, Max BBPLL VCO Cal Time: 345.600 us (Done when 0x05E[7]==1) SPIRead 05E // Check BBPLL locked status (0x05E[7]==1 is locked) SPIWrite 002,4E // Setup Tx Digital Filters/ Channels SPIWrite 003,5E // Setup Rx Digital Filters/ Channels SPIWrite 004,03 // Select Rx input pin(A,B,C)/ Tx out pin (A,B) SPIWrite 00A,09 // Set BBPLL post divide rate ProgramTxFIR C:\Program Files (x86)\Analog Devices\AD9361R2 Evaluation Software 2.1.3\DigitalFilters\LTE20_MHz.ftr // Program Tx FIR Filter ProgramRxFIR C:\Program Files (x86)\Analog Devices\AD9361R2 Evaluation Software 2.1.3\DigitalFilters\LTE20_MHz.ftr // Program Rx FIR Filter

- 1

- 2

- 3

- 4

- 5

- 6

- 7

- 8

- 9

- 10

- 11

- 12

- 13

- 14

- 15

- 16

- 17

- 18

- 19

- 20

- 21

- 22

- 23

- 24

- 25

- 26

- 27

- 28

- 29

- 30

- 31

- 32

- 33

- 34

- 35

- 36

- 37

3.2 常用脚本命令

3.2.1 FPGA

- RESET_FPGA : FPGA执行硬复位

- BlockWrite :参数 Address(hex),Data(hex), 将16位地址、32位数据对写入FPGA

- WAIT :参数 Time(ms) , 等待X毫秒,然后继续执行脚本

3.2.2 AD9361

- SPIWrite : 参数 Address(Hex),Data(Hex),将8位数据字写入指定的10位地址

- SPIRead : 参数Address(Hex), 在指定的10位地址回读8位数据

- ProgramRxFIR :参数 Filepath ,使用指定文件对RX FIR滤波器进行编程

- ProgramTxFIR :参数 Filepath ,使用指定文件对TX FIR滤波器进行编程

全部的脚本命令可在 AD9361 Script Commands(见该软件中Documents)中查看。从软件整体配置过程及得到的配置脚本,我们可以加深对AD9361的了解。

有不对的地方,欢迎大家在评论区指正,非常感谢!