- 1如何使用Springboot开发实现一个物业管理系统_物业系统怎么做

- 2Scrcpy_安卓手机投屏电脑 | 流畅高帧率 | 电脑控制手机 | 无线投屏 | 免安装 | 可录屏

- 3点云地面滤波实验之渐进形态学(实验二)

- 4【每周一文】A Few Usefull Things to know about Machine Learning_a few useful things to know about machine learning

- 5Google IO 2023推出Android Studio官方AI工具Studio Bot

- 6Android 五大数据存储 数据库加密 数据库升级 跨进程共享数据(含greendao招商银行转账示例实务操作)_sharedprefereces 跨进程

- 7Android方案需求,Android 三种适配方案

- 8docker 服务的启动命令_docker启动命令

- 9中国特色新型智 谋定研究·中国智库-周湘智:发展趋势与走向

- 10机器学习系列文章(chapter two)——数据特征分析处理_数据特征趋势分析机器学习

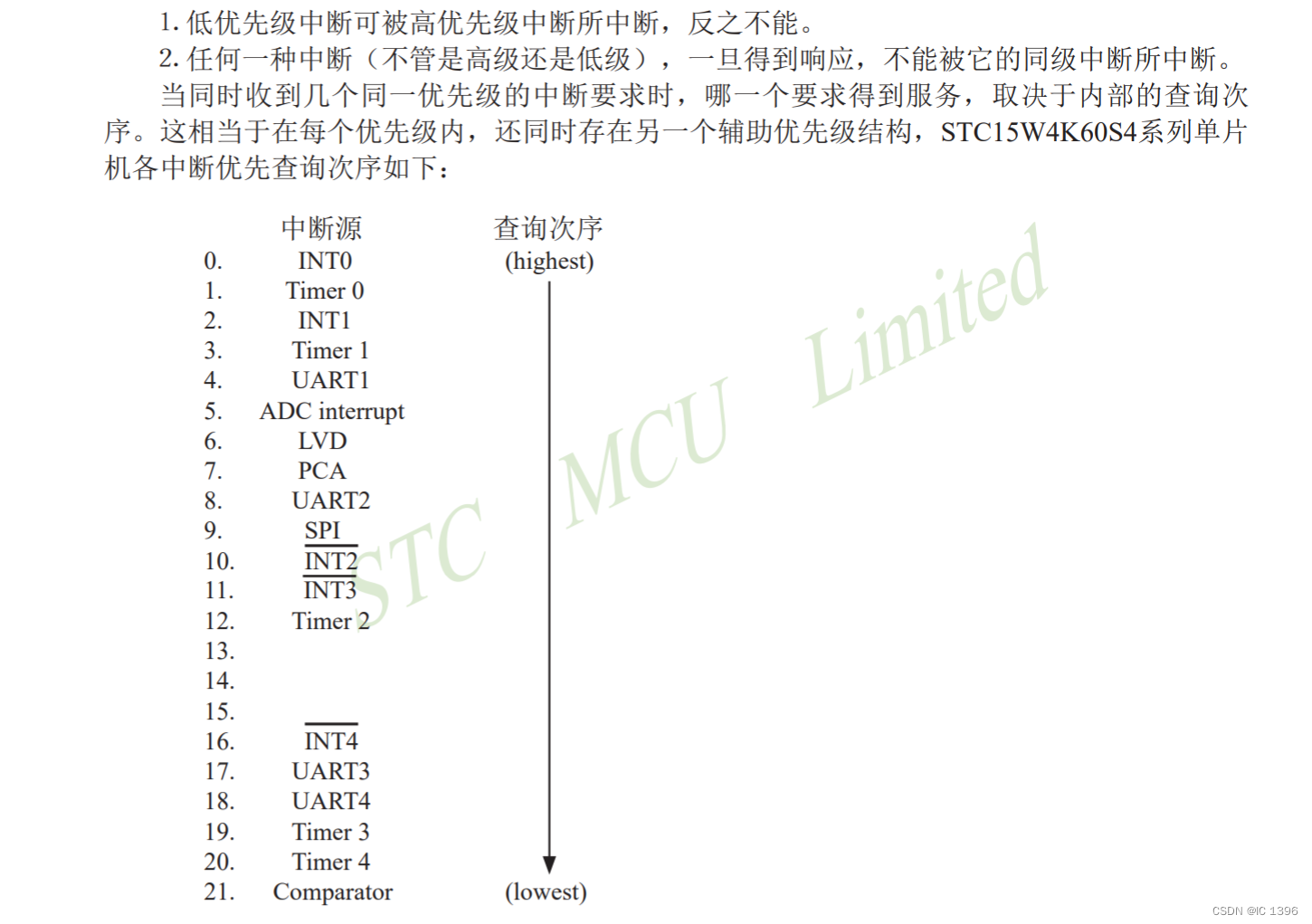

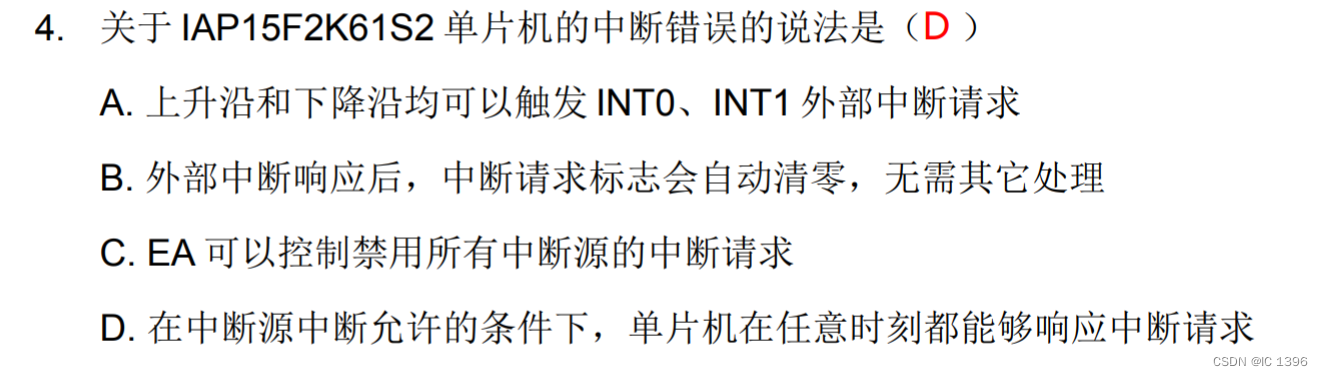

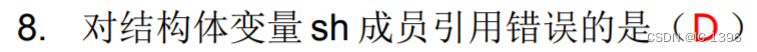

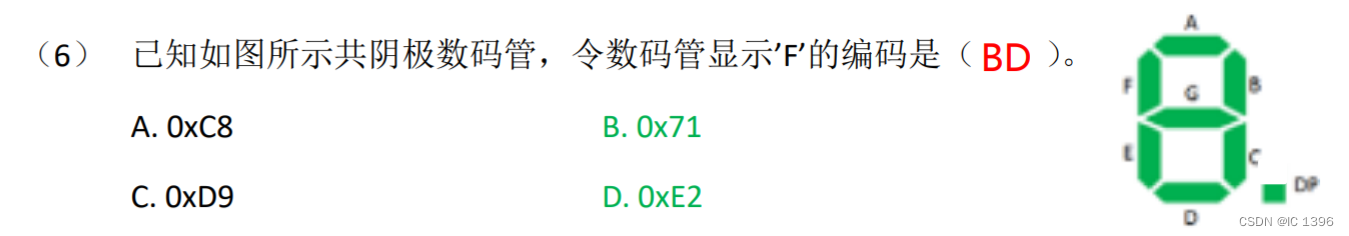

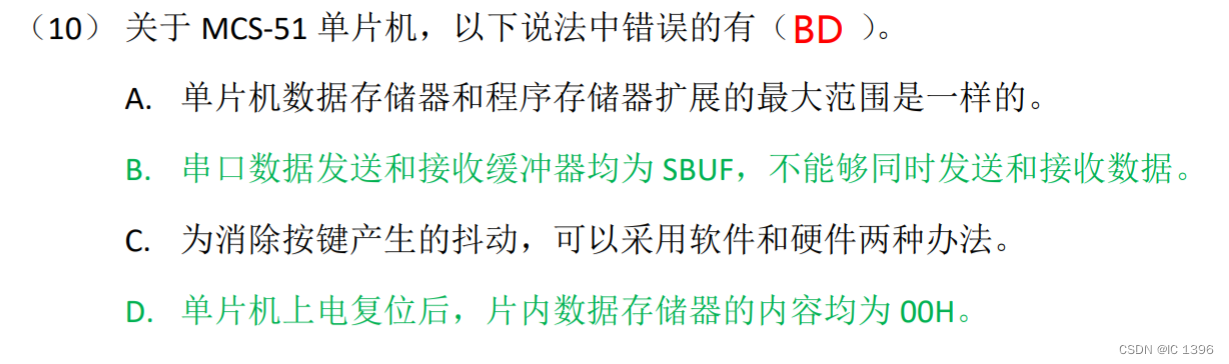

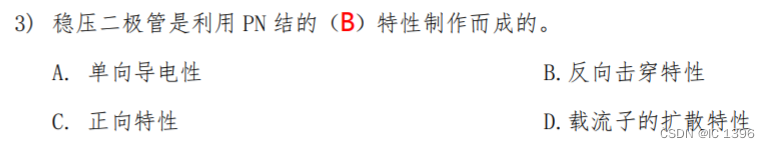

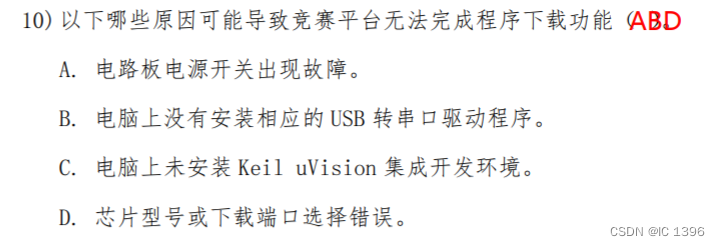

[蓝桥杯单片机]——八到十一届初赛决赛客观题_蓝桥杯单片机历届试题

赞

踩

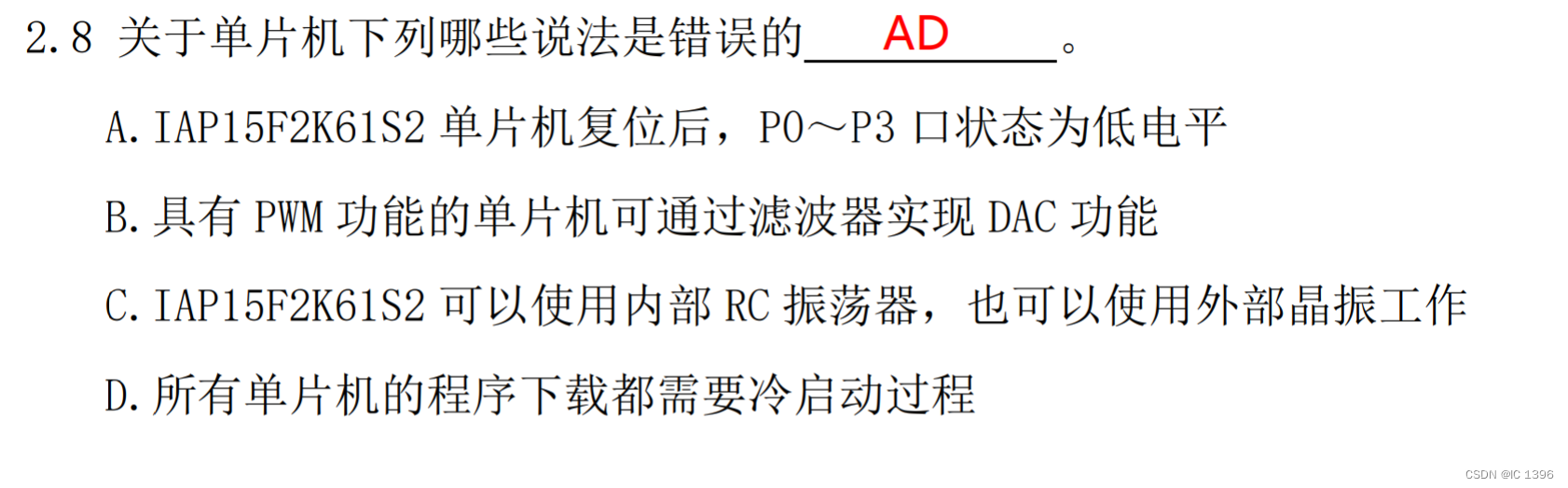

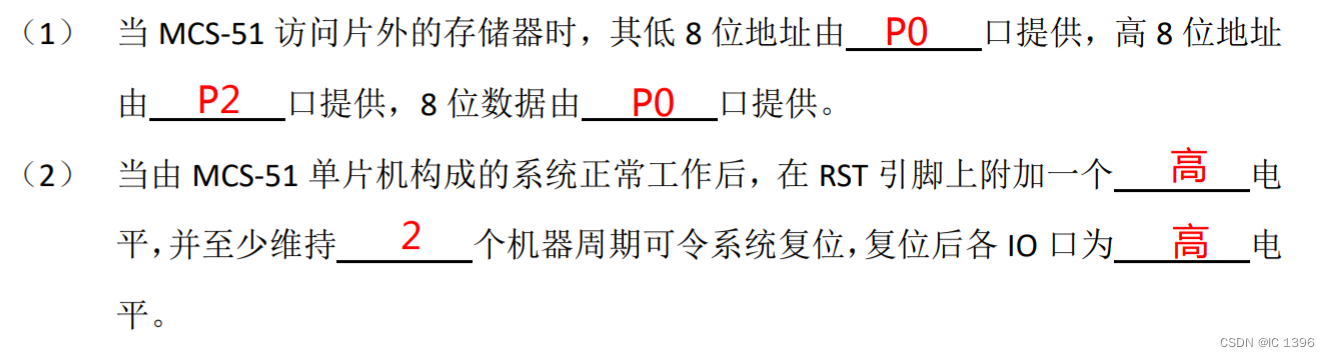

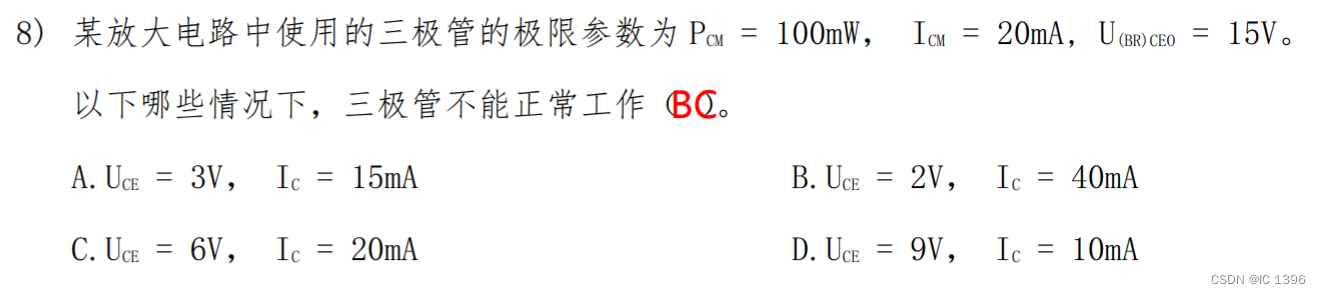

第八届初赛

一、填空题

采用外部12MHz晶振,经过系统12分频时定时器获得最大定时长度,此时定时器定时脉冲为1MHz,周期为1s,而定时器计时均为16位加法计数器,即计时长度为

。

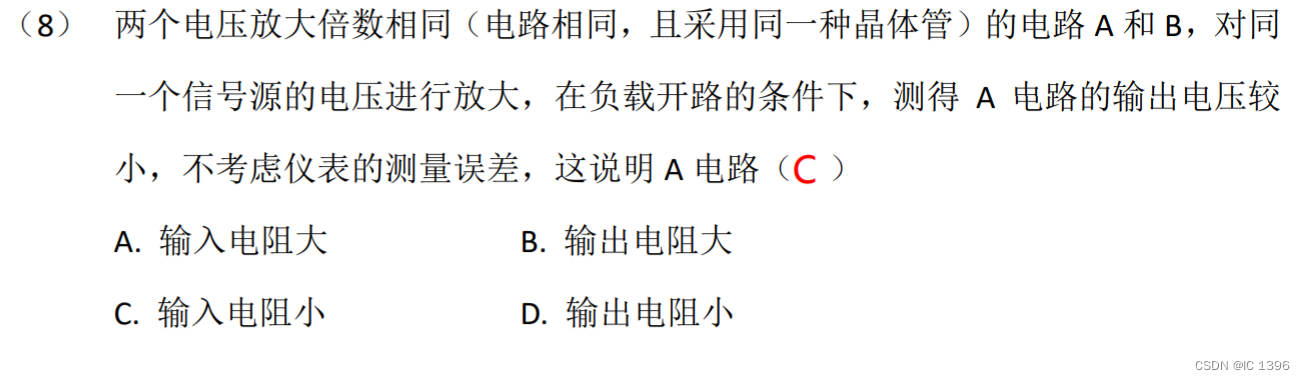

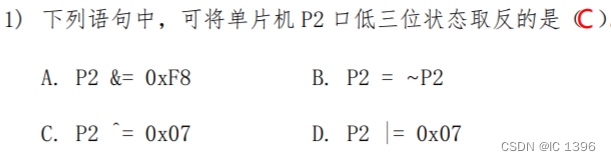

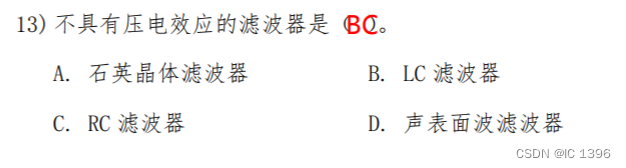

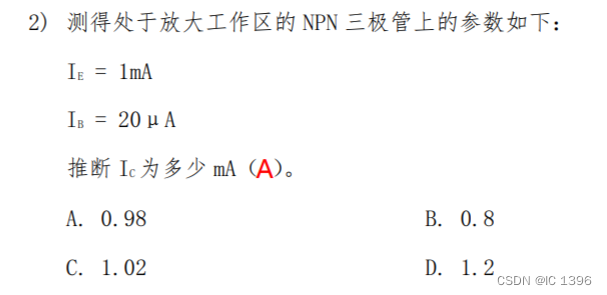

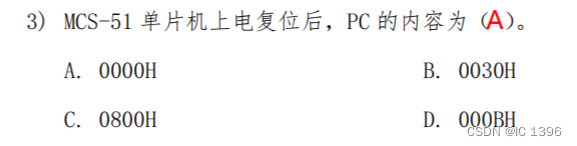

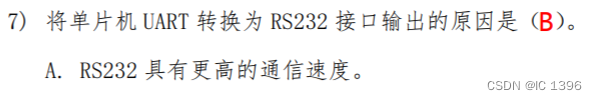

二、 选择题

①带阻滤波器是指能通过大多数频率分量、但将某些范围的频率分量衰减到极低水平的滤波器

②低通滤波器是容许低于截止频率的信号通过, 但高于截止频率的信号不能通过的电子滤波装置

③高通滤波器,又称低截止滤波器、低阻滤波器,允许高于某一截频的频率通过,而大大衰减较低频率的一种滤波器。

④带通滤波器是一个允许特定频段的波通过同时屏蔽其他频段的设备

有用信号为固定频率,应使用带通滤波器,允许特定频段滤波通过

直流电源使用低通滤波器,过滤高频交流信号

TTL与非门输出为推拉式输出电路结构,它们的输出端不能并联使用。如果一个门的输出是高电平而另一个的输出是低电平,则输出端并联以后必然有很大的负载电流同时流过这两个门的输出级,这个电流的数值将远远超过正常工作电流,可能使门电路损坏。因此,不能用来实现线与。而OC门外为集电极开路结构,在工作时需要外接负载电阻和电源。将两个OC结构与非门输出端并联,便不会有电流过大损坏管子的问题。即能够实现线与功能

重置段选代码可以实现消隐功能

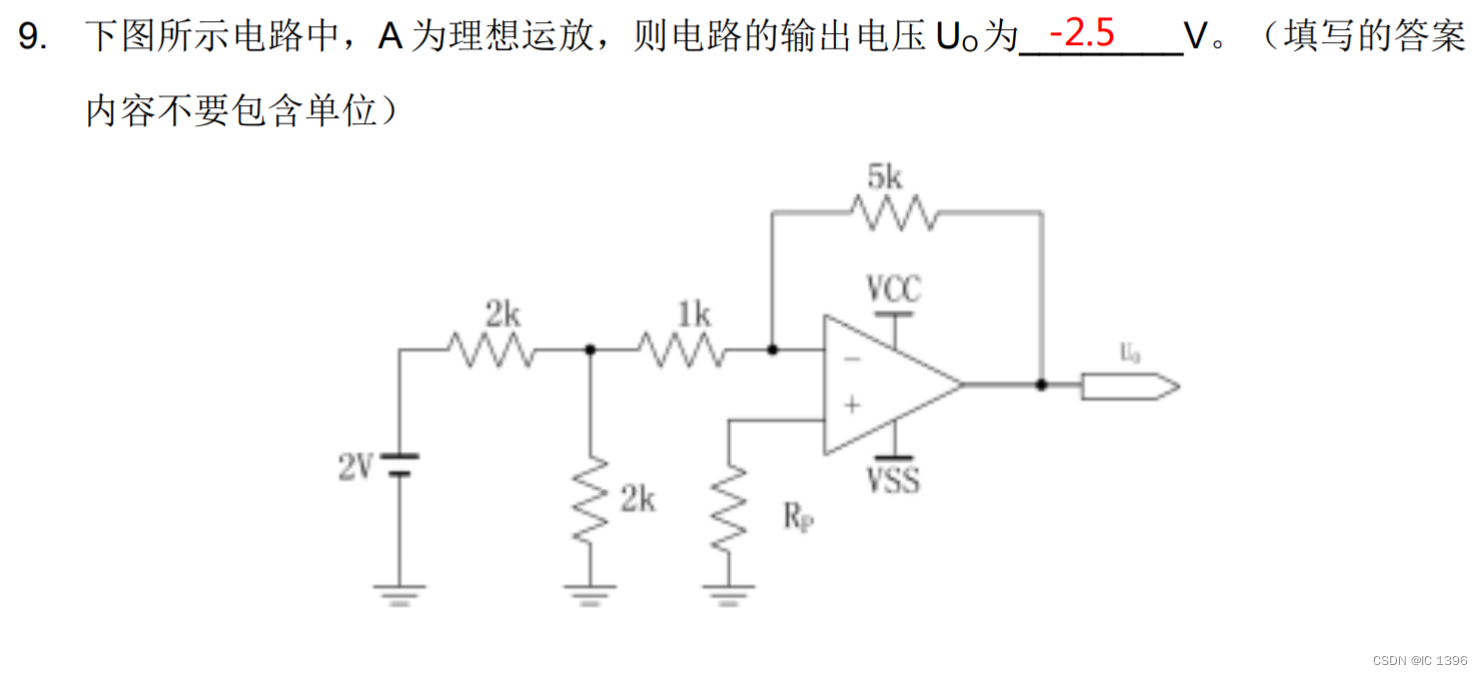

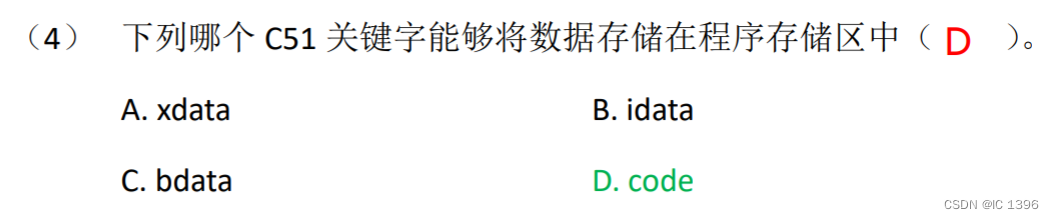

从数据存储类型来说,8051系列有片内、片外程序存储器,片内、片外数据存储器。片内程序存储器还分为直接寻址区和间接寻址区。

①data:将数据存储在0x00 - 0x7f的128B的RAM空间,可以用acc直接读写,速度最快,生成的代码也最少。

②idata:将数据存储在0x00 - 0xff的256B的RAM空间,与data的区别在于访问方式不同,idata数据需要通过间接方式访问。

③xdata:将数据存储在外部0x0000 - 0xffff RAM空间,用DPTR访问。

④pdata:将数据存储在外部扩展RAM的低256字节空间。

⑤code:将数据存储在ROM区域。

⑥bdata:C51自定义语句,非标准C关键字。主要用于定义8位或以上的位访问

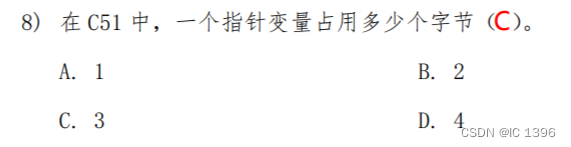

IAP15F2K61S2单片机复位后,P0~P3口状态为准双向/弱上拉模式,

51单片机是高电平复位,复位后各IO端口为高电平

具有PWM功能的单片机可以通过滤波器实现DAC功能

IAP15F2K61S2可以使用内部RC振荡器,也可以使用外部晶振工作

并不是所有单片机的程序下载都需要冷启动的

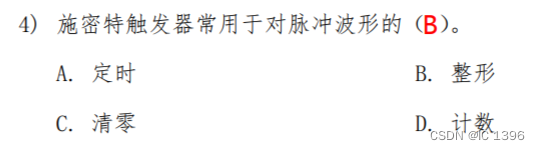

第八届决赛

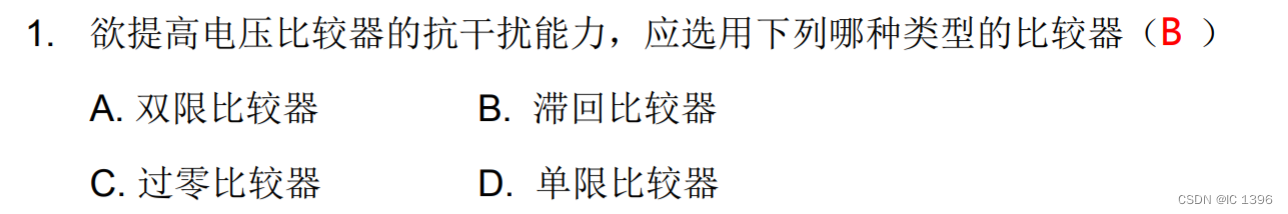

滞回比较器又称施密特触发器,迟滞比较器。这种比较器的特点是当输入信号ui逐渐增大或逐渐减小时,它有两个阈值,且不相等,其传输特性具有“滞回”曲线的形状。

有优先级

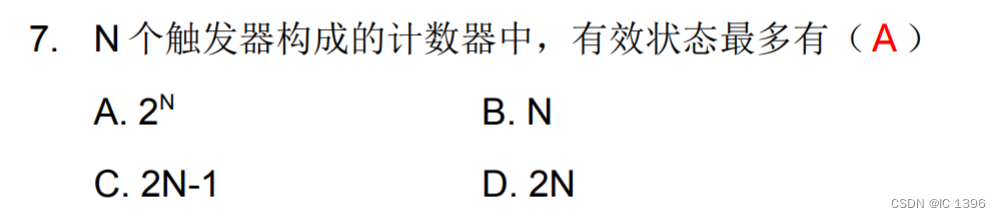

一个触发器可以当成一位,一共N位,则为

一个触发器可以当成一位,一共N位,则为

同第八届省赛2.7

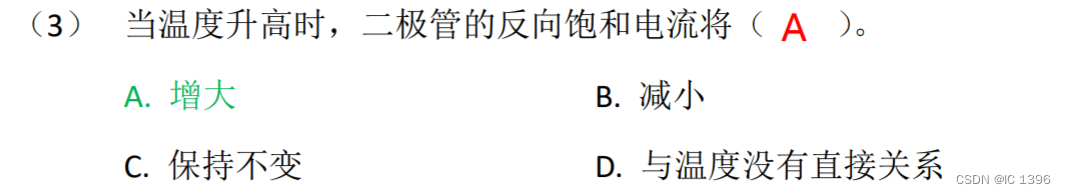

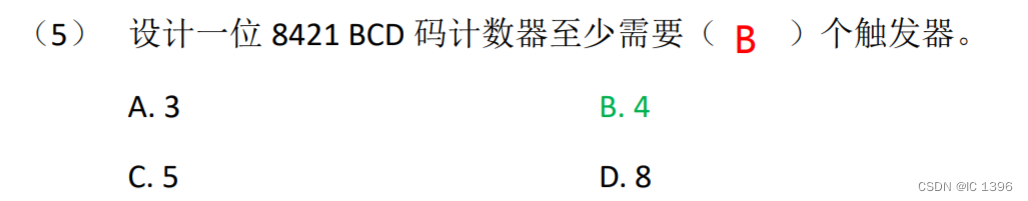

第九届初赛

当二极管加反向电压时,通过 PN 结的只有少数载流子的漂移运动所形成的漂移电流。在常温下,由于少数载流子数目极少,在不太大的反向电压下已全部通过 PN结,因而,即使反向电压再升高,反向饱和电流仍保持很小的数值不变。当环境温度升高时,少数载流子迅速增多,电流也明显增大。

8421码计数器每位十进制数字都要对应四个触发器。如果要设计一位数的加1计数器,就要4个触发器

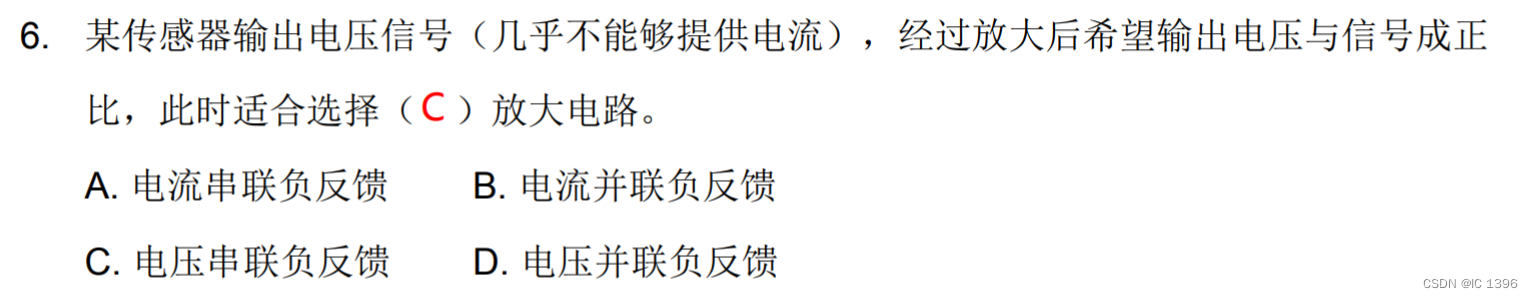

共集电路输入电阻高,输出电阻小 ,且有电压跟随特性

单片机冷启动后(即上电复位),片内RAM为随机值

第九届决赛

一、填空题

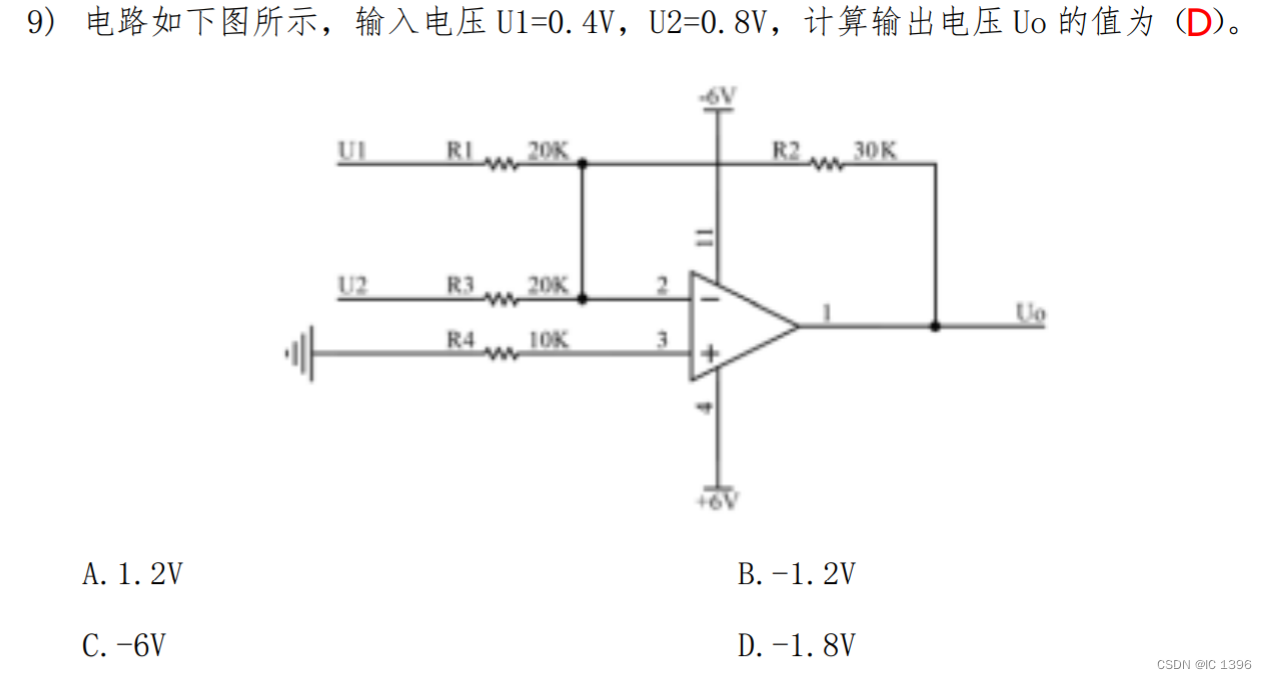

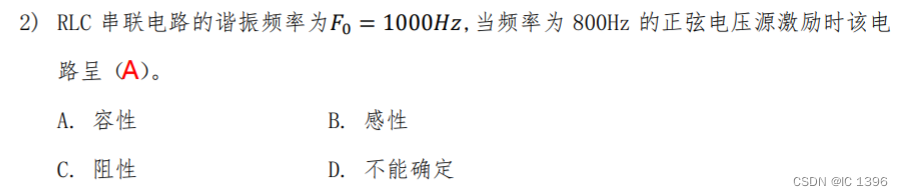

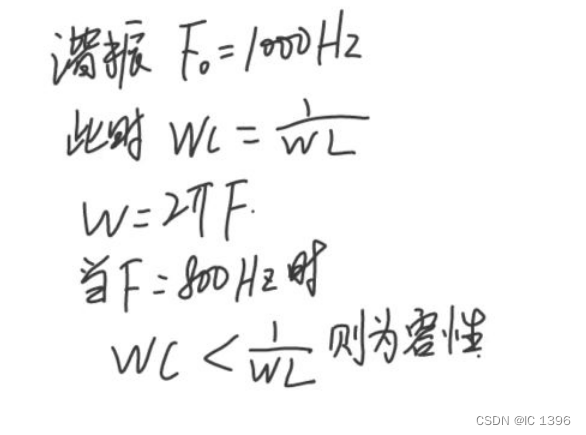

二、选择题

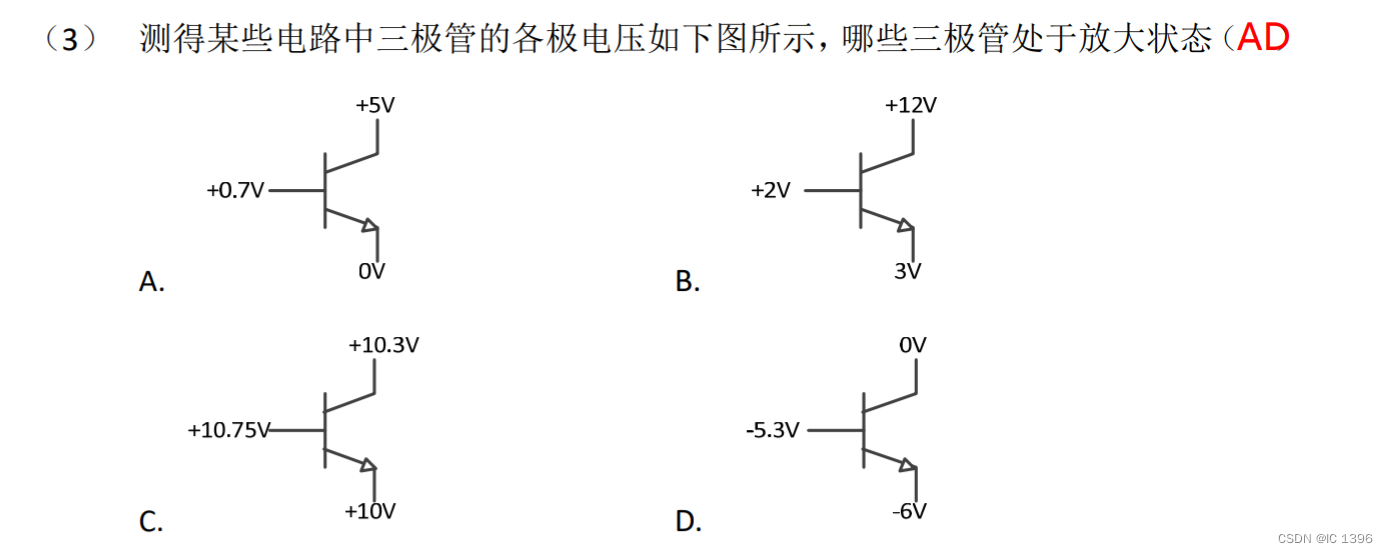

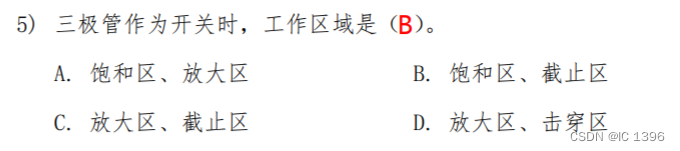

AD放大,B截止,C饱和

![]()

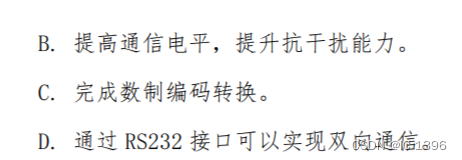

第一个字节表示存储器类型,第二,三个字节是指向数据地址的高字节和低字节

堆栈区存储在RAM区域, 汇编语言还会转换为机器语言,并不会被直接执行

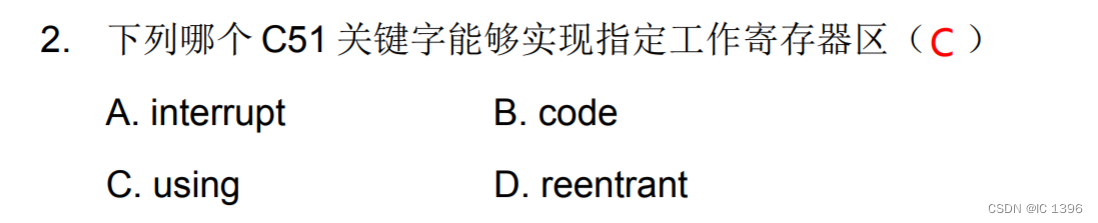

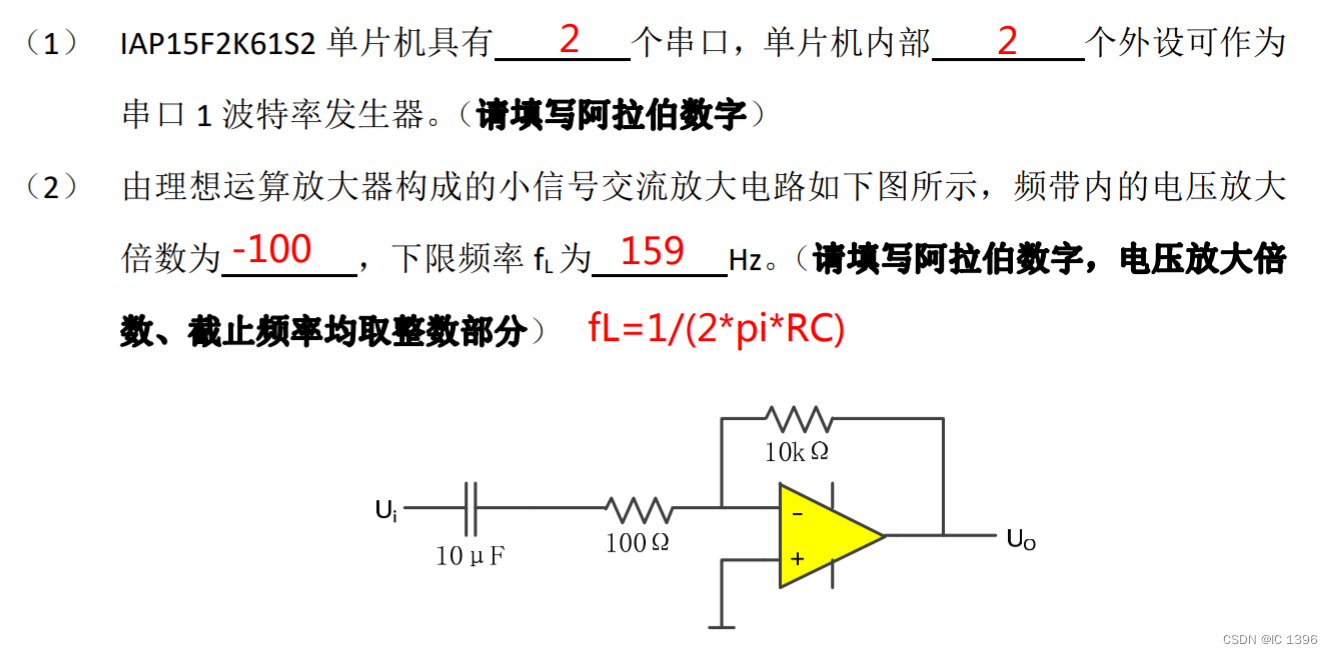

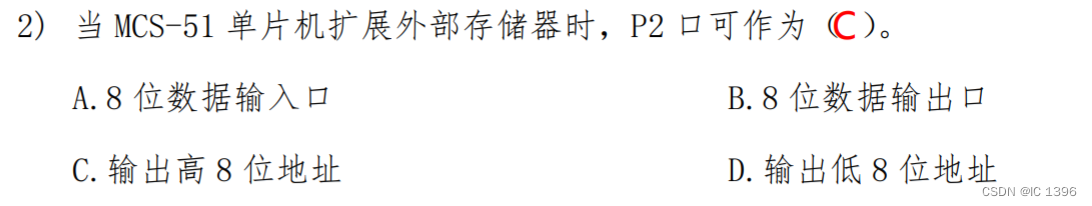

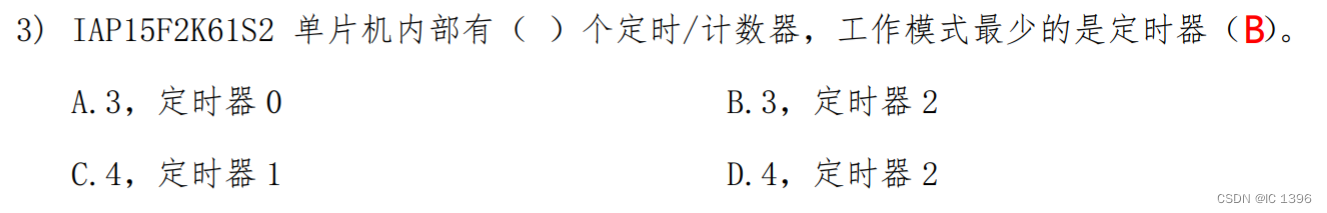

第十届初赛

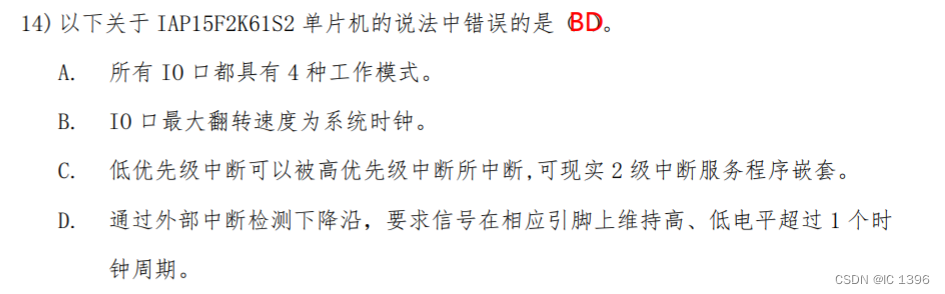

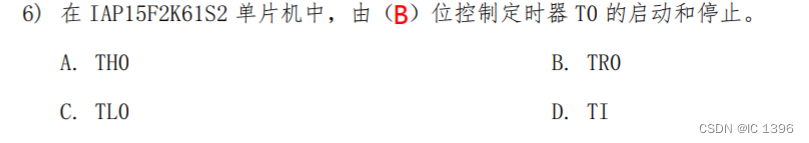

IAP15F2K61S2有3个定时计数器, 定时器0有四种模式,定时器1有三种模式,定时器2固定为16位自动重装载模式

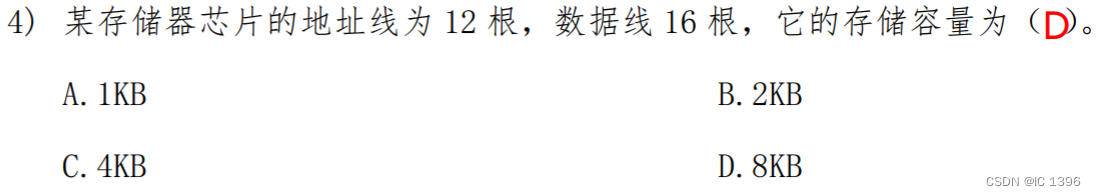

ram芯片的存储容量 =地址线条数×数据线的条数bit = 字数(存储单元个数)×字长。

地址线12根,表示能指示2^12个内存单元;而数据线16根,表明通过数据线每次可以传送16位(每根线每次只能传送1位),即2B(16bit= 2*8bit = 2B),那么可以理解为内存单元的大小等同于数据线每次的传送位数,同样为2B,所以主存容量为2^12*2B=8KB。

TMOD用于设置定时器工作模式

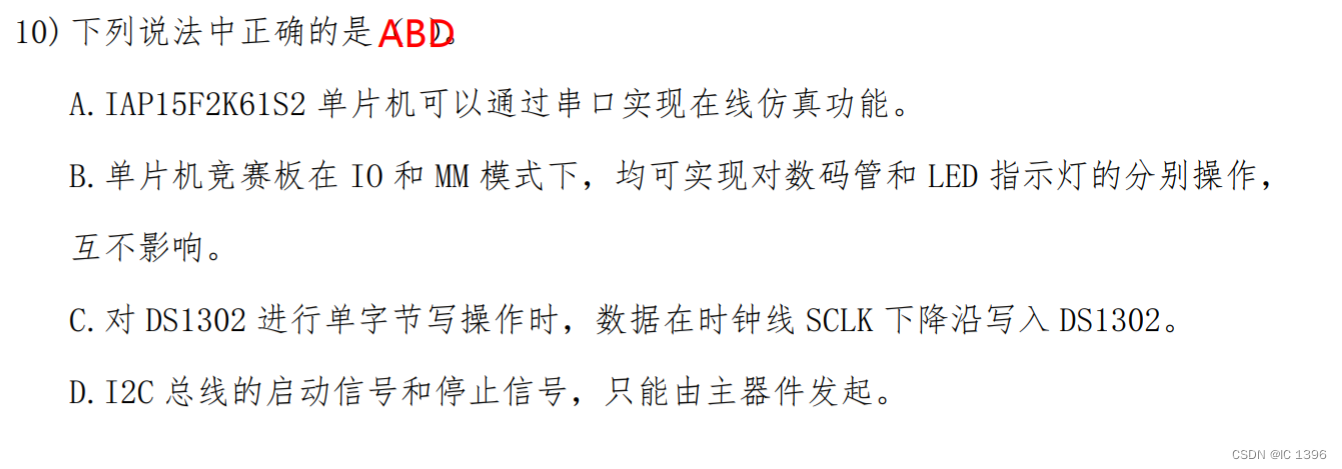

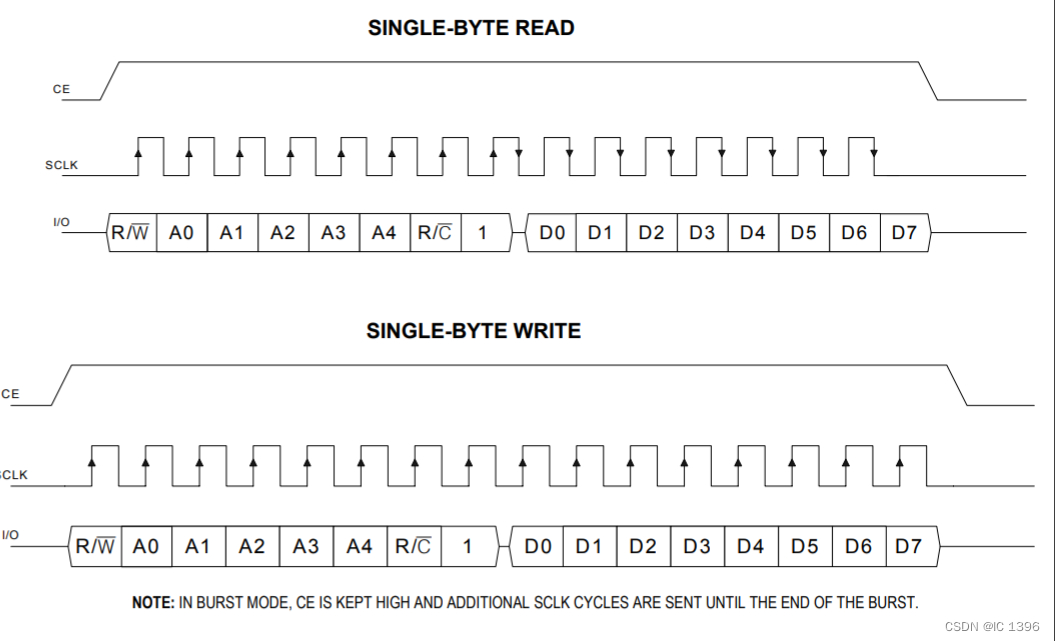

DS1302时序图,单字节写操作时,均是上升沿写入

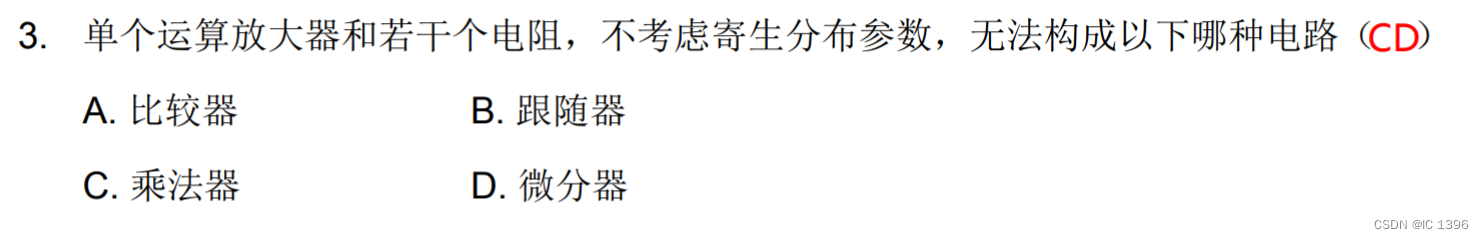

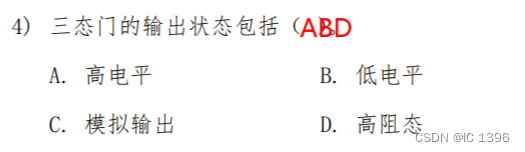

第十届决赛

一、填空题

^=为异或运算符,与0x07异或将低三位取反

三态门是指逻辑门的输出有三种状态:高电平状态、低电平状态、高阻状态。 高阻态的重要作用就是I/O(输入/输出)口在输入时读入外部电平用。

开路电压即为等效电动势

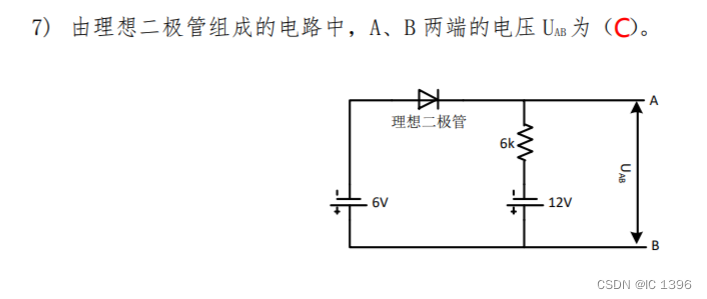

二极管导通,AB两端电压等于第一个电源的电压,不过方向相反,需要加负号

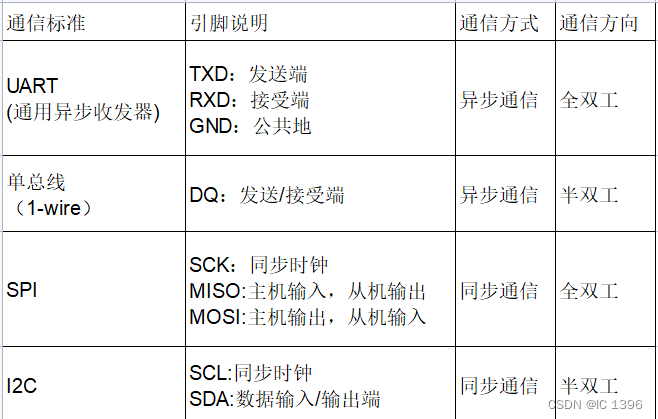

单工: 单工制式下,通信线的一端为发送器,一端为接收器,数据只能按照一个固定的方向传送;

半双工:半双工制式下,系统的每个通信设备都由一个发送器和一个接收器组成,因而数据能从A站传送到B站,也可以从B站传送到A站,但是不能同时在两个方向上传送;(can总线,四线RS485)

全双工:全双工方式下,系统的每端都有发送器和接收器,可以同时发送和接收,即数据可以在两个方向上同时传送。

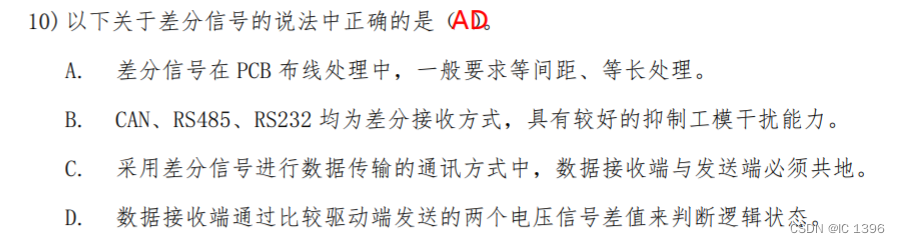

RS232是单端传输方式,差分信号通讯不用共地

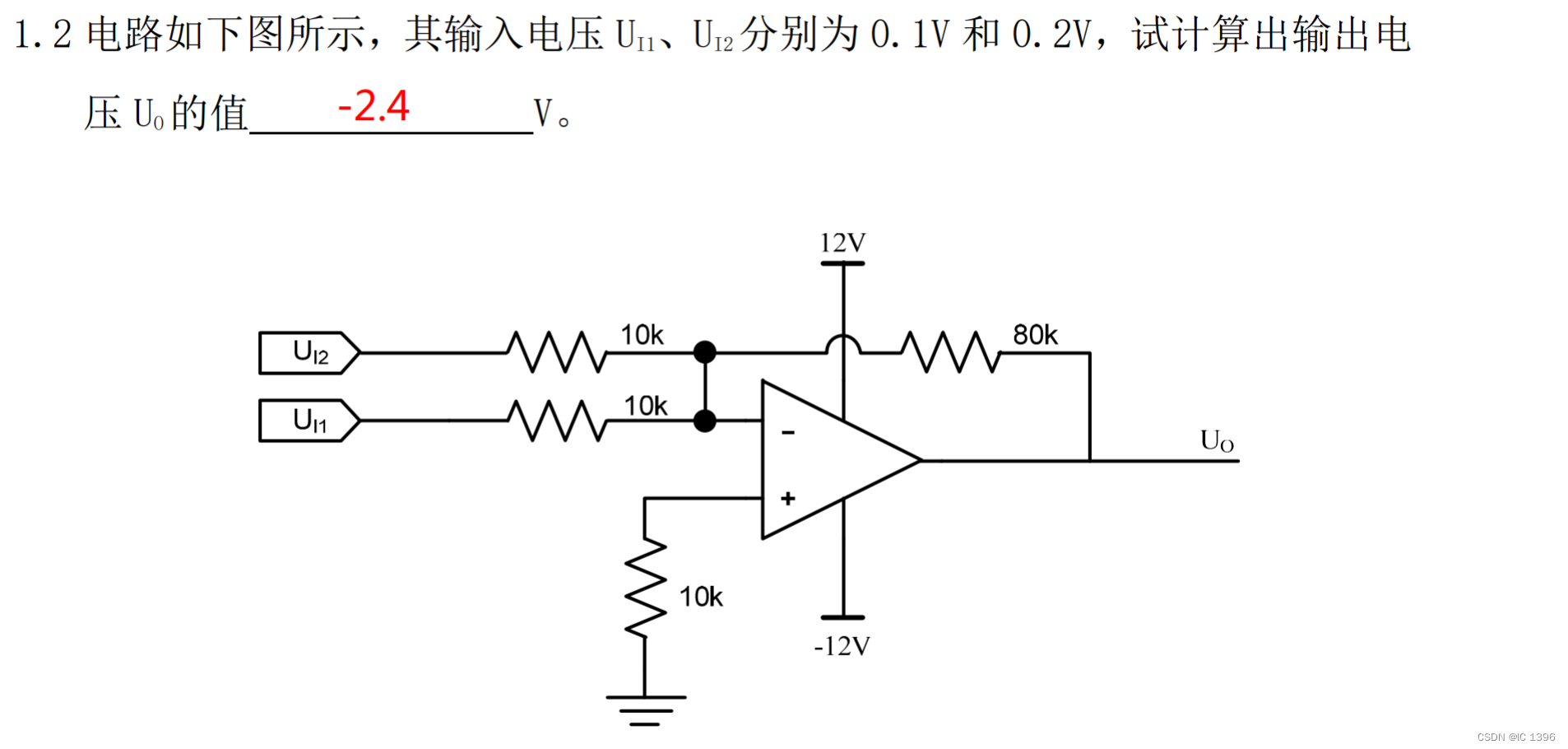

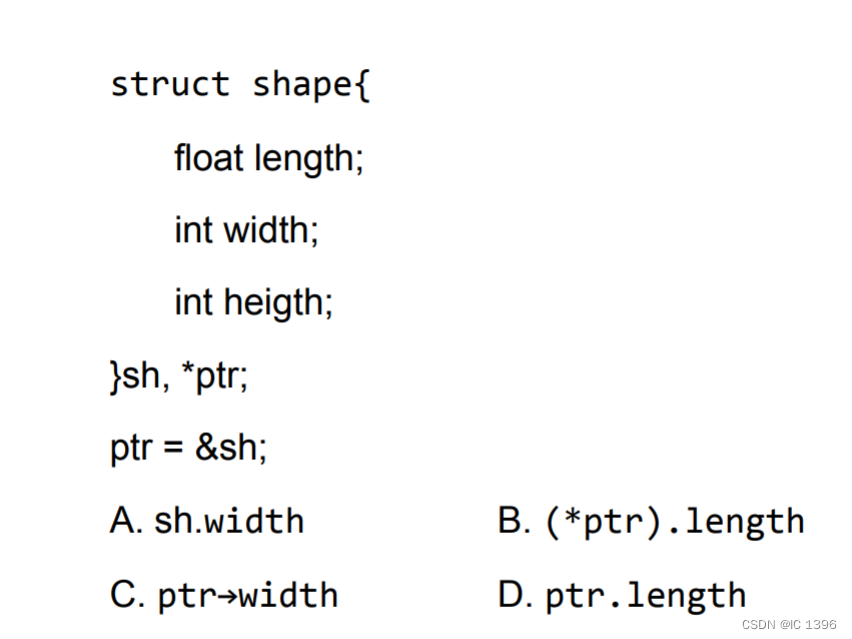

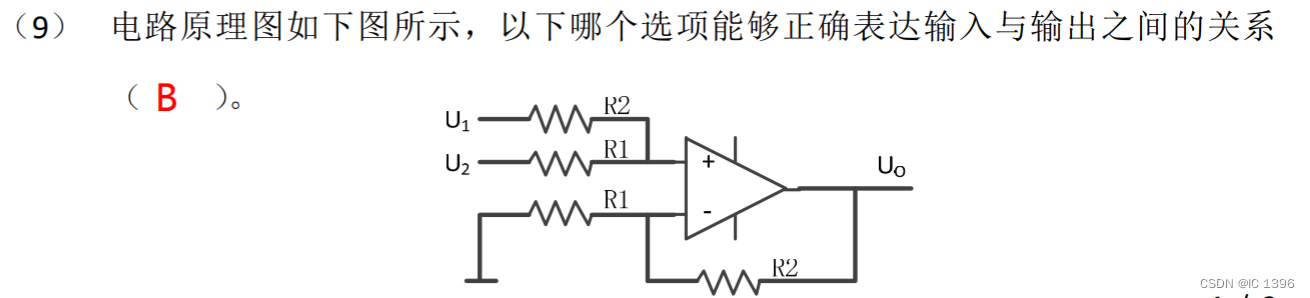

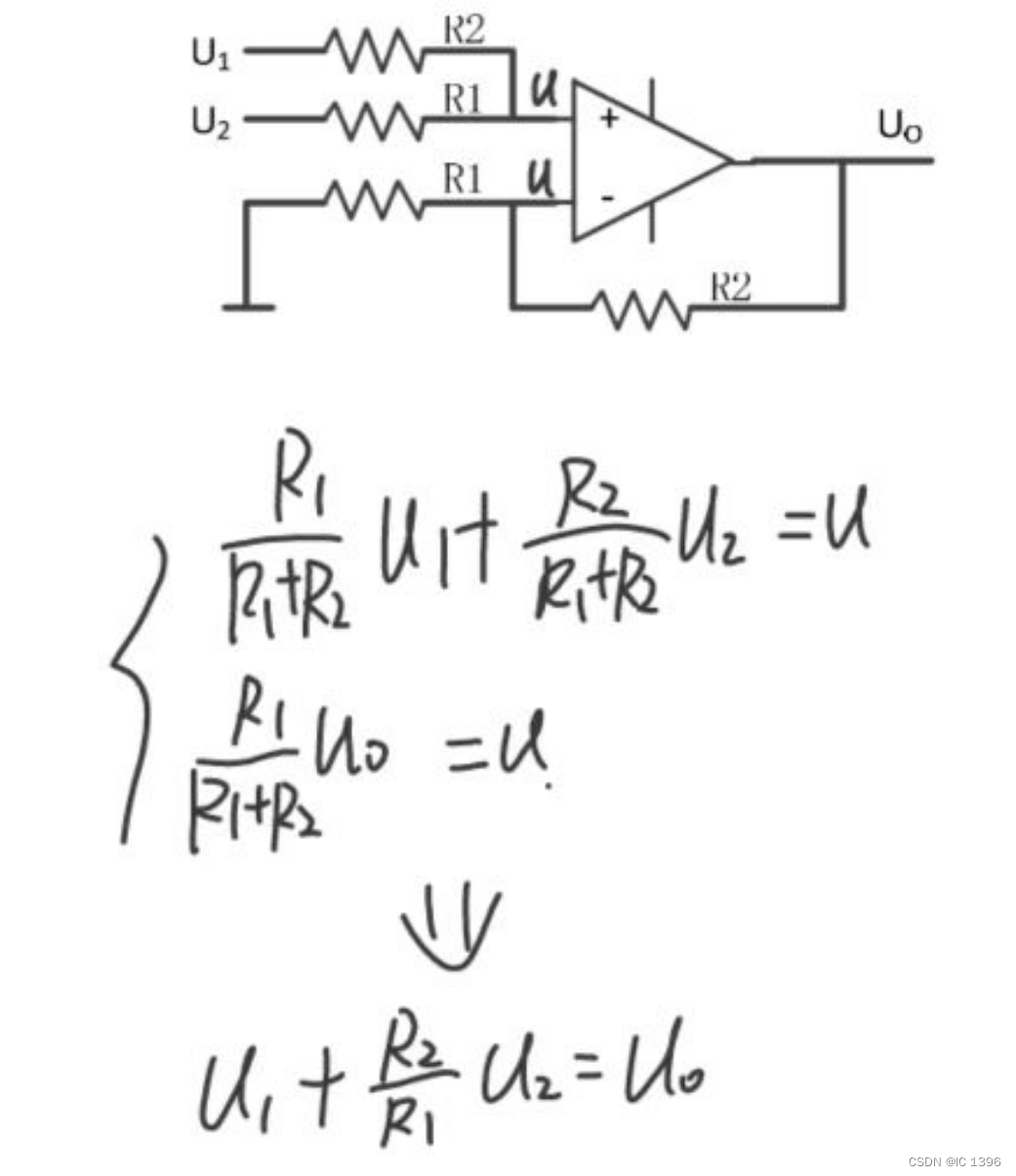

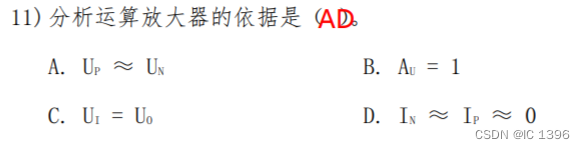

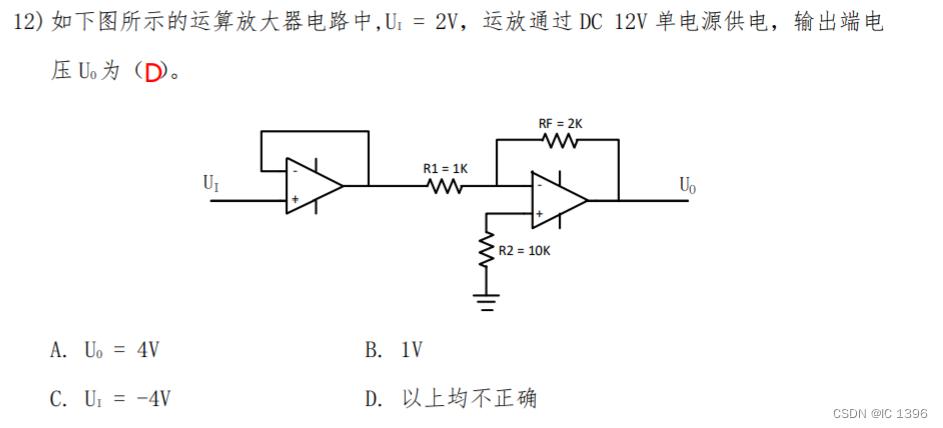

虚短路,虚断开

IO口的最大翻转速度受制于多种因素,其中包括系统时钟频率、IO口控制器支持的最大速度、驱动器的响应速度、传输线的质量和长度等。因此,IO口的最大翻转速度并不完全取决于系统时钟频率。不过,系统时钟频率仍然是影响IO口翻转速度的重要因素之一。

当检测到下降沿时,需要尽快响应外部中断,因此,在适当条件下,可以立即响应中断,而不必一定等待时间。这些条件包括使用合适的抗干扰电路,对信号进行滤波、消除弹跳等措施,以及减少信号上下边沿的上升和下降时间等等。总之,通过外部中断检测下降沿时,要求信号在相应引脚上维持高、低电平超过一个时钟周期并不是必需的,应该根据具体情况来选择是否需要等待时间。

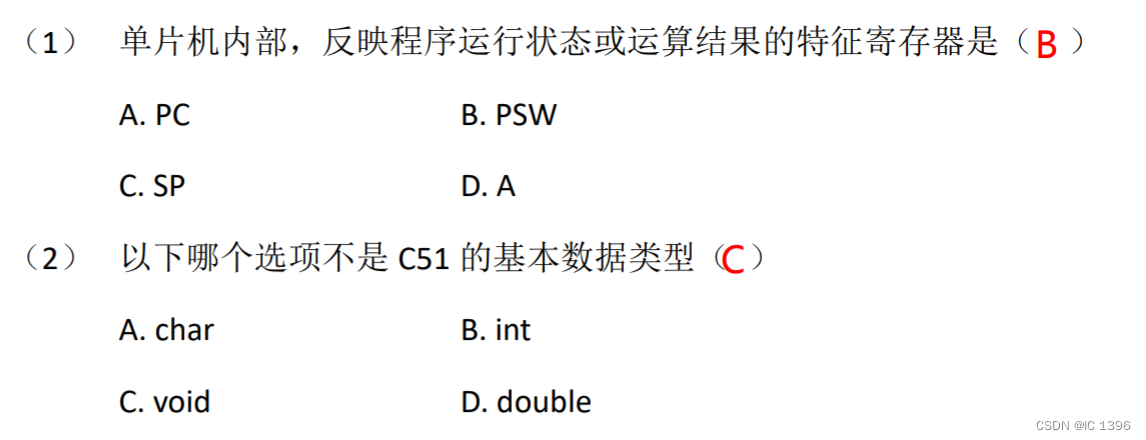

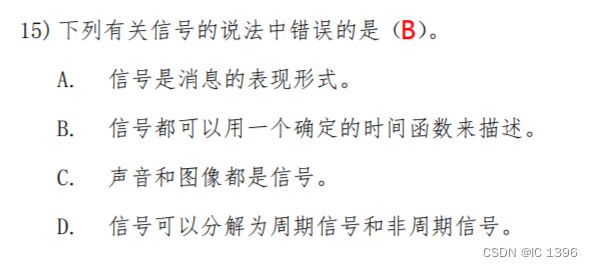

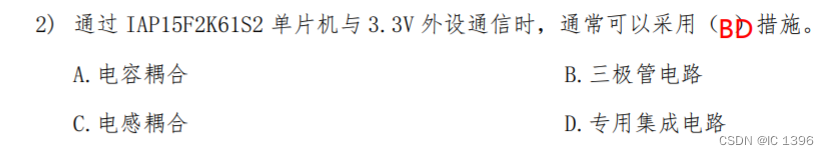

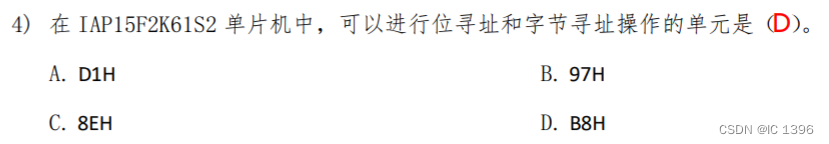

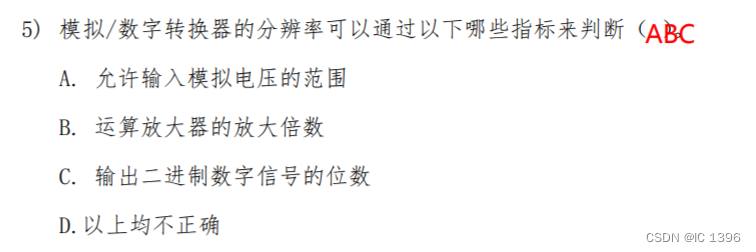

十一届初赛

=16

B8H位于特殊功能寄存器中,能够进行位寻址和字节寻址

时序逻辑电路在逻辑功能上的特点是任意时刻的输出不仅取决于当时的输入信号,而且还取决于电路原来的状态,与以前的输入有关。

![]()

absacc.h代表绝对地址访问的宏定义组,里面包含CBYTE.XBYTE,PBYTE,DBYTE,PWORD,CWORD DWORD七个宏定义。

十一届决赛

八到十一届初赛决赛客观题到这里就结束啦

要是文章有帮助的话,就点赞收藏关注一下啦!

感谢大家的观看

欢迎大家提出问题并指正~