热门标签

热门文章

- 1Flink 内核原理与实现-状态原理_flink state实现

- 2gerrit submit撤回_Gerrit使用篇-提交代码,合并代码

- 3关系抽取(三)实体关系联合抽取:CasRel_最新的实体关系抽取工具

- 4webpack-theme-color-replacer自定义element-ui主题

- 5【Unity】天气特效:打雷下雨_unity落雷特效制作

- 6Cognex VisionPro连接USB相机的两种品牌

- 7极其强大的数据统计软件 Stata 安装教程_如何把stata装到硬盘里面

- 8Oracle使用序列触发器实现主键id自动增长_oracle的id自增序列

- 9蚁剑下载、安装_蚁剑 下载 csdn

- 10AI+AR,二维码还能这么玩儿!优质提示词的12个技巧;LLM学习路径和资料汇总;AI二维码工具大盘点 | ShowMeAI日报_quick qr提示词

当前位置: article > 正文

基于FPGA的流水彩灯_硬件描述语言实验教程彩灯

作者:IT小白 | 2024-06-10 17:14:29

赞

踩

硬件描述语言实验教程彩灯

概述

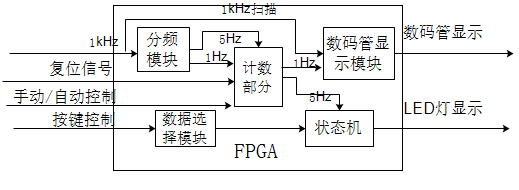

本设计基于超高速硬件描述语言VHDL在Altera公司的实验箱主控板上编程实现,主要由状态机完成对彩灯的控制,并有分频模块分别控制彩灯的循环及数码管的扫描计时,完成彩灯的自动循环、手动控制、清零、及定时功能。

设计任务

1.基本功能:

- 由两位以上输入控制端控制节日彩灯输出花样。

- 输出对应8位彩灯,用LED发光二极管代替。

- 花样可以是:循环左移、循环右移、从中间向两边、从两边往中间等。

- 一位复位信号对流水彩灯进行清零控制。

2.扩展功能:

- 增加手动/自动控制端,手动控制时,由输入控制端控制输出彩灯花样,自动时,按预设花样循环输出。

- 时控功能:在设定时间段自动亮,其他时间自动灭。

- 一位复位信号对计数器进行清零控制。

设计方案

模块设计

1.分频模块

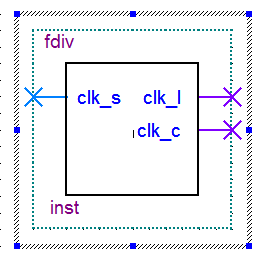

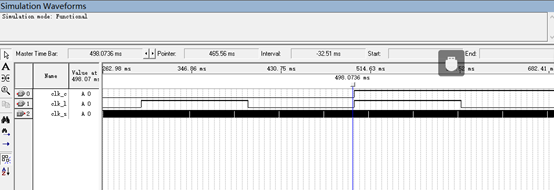

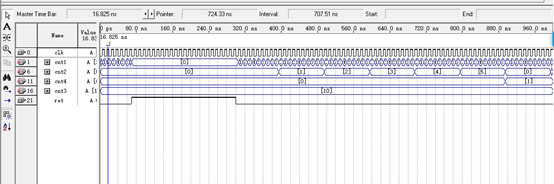

输入1kHz,用于数码管的扫描,又将它分频为1Hz和5Hz两部分,1Hz的用于数码管秒的计时,5Hz的用于彩灯的循环。其中clk_s是1kHz的输入时钟,clk_l是分频为5Hz的输出时钟,clk_c是分频为1Hz的输出时钟。

library ieee; use ieee.std_logic_1164.all; use ieee.std_logic_unsigned.all; entity fdiv is port( clk_s:in std_logic; clk_l,clk_c:out std_logic ); end fdiv; architecture tmp of fdiv is signal cnt1:integer range 0 to 100; signal cnt2:integer range 0 to 500; signal ct,st:std_logic; begin clk_l<=st;clk_c<=ct; process(clk_s) begin if clk_s'event and clk_s='1' then if cnt1<99 then cnt1<=cnt1+1; else cnt1<=0;st<=not st; end if; if cnt2<499 then cnt2<=cnt2+1; else cnt2<=0;ct<=not ct; end if; end if; end process; end;

- 1

- 2

- 3

- 4

- 5

- 6

- 7

- 8

- 9

- 10

- 11

- 12

- 13

- 14

- 15

- 16

- 17

- 18

- 19

- 20

- 21

- 22

- 23

- 24

- 25

- 26

- 27

- 28

- 29

- 30

- 31

- 32

- 33

2.计数模块

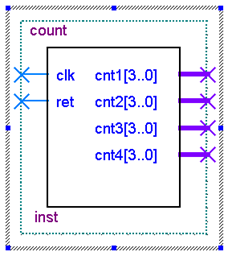

计数器不仅可以用来进行数字计数,用于数码管计时,还可以用来控制有限状态机的转换,进行彩灯的循环花样显示,本设计中单独的计数小模块用于数码管计时三分钟,秒的部分为60进制,分钟部分从0到2,总共计时三分钟,这部分可以修改,只是为了减少拍视屏时间及验证时间,将时间定时为三分钟。其中clk是输入1Hz的分频时钟,ret是计数器清零复位端,cnt1,cnt2,cnt3,cnt4是计数器输出的时间,cnt1:0至9,cnt2:0至5,60秒计数,cnt3使它永远保持为10,在数码管中固定显示为“-”,用于将分钟与秒分隔开,cnt4:0至2,分钟计数。

library ieee; use ieee.std_logic_1164.all; use ieee.std_logic_unsigned.all; entity count is port( clk:in std_logic; cnt1,cnt2,cnt3,cnt4:out std_logic_vector(3 downto 0) ); end count; architecture tmp of count is signal temp1,temp2,temp3,temp4:std_logic_vector(3 downto 0); signal c,c1:std_logic; begin cnt1<=temp1;cnt2<=temp2;cnt3<=temp3;cnt4<=temp4; process(clk) begin if clk'event and clk='1' then temp3<="1010"; if temp1<"1001" then temp1<=temp1+1;c<='0'; else temp1<="0000";c<='1'; end if; end if; end process; process(c) begin if c'event and c='1' then if temp2<"0101" then temp2<=temp2+1;c1<='0'; else temp2<="0000";c1<='1'; end if; end if; end process; process(c1) begin if c1'event and c1='1' then if temp4<"0010" then temp4<=temp4+1; else temp4<="0000"; end if; end if; end process; end;

- 1

- 2

- 3

- 4

- 5

- 6

- 7

- 8

- 9

- 10

- 11

- 12

- 13

- 14

- 15

- 16

- 17

- 18

- 19

- 20

- 21

- 22

- 23

- 24

- 25

- 26

- 27

- 28

- 29

- 30

- 31

- 32

- 33

- 34

- 35

- 36

- 37

- 38

- 39

- 40

- 41

- 42

- 43

- 44

- 45

- 46

- 47

- 48

- 49

- 50

- 51

- 52

- 53

- 54

- 55

- 56

- 57

3.数码管显示模块

用数码管显示时钟并定时控制彩灯的亮灭,可以分为译码部分和扫描部分,译码模块是实现4位二进制计数结果与对应数码管各段编码的转换;扫描子模块则通过扫描信号依次选中数码管,并决定该数码管显示的数字。其中clk_s是1kHz的输入时钟,data1,data2,data3,data4是从计数器输出的二进制时间,dig是数码管的位选端,seg是数码管的段选端。

process(clk_s)

begin

if clk_s'event and clk_s='1' then

cnt<=cnt+1;

end if;

end process;

process(cnt)

begin

case cnt is

when "00"=>dig<="000";d<=data1- 1

- 2

- 3

- 4

- 5

- 6

- 7

- 8

- 9

- 10

推荐阅读

相关标签