热门标签

热门文章

- 1Cloudflare自动检测恶意IP拉黑到防火墙和自动切换5秒盾防CC攻击_cloudflare自动拉黑攻击ip

- 2vue3+element-plus el-form表单组件二次封装(vue3+ts项目)TForm组件新增继承 Element-plus 组件的事件使用及el-input 去除前后空格_vue+element-plus封装form

- 3解析Python中的全局解释器锁(GIL):影响、工作原理及解决方案_python 多线程 gil

- 4FIFO算法_fifo算法详细解释

- 5一元线性回归-python代码_线性回归代码python

- 6时代新宠儿——HEIF图像格式:节省50%空间

- 7Maven依赖排除(exclusion),查看依赖树(mvn dependency:tree),分析依赖项(mvn dependency:analyze)_maven exclusions

- 8记一次完整的uni-app微信小程序开发到上线过程_uniapp开发小程序

- 9微信小程序开发中的推送消息和通知功能_微信小程序 开发接口实时推送

- 10linux搭建vue开发环境,图文详解在Ubuntu 20.04中搭建Vue开发环境

当前位置: article > 正文

FPGA SPI采集ADC7606数据

作者:小蓝xlanll | 2024-06-09 01:20:30

赞

踩

FPGA SPI采集ADC7606数据

一,SPI总线的构成及信号类型

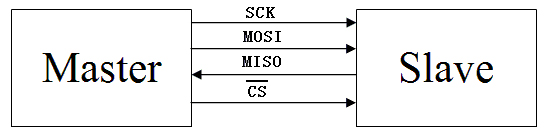

SPI总线只需四条线(如图1所示)就可以完成MCU与各种外围器件的通讯:

1)MOSI – Master数据输出,Slave数据输入

2)MISO – Master数据输入,Slave数据输出

3)SCK – 时钟信号,由Master产生

4)/CS – Slave使能信号,由Master控制。

在一个SPI时钟周期内,会完成如下操作:

1) Master通过MOSI线发送1位数据,同时Slave通过MOSI线读取这1位数据

2) Slave通过MISO线发送1位数据,同时Master通过MISO线读取这1位数据

Master和Slave各有一个移位寄存器,如图4所示,而且这两个移位寄存器连接成环状。依照SCK的变化,数据以MSB first的方式依次移出Master寄存器和Slave寄存器,并且依次移入Slave寄存器和Master寄存器。当寄存器中的内容全部移出时,相当于完成了两个寄存器内容的交换。Master和Slave各有一个移位寄存器,如图4所示,而且这两个移位寄存器连接成环状。依照SCK的变化,数据以MSB first

声明:本文内容由网友自发贡献,不代表【wpsshop博客】立场,版权归原作者所有,本站不承担相应法律责任。如您发现有侵权的内容,请联系我们。转载请注明出处:https://www.wpsshop.cn/w/小蓝xlanll/article/detail/692013

推荐阅读

相关标签