热门标签

热门文章

- 1实操教学|用Serverless 分分钟部署一个 Spring Boot 应用,真香!

- 2色彩校正及OpenCV mcc模块介绍_有mcc的opencv

- 3文本----简单编写文章的方法(中),后端接口的编写,自己编写好页面就上传到自己的服务器上,使用富文本编辑器进行编辑,想写好一个项目,先分析一下需求,再理一下实现思路,再搞几层,配好参数校验,lomb

- 4【Flink实战系列】Flink+kafka+redis 实时计算 wordcount_flink 读写redis

- 5【ViViT】A Video Vision Transformer 用于视频数据特征提取的ViT详解_视频vit

- 6数据结构之——简说链表

- 7【专题】2024中国汽车业人工智能行业应用发展图谱报告合集PDF分享(附原数据表)...

- 8浅谈Nginx负载均衡原理与实现_nginx 负载均衡 必须在局域网吗为什么

- 9二、Neo4j的使用(知识图谱构建射雕人物关系)

- 10推荐9个好玩的AI作图网站_mental ai

当前位置: article > 正文

FPGA实现CLAHE算法(Verilog)

作者:Monodyee | 2024-04-08 20:54:57

赞

踩

FPGA实现CLAHE算法(Verilog)

在介绍CLAHE算法之前必须要先提一下直方图均衡化,直方图均衡化算法是一种常见的图像增强算法,可以让像素的亮度分配的更加均匀从而获得一个比较好的观察效果。

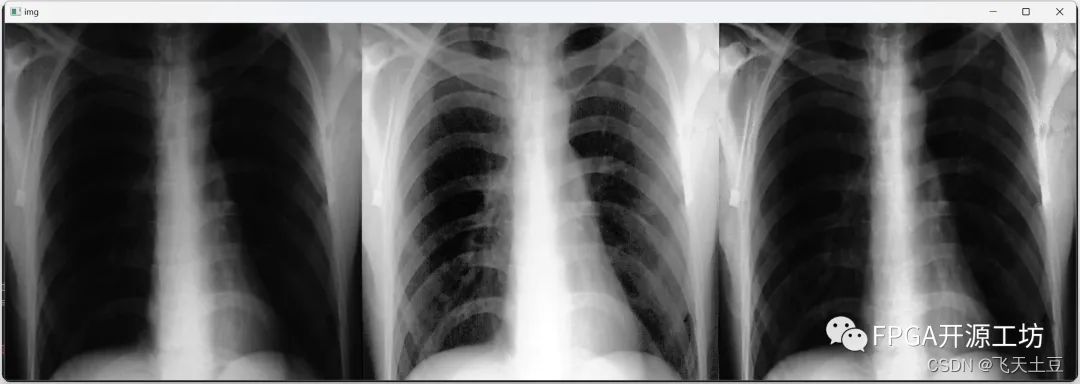

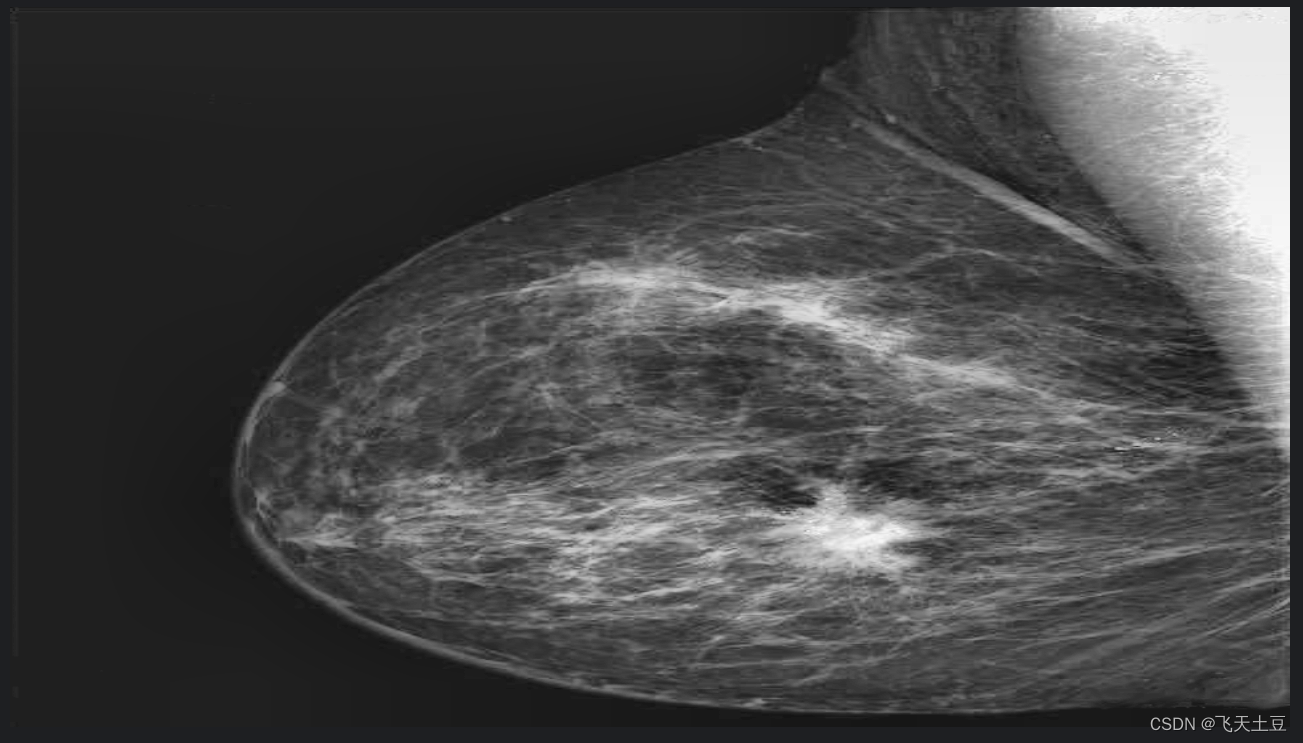

左边是原图,右边是经过直方图均衡化后图,可以看到肋骨什么的可以更加清晰的显示了出来,能够更好的观察到肋骨等位置的细节。

但是美中不足的是总感觉有的地方太亮了,干扰到了我们的观察。

这是因为直方图均衡化有着两个问题:

直方图均衡化是针对全局进行处理的,所以当局部出现过亮或者过暗的时候就会影响效果。

直方图均衡化会增强噪声。

再来看看经过CLAHE算法后的效果。

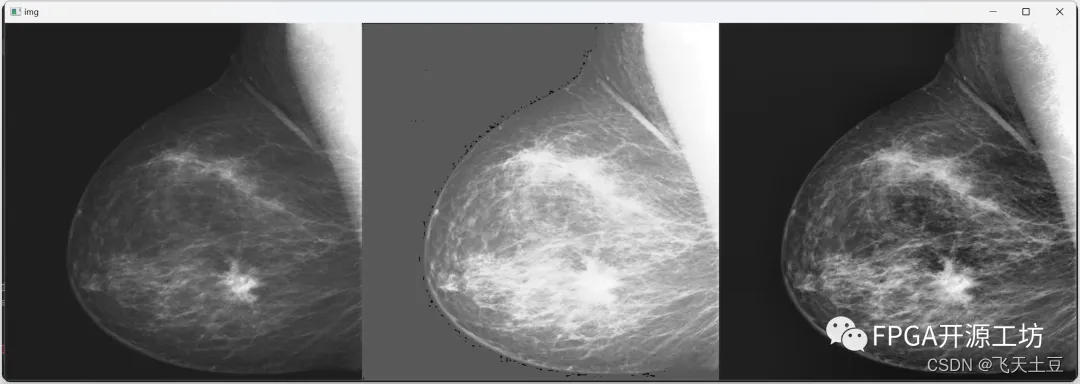

最左侧为原图,中间为直方图均衡化后的结果,最右侧为CLAHE算法的效果。

从视觉效果上来看,CLAHE算法的效果最为明显。

CLAHE算法针对上面两个问题,提出了相应的解决方案:

CLAHE会将图像分成一个一个的小块,这样在局部进行直方图均衡化。

针对背景噪声增强的问题,CLAHE算法应用了限制对比度的方法。

CLAHE算法的实现步骤分为以下三个部分:

-

对图像进行分块

-

对每个块进行直方图均衡化和限制对比度

-

使用插值的方法得到最后增强的图片

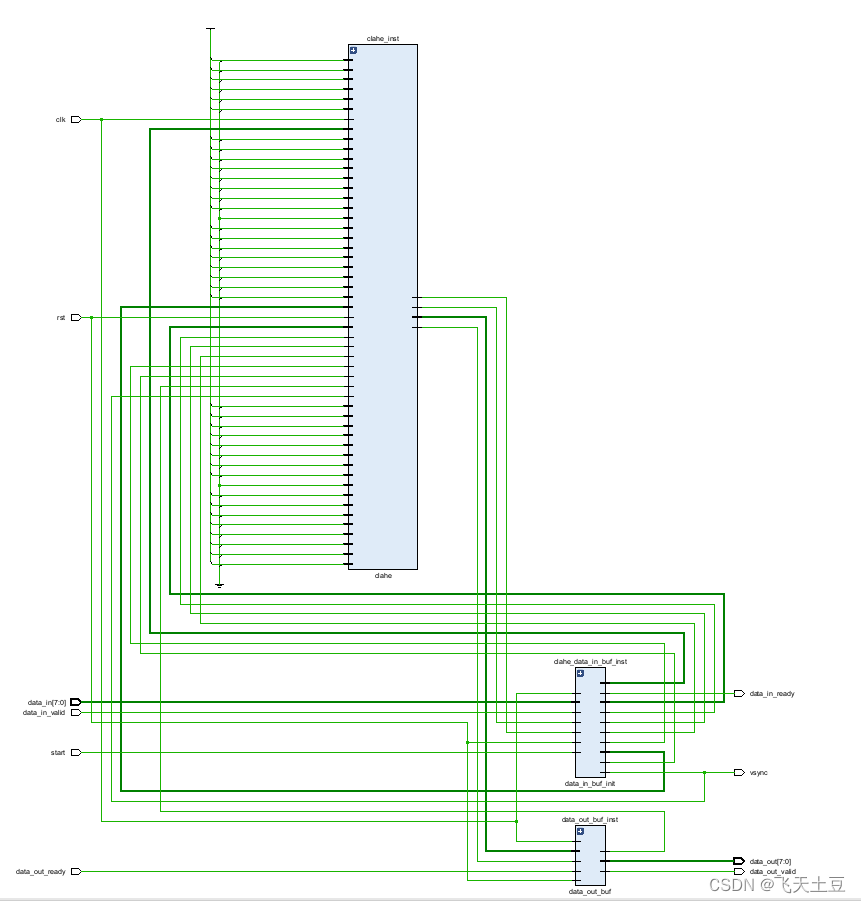

使用FPGA实现CLAHE算法可以分为以下模块:

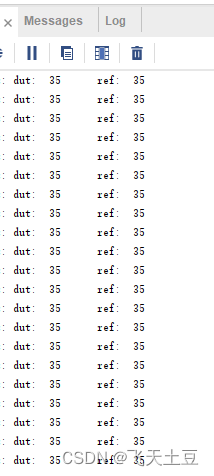

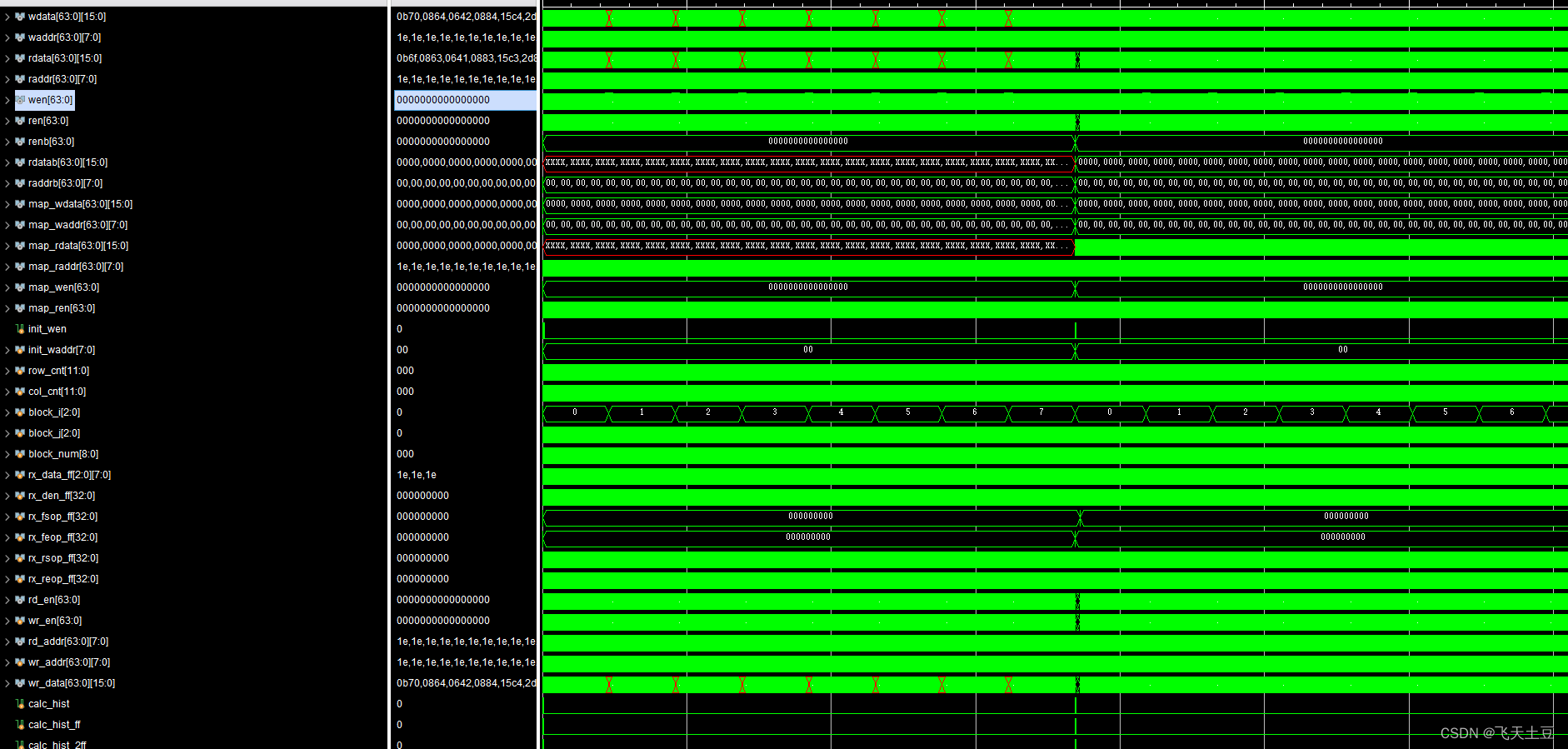

仿真时打印的部分数据:

FPGA仿真结果图

声明:本文内容由网友自发贡献,不代表【wpsshop博客】立场,版权归原作者所有,本站不承担相应法律责任。如您发现有侵权的内容,请联系我们。转载请注明出处:https://www.wpsshop.cn/w/Monodyee/article/detail/388157

推荐阅读

相关标签