- 1CrossOver for Mac 24.0.0 (mac类虚拟机运行Windows软件)

- 2致远互联的下一步:从“协同”到“门户”

- 3如何开发一个chrome浏览器插件_浏览器插件开发

- 4龙蜥社区首次突破!高性能存储 SIG 现身 LSF/MM/BPF 2023 分享 EROFS 的演进路线_中国存储文件系统峰会2023lsf

- 5内网服务器实现共享上网_redirect host(new nexthop

- 6小程序基础入门(黑马学习笔记)_黑马微信小程序笔记

- 7Android Studio 4.2 新变化_androidcomponents onvariants

- 8C#上位机与omron欧姆龙 Fins TCP通信以太网通讯实例 源码通过和PLC用网络连接_c# finstcp

- 9华为数通 HCIP-Datacom H12-831 题库补充

- 10ELF格式文档详解_elf geshi wendang

FPGA LUT查找表原理和编程方式

赞

踩

一、查找表

LUT就是查找表,对于4输入的LUT而言,实际上就是4位地址位,一位数据位的存储器,能够存储16位数据,所以我们在FPGA设计中可以用LUT组建分布式的RAM。

这样也可以解释我们在设计中为什么要采用流水线的实现方法

因为当输入数据的位数远大于一个LUT的输入时,就需要用多个LUT级联来实现逻辑,那么级联产生的延时也就不可避免了,这样就会制约系统的运行频率。那么为了避免级联数过于多,就采用插入寄存器的方法来实现。

举一个简单的例子,如果要实现一个6*1的mux可以用一个6输入的LUT或者是2个4输入的LUT来实现,6输入的LUT相当于是6位地址线一位数据位,能够存储64bit的数据,而采用两个4输入的LUT的话,它的总容量大小为32位数据。

如果用6输入的LUT实现4输入LUT的功能,那么就浪费了1-16/64=75%的资源,所以采用少输入的LUT可以更好的节省面积和资源,但是呢如果LUT采用的是2输入的呢,那样岂不是更好吗,不是的,因为对于多输入的信号处理的时候,就需要有多个LUT的级联来实现,而级联有不可避免的会导致延时过分,导致时序不满足。因此在实际的FPGA产品中多采用的是4输入或者6输入的LUT。

图 4输入的LUT

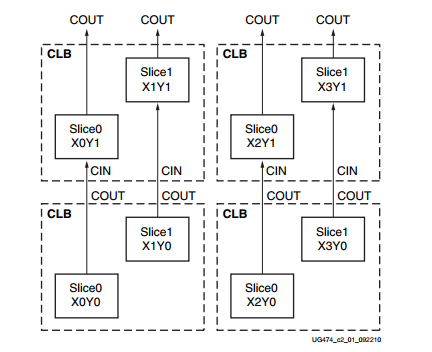

CLB是xilinx基本逻辑单元,每个CLB包含两个slices,每个slices由4个(A,B,C,D)6输入LUT和8个寄存器组成(中间应该还有一些选择器、与非门、或非门之类的东西)。放一个slices的内部图

同一CLB中的两片slices没有直接的线路连接,分属于两个不同的列。每列拥有独立的快速进位链资源。

slice分为两种类型 SLICEL, SLICEM

(1)SLICEL可用于产生逻辑,算术,ROM。

(2)SLICEM除以上作用外还可配置成分布式RAM或32位的移位寄存器。每个CLB可包含两个SLICEL或者一个SLICEL与一个SLICEM.

分布式RAM

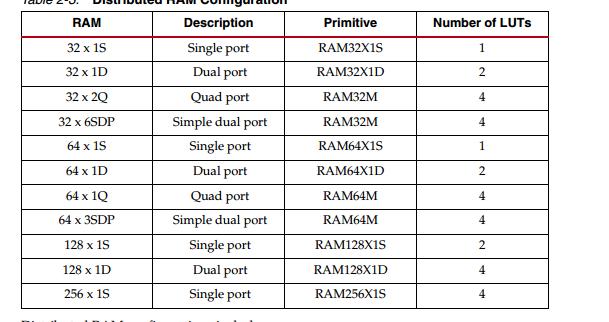

SLICEM可以配置成分布式RAM,一个SLICEM可以配置成以下容量的RAM

多bit的情况需要增加相应倍数的LUT进行并联。

分布式RAM和 BLOCK RAM的选择遵循以下方法:

1. 小于或等于64bit容量的的都用分布式实现

2. 深度在64~128之间的,若无额外的block可用分布式RAM。 要求异步读取就使用分布式RAM。数据宽度大于16时用block ram.

3. 分布式RAM有比block ram更好的时序性能。 分布式RAM在逻辑资源CLB中。而BLOCK RAM则在专门的存储器列中,会产生较大的布线延迟,布局也受制约。

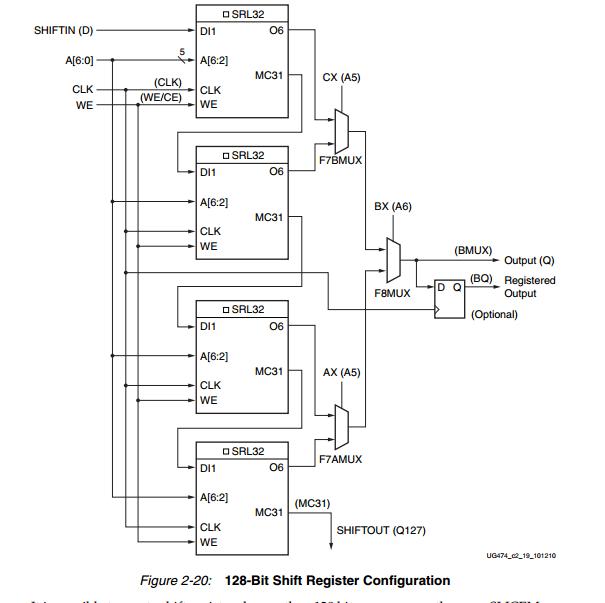

移位寄存器(SLICEM)

SLICEM中的LUT能在不使用触发器的情况下设置成32bit的移位寄存器, 4个LUT可级联成128bit的移位寄存器。并且能够进行SLICEM间的级联形成更大规模的移位寄存器。

MUX

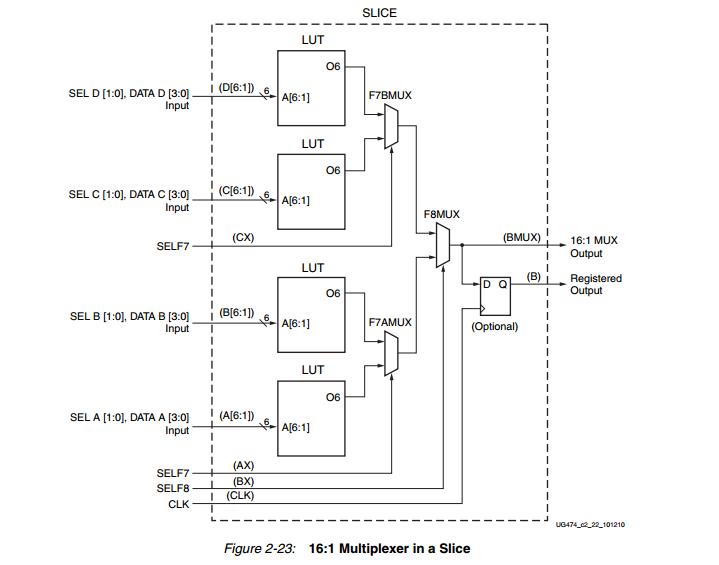

一个LUT可配置成4:1MUX.

两个LUT可配置成最多8:1 MUX

四个LUT可配置成16个MUX

同样可以通过连接多个SLICES达成更大规模设计,但是由于SLICE没有直接连线,需要使用布线资源,会增加较大延迟。

进位链

每个SLICE有4bit的进位链。每bit都由一个进位MUX(MUXCY)和一个异或门组成,可在实现加法/减法器时生成进位逻辑。该MUXCY与XOR也可用于产生一般逻辑。

设计中我们可以用vivado查看设计底层的LUT实现图,具体的差看方法https://blog.csdn.net/qijitao/article/details/51371434

二、LUT实现原理

LUT中文名字叫查找表。以7系列的FPGA为例,每一个Slice里面有四个LUT。FPGA就是通过LUT实现大量的组合逻辑,以及SLICEM里面的LUT还可以构成RAM,Shift Register,以及Multiplexers。这篇文章我们一起来学习LUT如何构成组合逻辑。

LUT,中文名字叫做查找表,其原理其实也就是一个一个查找表,根据输入去找到相应位置的信号,然后做输出。说白了就好像一个小容量的ROM,把输入当作地址信号,对LUT里面预存的内容进行寻址。

7系列的FPGA的LUT有6个输入端口(A1-6),然后有两个输出端口(O5,O6)。下图是SLICEL里面的LUT。

其可以实现6输入的布尔组合逻辑函数,输入信号为A1,A2,A3,A4,A5,A6,输出端口为O6。如下

O6=f(A1,A2,A3,A4,A5,A6)

其实现方式就是将输入(A1,A2…A6)对应的输出在LUT里面预存好(这一步在我们用bit文件配置FPGA时实现),然后把输入信号当作地址信号去把对应的输出信号调出来。

同样其还可以构成两个5输入的布尔组合逻辑函数,其中这两个函数共用5个输入信号(A1,A2,A3,A4,A5),A6被拉高,O5,O6分别是两个布尔逻辑的输出。

O5=f(A1,A2,A3,A4,A5)

O6=f(A1,A2,A3,A4,A5)

故这也相当于实现的是一个5输入2输出的逻辑函数。

[O5,O6]=f(A1,A2,A3,A4,A5)

二、LUT提升

总结一下,就好比单个LUT里面可以预存 2^6=64个结果。那么单个LUT可以实现

(1)输入信号最多为6bit,输出信号为1bit的的布尔逻辑函数;

(2)输入信号最多为5bit,输出信号为2bit的逻辑。

一个SLICE里面有四个LUT故最多可以预存的输出信号个数为 26*4=28。

因此在一个SLICE里面,借助选择器将多个LUT进行互连,可以实现输入数,输出数最多为如下所示的逻辑。

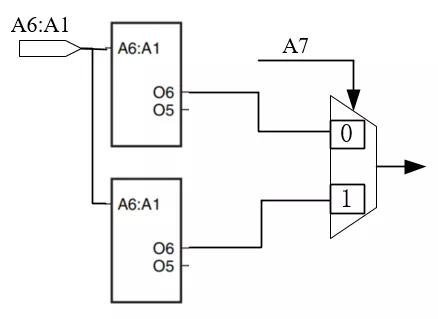

(1)2个LUT通过互连可以构成7bit输入,单bit输出的逻辑。实现方式为两个LUT的输入信号A1,A2,A3,A4,A5,A6接到一起,输出信号经过选择器选择输出,选择器的选择信号也是逻辑函数的一个输入信号。

将逻辑函数的输出送到Storage Element便可以形成同步时序逻辑。

(2)4个LUT通过互连可以构成8bit输入,单bit输出的逻辑。实现方式大家可以根据上面的实现方式自行推理。

(3)2个LUT通过互连可以构成6bit输入,2bit输出的逻辑。实现方式自行推理。

(4)4个LUT通过互连可以构成7bit输入,2bit输出的逻辑。实现方式自行推理。