热门标签

热门文章

- 1Android静态安全检测 -> 随机数使用不安全_securerandom随机数不安全使用

- 2无人自助棋牌室 麻将室 Java+小程序系统源码 SaaS多品牌 硬件Lora/ZigBee通讯_共享棋牌室 源码

- 3pycharm中Git常见操作与问题总结_committer identity unknown *** please tell me who

- 4【雕爷学编程】Arduino动手做(26)---4X4轻触开关矩阵键盘模块2_arduino 模拟触控按钮

- 5用清华源等国内镜像加速Python常用库的安装_清华镜像安装python库

- 6mysql表名忽略大小写_mysql 表名大小写忽略

- 7海南注册科技公司难不难?怎么注册?

- 8mysql 使用mysqldump 导出数据 和 怎么把导出的数据恢复_mysqldump导出sql文件恢复

- 9【攻克】抓包工具:中文版Fiddler使用 教程-攻克获取微信账单 保姆级进阶使用教程(超详细)_攻克抓包

- 10Android Button 属性介绍与使用_android button属性

当前位置: article > 正文

ZedBoard+AD9361_FPGA的PL端纯逻辑(verilog)配置控制9361(三)_建立完整工程,编写配置寄存器的状态机文件、SPI文件、9361收发接口文件并测试效果_ad9361工程

作者:Monodyee | 2024-04-21 11:45:59

赞

踩

ad9361工程

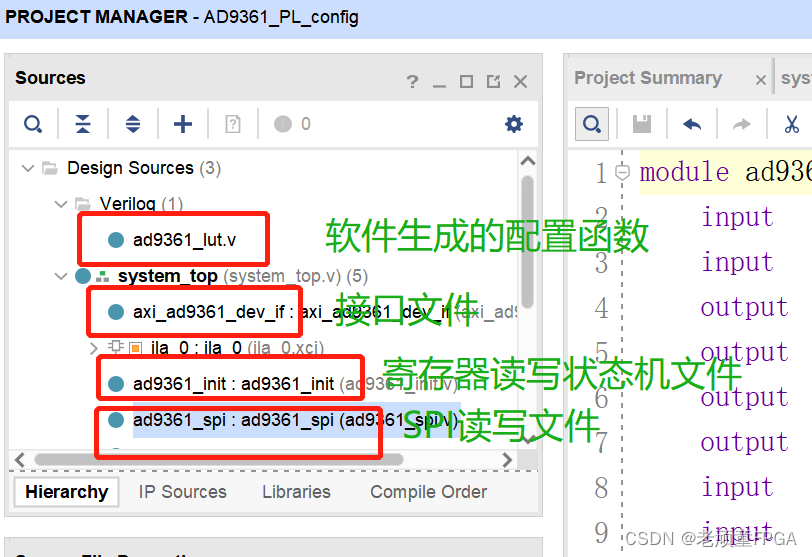

建立工程,主要文件有4个,配置函数,接口文件、寄存器读写状态机文件,SPI文件。

工程文件下载:百度网盘 提取码:mww7

一、编写状态机文件

根据前面生成的ad9361_lut.v文件,分成写状态、读状态、延时状态,反复循环,直到最后配置完所有寄存器之后使状态机处在一个固定状态,并给出配置结束的标志信号。时钟建议20MHz和SPI读写时钟一致。

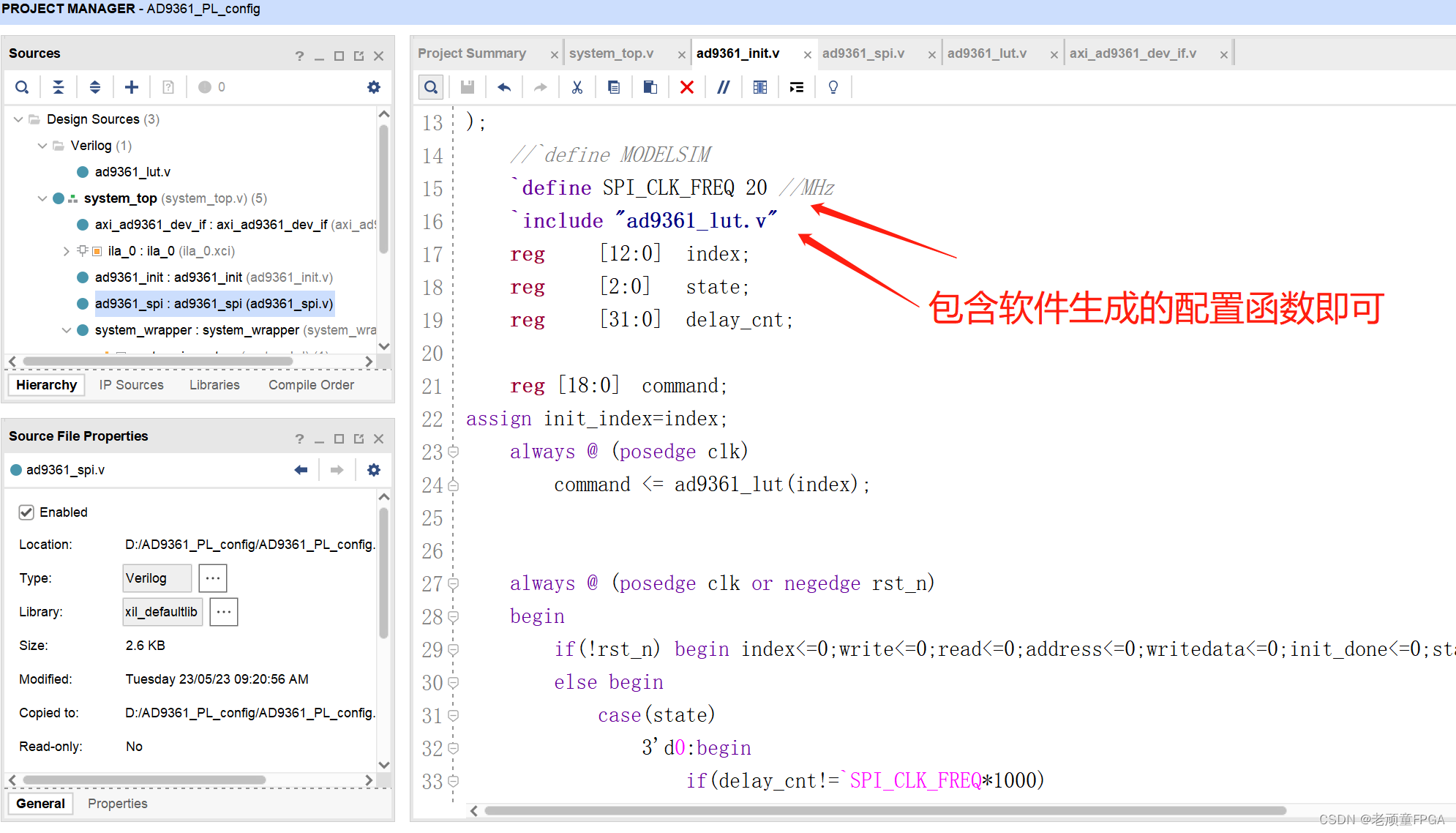

二、编写SPI读写文件

根据状态机状态,选择对相应寄存器的读写操作。根据状态机状态给出读写指示,并给出相应的寄存器地址和所需写入或读取的值。

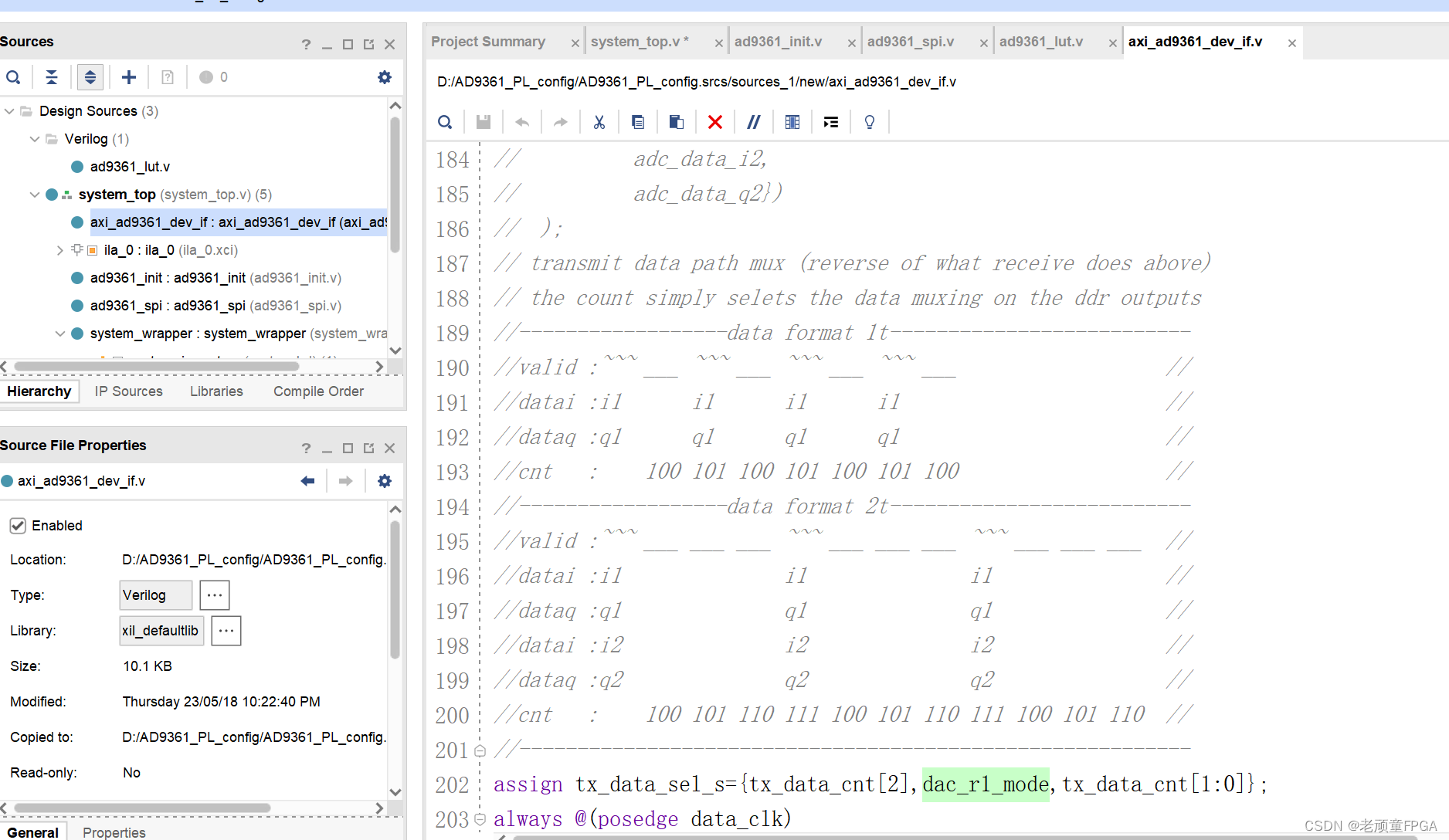

三、接口文件

基本参考ADI官方的接口文件,稍作修改,可以直接设置adc_r1_mode和dac_r1_mode配置单通道或者双通道读写。

四、测试结果

上述文件都编写结束,根据寄存器配置参数,AD9361应处在FDD工作状态,tx1和rx1单通道收发,收的频率2.4GHz,发的频率1.2GHz,工程编译完之后,加载到电路板,利用示波器测试clk_out引脚查看时钟是否配置正确,利用频谱仪测试输出信号是否为1.2GHz频率。

为了方便测试,使tx1通道输出单载波信号,直接向接口赋值1即可,如下:

示波器和频谱仪的测试结果,从测试结果看,时钟配置正确,输出信号频率1.2GHz。到这AD9361已经正常工作了。

并且通过ila查看了每个读寄存器的值,均符合要求。

推荐阅读

相关标签