- 1省钱!NewBing硬核新玩法;手把手教你训练AI模特;用AI替代同事的指南;B站最易上手AI绘画教程 | ShowMeAI日报_ai绘画教程bilibili

- 2一口气说出 Redis 16 个常见使用场景_redis使用场景

- 3动态规划-思考解决动态规划问题_你的公司老板给了你一张n×n个格子组成的动态规划

- 4B样条曲线优化各种路径规划算法,matlab栅格地图。_b样条优化

- 5three.js流动线_threejs流动线

- 6自然语言处理工具包:NLTKspaCy

- 7超星高级语言程序设计实验作业 (实验01顺序程序设计)_分别输入三个浮点数代表a、b、c的值;如果c的值为0,直接输出-1,否则计算并输出多项

- 8笔记本wifi与台式机、内网服务器共网、共享wifi详细教程_服务器没有网,怎么共享笔记本网络

- 9核函数kernal

- 10Android~获取WiFi MAC地址和IP方法汇总_android 获取本机wlan mac地址

NUMA概述

赞

踩

NUMA是什么

【非统一内存访问(NUMA)是一种用于多处理器的电脑记忆体设计,内存访问时间取决于处理器的内存位置。 在NUMA下,处理器访问它自己的本地存储器的速度比非本地存储器(存储器的地方到另一个处理器之间共享的处理器或存储器)快一些。】

下图就描述了一个比较形象的NUMA架构:

我们有两个NUMA结点。每个NUMA结点有一些CPU, 一个内部总线,和自己的内存,甚至可以有自己的IO。每个CPU有离自己最近的内存可以直接访问。所以,使用NUMA架构,系统的性能会更快。在NUMA结构下,我们可以比较方便的增加CPU的数目。而在非NUMA架构下,增加CPU会导致系统总线负载很重,性能提升不明显。

每个CPU也可以访问另外NUMA结点上的内存,但是这样的访问,速度会比较慢。我们要尽量避免。应用软件如果没有意识到这种结构,在NUMA机器上,有时候性能会更差,这是因为,他们经常会不自觉的去访问远端内存导致性能下降。

NUMA的几个概念(Socket,Core,Thread , Node)

总结:

- Socket就是主板上的CPU插槽;

- Core就是socket里独立的一组程序执行的硬件单元,比如寄存器,计算单元等;

- Thread:就是超线程hyperthread的概念,逻辑的执行单元,独立的执行上下文,但是共享core内的寄存器和计算单元。

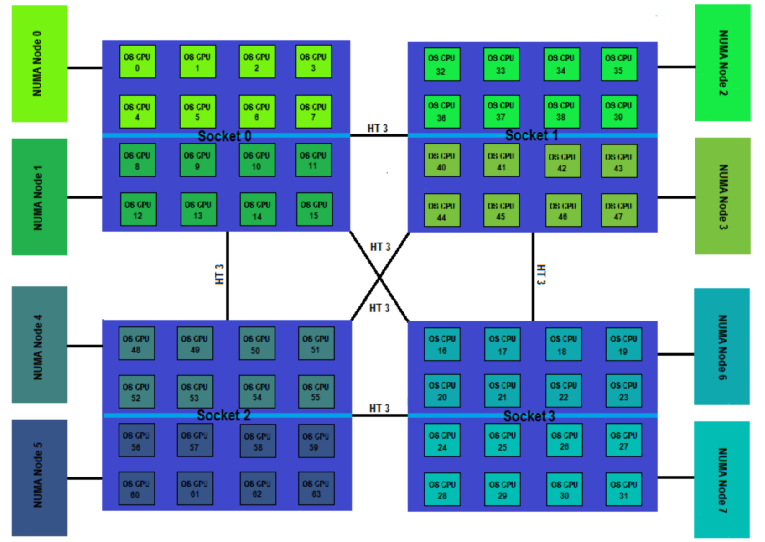

NUMA体系结构中多了Node的概念,这个概念其实是用来解决core的分组的问题,具体参见下图来理解(图中的OS CPU可以理解thread),图中共有4个socket,每个socket 2个node,每个node中有8个thread,总共4(Socket)× 2(Node)× 8 (4core × 2 Thread) = 64个thread。

根据上面提到的,由于每个node内部有自己的CPU总线和内存,所以如果一个虚拟机的vCPU跨不同的Node的话,就会导致一个node中的CPU去访问另外一个node中的内存的情况,这就导致内存访问延迟的增加。在有些特殊场景下,比如NFV环境中,对性能有比较高的要求,就非常需要同一个虚拟机的vCPU尽量被分配到同一个Node中的pCPU上。

如何查看机器的NUMA拓扑结构

比较常用的命令就是lscpu,具体输出如下:

dylan@hp3000:~$ lscpu Architecture: x86_64 CPU op-mode(s): 32-bit, 64-bit Byte Order: Little Endian CPU(s): 48 //共有48个逻辑CPU(threads) On-line CPU(s) list: 0-47 Thread(s) per core: 2 //每个core有2个threads Core(s) per socket: 6 //每个socket有6个cores Socket(s): 4 //共有4个sockets NUMA node(s): 4 //共有4个NUMA nodes Vendor ID: GenuineIntel CPU family: 6 Model: 45 Stepping: 7 CPU MHz: 1200.000 BogoMIPS: 4790.83 Virtualization: VT-x L1d cache: 32K //L1 data cache 32k L1i cache: 32K //L1 instruction cache 32k (牛x机器表现,冯诺依曼+哈弗体系结构) L2 cache: 256K L3 cache: 15360K NUMA node0 CPU(s): 0-9,20-29 NUMA node1 CPU(s): 10-19,30-39

- 1

- 2

- 3

- 4

- 5

- 6

- 7

- 8

- 9

- 10

- 11

- 12

- 13

- 14

- 15

- 16

- 17

- 18

- 19

- 20

- 21

- 22

- 23

cpu0的cache信息可用下列命令查看:

# cat /sys/devices/system/cpu/cpu0/cache/index0/shared_cpu_list 0,20 # cat /sys/devices/system/cpu/cpu0/cache/index0/size 32K # cat /sys/devices/system/cpu/cpu0/cache/index1/shared_cpu_list 0,20 # cat /sys/devices/system/cpu/cpu0/cache/index1/size 32K # cat /sys/devices/system/cpu/cpu0/cache/index2/shared_cpu_list 0,20 # cat /sys/devices/system/cpu/cpu0/cache/index2/size 256K # cat /sys/devices/system/cpu/cpu0/cache/index3/shared_cpu_list 0-9,20-29 # cat /sys/devices/system/cpu/cpu0/cache/index3/size 15360K

- 1

- 2

- 3

- 4

- 5

- 6

- 7

- 8

- 9

- 10

- 11

- 12

- 13

- 14

- 15

- 16

- 17

其中,index0对应的是L1 Data Cache,index1对应的是L1 Instruction Cache,index2对应的是L2 Cache,index3对应的是L3 Cache.

从上面我们看到cpu0 和cpu20 是node0上的 core0里面的两个兄弟逻辑cpu,按照intel的组织架构,这两个cpu是共享L1 cache (数据cache和指令cache) 和L2 cache的 ,同numa上的cpu共享L3 cache。遍历所有的cpu信息,可知cpu的拓扑架构如下所示:

另外:CPU Cache Line定义了缓存一次载入数据的大小:

# cat /sys/devices/system/cpu/cpu0/cache/index0/coherency_line_size

64

- 1

- 2

一般64位操作系统cache line为64。

上面的CPU拓扑架构图还不完整,每个node都有一个对应的本地内存。假设node0的本地内存标记为mem0,node1的本地内存标记为mem1。mem0对于node0就是本地内存,mem1对于node0就是远端内存;反之对于mem1亦有类似关系。

访问本地内存的速度要快于访问远端内存的速度。访问速度与node的距离有关系,node间的距离我们称为node distance

Node0的本地内存大小为32209MB,Node1的本地内存大小为32316MB。Node0到本地内存的distance为10,到node1的内存distance距离为20;Node1到本地内存的distance为10,到node0的内存distance距离为20。

参考:https://blog.csdn.net/weijitao/article/details/52884422