- 1算法-动态规划入门(C++实现)_c++动态规划

- 2Guitar Pro8软件激活码许可证如何获取?最新2024年免费教学步骤_guitarpro8许可证

- 3CNN中的卷积的作用及原理通俗理解_添加卷积cnn的作用是什么?

- 4HybridCLR热更新介绍

- 5用I/O流建立一个text.txt并写入字符。_用io流以文本方式建立一个文件txt,写入字符

- 6Redis集群原理和总结_redis的无主集群

- 7网络原理——TCP/IP--数据链路层,DNS

- 8Java安全--CC1的补充和CC6_yso cc6

- 9计划有变,国内应用厂商都在适配HarmonyOS?_haromony os next 适配情况_鸣潮适配鸿蒙吗

- 10基于OpenHarmony 系统通过S7协议读取西门子PLC数据_go plc s7

DE10-Standard板卡SoC入门实验之流水灯_d10-standard

赞

踩

说明

实验说明:

本实验的硬件平台基于DE10-Standard板卡,通过HPS控制FPGA的PIO外设,PIO连接有LED灯,实验现象为四个led依次循环点亮。

术语说明:

HPS:Hard Processor System硬核处理器系统

SOC:System On Chip 片上系统

Shell:本实验中指嵌入式命令行shell,即Embedded_Command_Shell.bat

软件说明:

本实验用到的软件有Quartus 15.1和SOC EDS 15.1。下文提到的bsp-editor工具和Shell包含在SOC EDS中。Qsys工具包含在Quartus中。进行本实验前请先正确安装这两个软件。

第一步:使用Quartus和Qsys工具完成硬件系统的配置。

该步骤实现SOC最小系统的硬件配置,包括硬核处理器配置、HPS和FPGA之间通信接口总线的选择、HPS外设裁剪、HPS时钟配置和SDRAM配置。该实验中主要用到HPS硬核,以及PIO外设IP核。Qsys工具为用户提供硬件系统的可视化设计,能够自动生成handoff文件,该文件配合bsp-editor工具可以生成preloader。Preloader是HPS的第二阶段引导源,主要作用为:初始化SDRAM接口,配置HPS IO口,加载下一引导源并跳转到它。

实验步骤

1 新建Quartus工程。

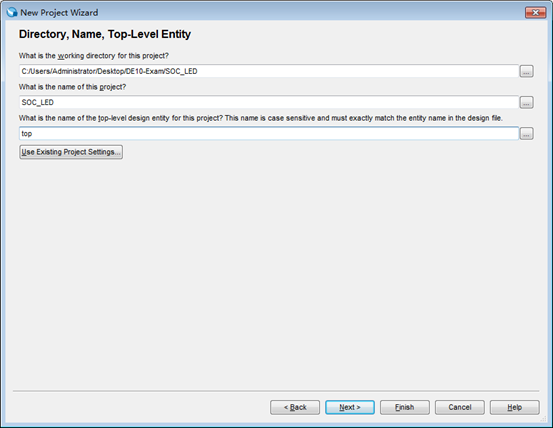

1.1 设置工程存放路径,工程名以及顶层文件名,如图1所示。

图 1

1.2 选择FPGA器件型号,如图2所示,DE10-Standard板载FPGA型号为5CSXFC6D6F31C6。

图 2

1.3 点击next直到finish,未提及的页面均按默认设置即可。

2 在Qsys中配置SOC。

2.1 运行Qsys工具。

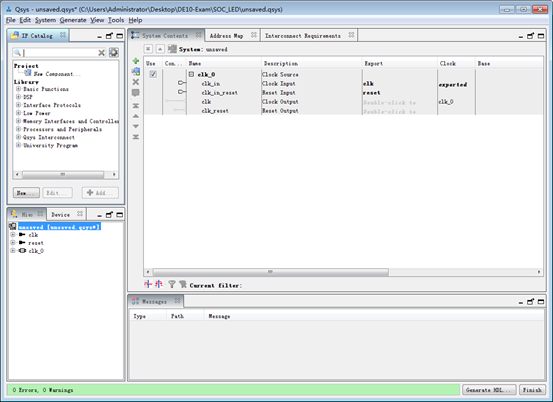

在Quartus软件中,通过菜单栏Tools->Qsys打开Qsys工具。刚打开的Qsys工具页面如图3所示。

图 3

2.2 添加HPS并完成配置。

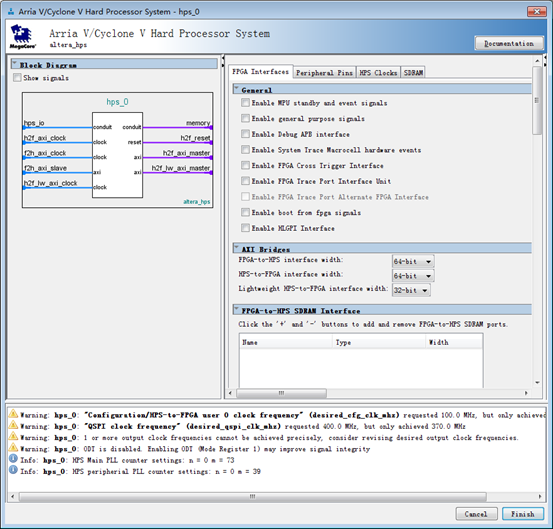

在左侧的IP目录中输入hps,选中Arria V/Cyclone V Hard Processor System,双击添加HPS,在弹出的HPS配置页面中进行HPS配置。HPS配置页面如图4所示。

图 4

1) 在FPGA Interfaces页面中,General一栏均不勾选,AXI Bridges一栏设为64-bit、64-bit、32-bit,FPGA-to-HPS SDRAM Interface一栏中移除原有接口,Resets一栏中均不勾选。

2)在Peripheral Pins页面中,设置HPS外设引脚复用及模式选择。设置如表1所示。设置完成后页面如图5所示。(本实验其实未用到这些外设)

表1 外设引脚复用及模式选择

外设名称 |

引脚复用选择 |

模式选择 |

EMAC1 |

HPS I/O Set 0 |

RGMII |

QSPI |

HPS I/0 Set 0 |

1SS |

SDIO |

HPS I/0 Set 0 |

4-bit Data |