- 1Llama3中文微调模型-Llama3-Chinese-8B-Instruct概述_llama3 chinese

- 2 webStorm Markdown 插件破解

- 3HOJ项目部署-前端定制案例分享:默认显示标签、 编辑器修改、导航栏、增加按钮音效、模拟机械键盘、AC彩带鼓掌喝彩特效、大屏、宠物升级、信奥编程python c++ 自动评测判题_前端网页编辑按下键盘不同类型按键音效的库

- 4数据结构中链式队列和顺序队列的实现_队列的顺序存储和链式存储的实现

- 5刷机维修进阶教程-----oppo机型 一加 7pro 修复基带 更改参数 实例详细步骤解析_一加修复基带

- 6使用VSCode运行React Native项目

- 7Kali Linux发动DDOS攻击_kali ddos

- 8算法——二分查找(一篇搞定)_二分查找csdn

- 9频谱、能谱、功率谱、倍频程谱、1/3 倍频程谱_1/3倍频程振动加速度级

- 102024年五一数学建模联赛B题具有无人机的物流配送问题

linux fall delay 10,Cell的Rise delay和Fall delay、Rise transition和fall transition

赞

踩

Cell的Rise delay和Fall delay、

Rise transition和Fall transition

介绍:

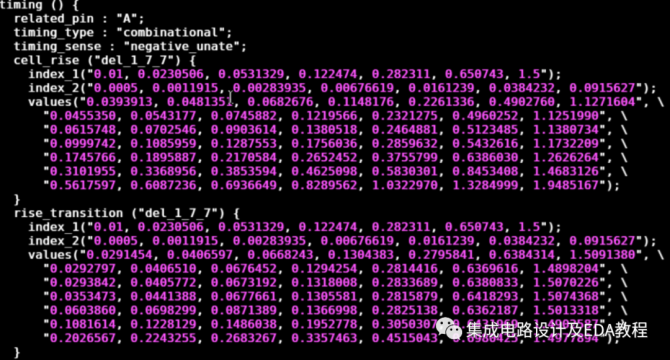

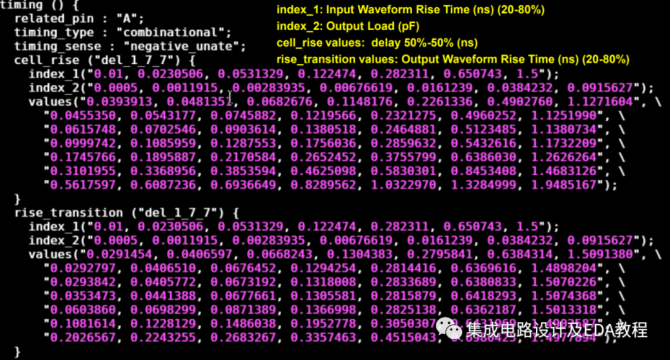

如下图所示为一个Cell的lib中关于cell_rise/cell_fall、rise_transition/fall_transition的描述:

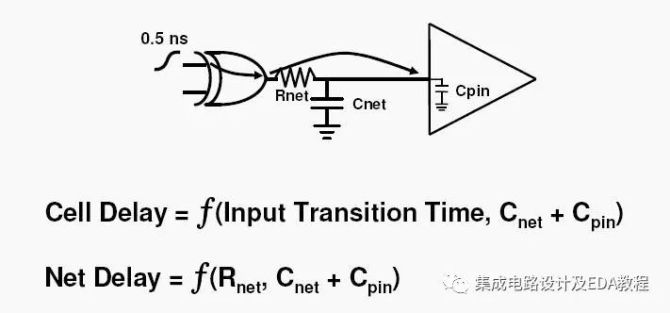

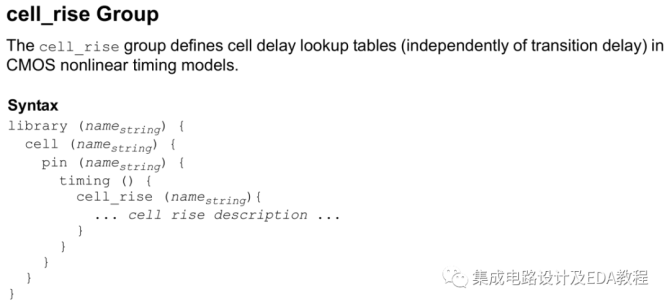

在NLDM模型的.lib中,cell_rise/cell_fall它描述的是Cell从输入到输出的延迟查找表,它是一个Input transition和Output load的二维查找表。

rise_transition/fall_transition描述的是Cell输出上升和下降沿transition time与Input transition和Output load的二维查找表。

问题:

以上内容大家应该都知道,下面提出一个问题:

对于.lib中的cell_rise/fall这里的rise和fall指的是输入是rise/fall还是输出是rise/fall情况下的cell delay呢?

输入是rise的猜想:因为delay是Input transition和Output load的二维查找表,所以可能指的是input rise或者fall的情况。另外该字段里面的related pin也是输入pin。

输出是rise的猜想:因为整个描述是定义在timing里面的output pin里面的,所以可能指的是output rise的情况,另外从名称判断cell_rise应该是输出上升的情况。

在给出答案之前大家可以想想哪个答案是对的。

混淆你的视听:

为了找到问题的答案,找了很多资料,可是发现网上有些资料是不可靠的,可能会混淆你的视听。

下面是Liberty UG里面相关的介绍,从里面并不能获得该问题的答案。

后来网上看到一个Liberty File的介绍,里面明确说明了rise_transition指的是output rise,而cell_rise感觉有点像是指的Input rise/fall:

http://web.engr.uky.edu/~elias/lectures/LibertyFileIntroduction.pdf

后来找了更多资料研究后发现这个图里面错误有很多,不具有参考性。

这个图里面的错误你能发现几个呢?

错误之处:

1、index_1和index_2不一定是input transition和output load,也可能是反着来的,要看lib前面的定义。不过在这里index_1是input transition没错,可是这个cell的timing_sense是negative_unate的,怎么可能出现input和output同时是rise的情况呢,所以上面的黄字介绍是错的,lib没错;

2、在index_1的input transition或者output transition rise time的时候里面说的是20%-80%,这个是有问题的,这个是lib里面定义的slew threshold的值,所以是slew time,而非transition time。这里应该写10%-90%。这里需要注意slew和transition的区别,之前一直以为是同一回事,研究发现并不是。后边会专门写篇推文介绍一下。

上面找到的例子有点问题,介绍几个正确的博文:

https://vlsiuniverse.blogspot.com/2016/12/liberty-format-introduction.html

https://gogul.dev/hardware/cmos-basics-for-sta-2

答案:

下面给出答案:

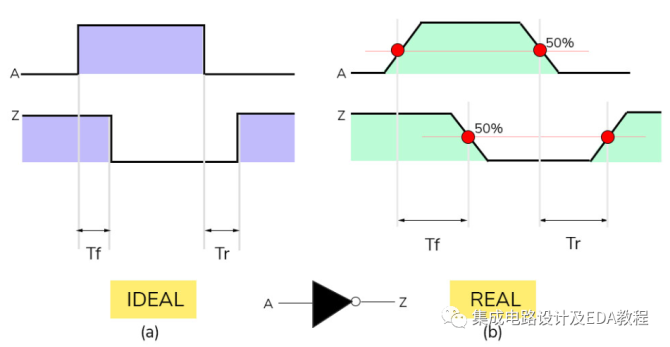

Cell_rise指的是当输出从0变为1时,在输入和输出之间的传播延迟;

Cell_fall指的是当输出从1变为0时,在输入和输出之间的传播延迟。

由于输入输出不是瞬间从0变成1的,反之亦然,因此我们需要定义一个阈值来进行测量:

# threshold point of input falling edge

input_threshold_pct_fall : 50.0 ;

# threshold point of input rising edge

input_threshold_pct_rise : 50.0 ;

#threshold point of output falling edge

output_threshold_pct_fall : 50.0 ;

#threshold point of output rising edge

output_threshold_pct_rise : 50.0 ;

这些点经常为VDD的50%,如下图所示为cell_rise/fall的真实定义:

举个例子:

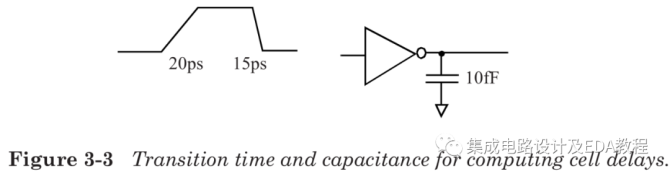

下面左图是一个Inverter的输入波形,input rise transition是20ps,input fall transition是15ps,output load是10fF。

那么Cell的fall delay通过查找LUT里面的cell_fall表格获取,其中查表用的输入分别为:

Input transition time(rising): 20ps;

Output load: 10fF