- 1盘点超好用的 6 款低代码开发平台_低代码工具

- 2【归并排序】C++数据结构实现归并排序完整代码_归并排序c++代码

- 3计算机网络:面向报文(UDP)和面向字节流(TCP)的区别_面向字节流和面向报文的区别

- 4jmeter分布式部署

- 5最通俗易懂的命名实体识别NER模型中的CRF层介绍

- 6python包括哪些部分_python必背内容有哪些

- 7智能聊天机器人实现 源码+解析_智能聊天机器人app的开发源码

- 8isaacgym(legged_gym)学习 (一)—— 添加自己的机器人模型并训练_isaacgym在训练自己的模型过程中机器人倒了

- 9记一次 mac电脑 parallels desktop win10 虚拟机配置rsync文件同步功能(含mac 无法读写ntfs移动硬盘的解决方法)_ntfs移动硬盘虚拟机安装w10

- 10百度身份证文字识别_百度身份证识别 只识别出一个address

fpga最小系统设计如何加入中断_Xilinx FPGA 自主配置管理容错设计研究(二)

赞

踩

针对SRAM型FPGA在空间辐射环境下容易受到单粒子效应影响的问题,在分析可重配置的Xilinx FPGA的结构和故障模式的基础上,提出一种基于自主配置管理的Xilinx FPGA容错设计方案。综合运用诸如逻辑电路三模冗余、块存储器EDAC校验、动态回读、动态局部重配置及周期全局重配置等方法实现故障的屏蔽、检测和修复。该方案覆盖了FPGA的各种单粒子效应故障模式,并且在芯片内部实现了自主配置管理,具有体积小、成本低、可靠性高的特点。

【关键词】现场可编程门阵列;容错;单粒子效应;自主配置管理

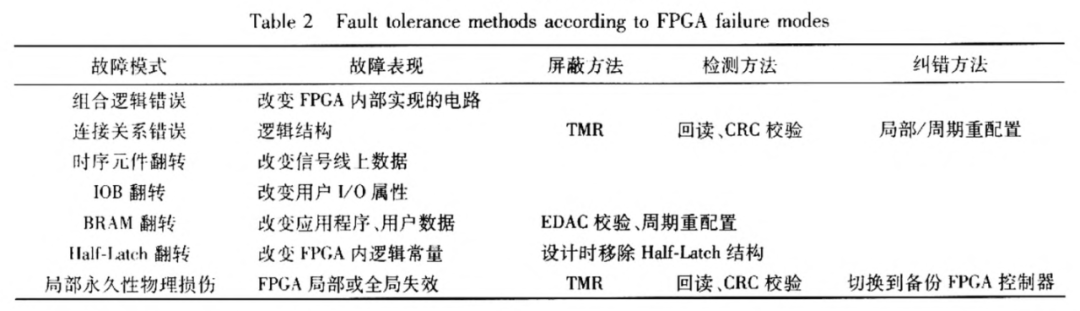

四、于自主配置管理的容错方案FPGA容错设计的目标是保证系统的安全性和可靠性,使得在各种单粒子效应发生时,尽量能够顺利执行正常操作,而不会导致操作紊乱或停止。针对上述FPGA故障模式,综合各种故障屏蔽、检测和纠错技术,建立如表2所示的故障应对方案。

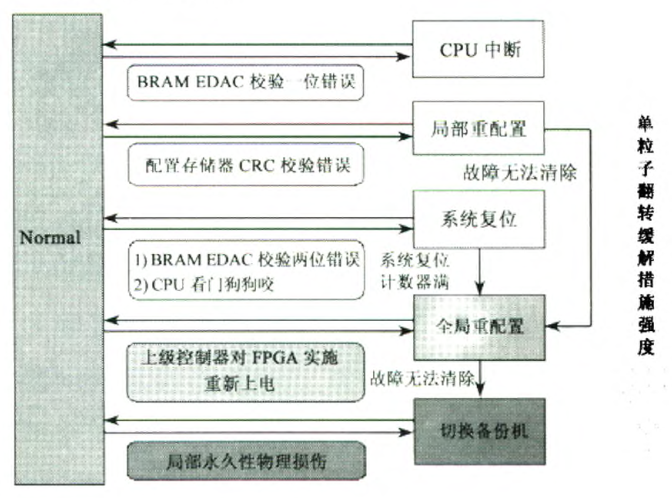

除了Half-Latch翻转和BRAM翻转,FPGA的各种故障都可以通过配置存储器的回读来检验,而除了永久性物理损伤,其它故障都可以通过重新配置存储器来纠正。因为局部重构方法会带来大量的时间和空间开销,目前尚处于理论研究阶段,因此在单机容错设计时不予采纳。可以采用双机冷备份的工作方式,若发生局部永久性物理损伤可以切换到备份FPGA。另外对于BRAM的容错处理也比较特殊,因为用户数据均存储在BRAM中,用户数据是根据程序运行情况不断变化的,所以不能通过回读来校验BRAM的翻转,也不能使用重配置来纠错,所以采用EDAC方法实现故障屏蔽、检测和纠错。应用表2中的容错方法,可以建立如图3所示的SEU缓解状态机。

挂接在OPB总线上的BRAM模块采用“纠1检2”的硬件检错与纠错电路,当存储器中一个32位数据发生单比特翻转时能及时纠正,发生两比特翻转时能及时检测出来。因为对一位错误能及时纠正,所以只需通过中断信号通知CPU即可。而两位错误只能检测不能纠正,所以两位错误发生时就需要对系统软件实施复位,若复位无法清除故障就实施全局重配置。回读配置存储器中除BRAM以外的配置信息,按帧进行CRC校验,发现错误时,对故障帧实行局部重配置,若故障不能清除就实施全局重配置。全局重配置后还不能清除故障,则意味着可能发生了局部永久性物理损伤,此时切换到备份FPGA控制器。

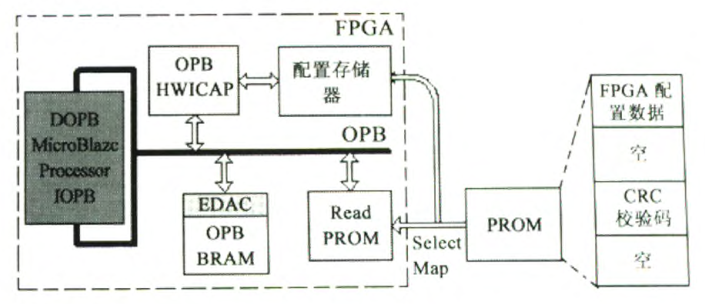

通常,FPGA配置存储器的回读与重配置由外部对单粒子效应不敏感的器件来控制。因为需要增加额外的配置管理控制器,这种方案体积、功耗大。Xilinx FPGA提供了lCAP(Internal Configuration Access Port)模块,可以通过ICAP从芯片内部访问配置存储器,从而实现回读与重配置的自主管理。图4给出了FPGA自主配置管理的结构框图。一次性烧写的PROM芯片对空间辐射效应不敏感,对单粒子事件免疫,因此将FPGA的配置数据和每一帧的校验码存入PROM中。

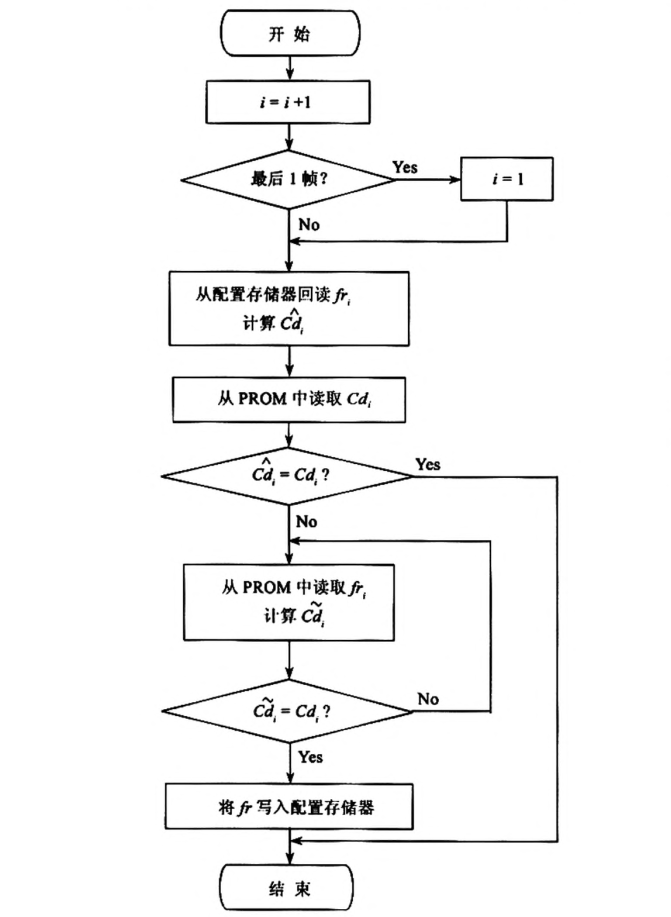

在设计阶段,对配置数据按帧进行编码,得到每一个配置帧 fri 的编码校验数 Cdi ,并预先存储在PROM中。上电后,配置数据通过SelectMap接口自动写人FPGA配置存储器。正常运行后,FPGA的回读与重配置管理由运行在Microblaze处理器中的一段配置管理程序来实现。配置管理程序控制OPB HWICAP模块读取配置帧 fri 的内容并存放到BRAM中,重新计算 fri 对应的编码校验值 Cdi ,同时通过ReadPROM模块从PROM中读入 fri 的原始校验码 Cdi ,比较两者,相同则处理下一帧 fri +1;若不同,则有可能发生了SEU,需要对故障帧进行局部重配置。此时通过ReadPROM模块从PROM中读入配置帧数据 fri ,经过校验码匹配验证后,通过OPB HWICAP模块写入FPGA配置存储器,覆盖原来的故障帧,在不干扰FPGA正常工作情况下,实现了故障的修复。配置管理程序的流程如图5所示。

4.1 ICAP接订

除了SelectMap等外部配置接口,Xilinx Virtex系列FPGA特别设计了一个内部配置接口ICAP,通过ICAP可以对配置控制逻辑进行读/写操作,并可以在运行过程中改变FPGA的当前配置。ICAP接口位于FPGA芯片物理位置的右下角,其通信协议是SeIectMap协议的子集,包括独立的8位数据读端口I[0:7],写端口O[0:7],写控制信号WRITE,芯片选择信号CE,忙信号BUSY及时钟输入CLK。为了保证不被误操作影响,不允许通过ICAP对整片FPGA实施全局重配置。在本应用中,ICAP嵌入到OPB HWICAP模块,作为从器件连接到OPB总线,受Microblaze软核处理器的控制,可以方便的实现FPGA芯片的自主配置管理。当总线频率为50MHZ时,lCAP接口可以达到5MB/s的数据吞吐能力。

4.2 帧定位

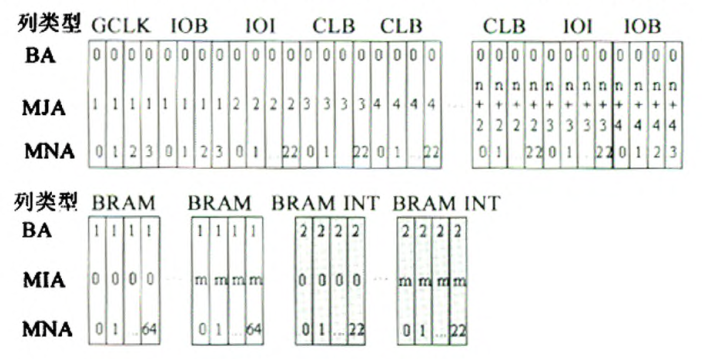

Xilinx FPGA的最小可配置单元称为帧,按照32位地址寻址,包含块地址BA(Block Address),主地址MJA(Major Address),次地址MNA(MinorAddress)和字节数。Virtex-II配置存储器可以划分为3个相对独立的块:BAO包含所有GCLK、IOB、IOI和CLB列;BAl包含所有BRAM列;BA2包含所有BRAM Interconnect列。主地址标识出块中的指定列,次地址标识出列中的指定帧。PROM中存储的配置数据文件,帧与帧之间数据是连续的,并没有明确的帧地址标签,因此要实现单帧数据的重配置,必须获得配置帧在位流文件中的位置信息。图6给出了位流文件中帧的排列顺序,按照帧地址增加的方向,数据帧依次代表了各配置列的信息。图中,n 为FPGA中CLB列的总数,m 为BRAM列的总数。

4.3 动态回读和校验

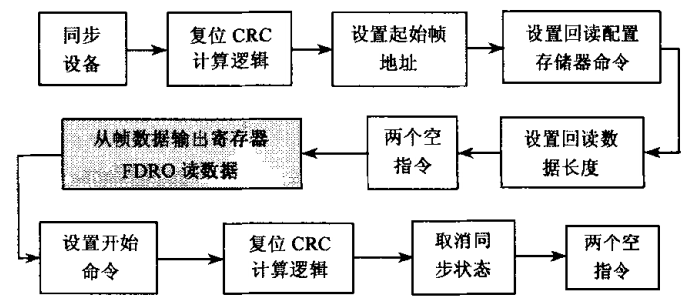

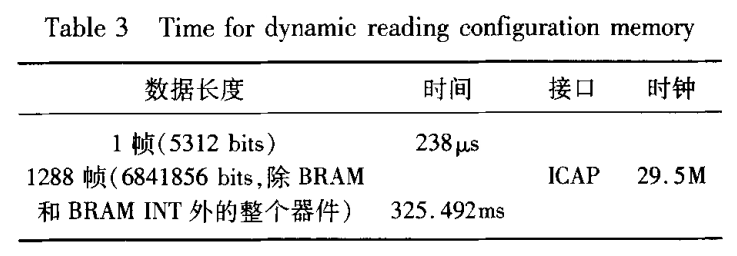

回读是通过ICAP接口将FPGA内部配置存储器中的数据读出的过程,动态回读是指回读过程不干扰FPGA的正常运行。通过回读可以获得CLB、IOB的寄存器以及布线资源的当前配置情况,然后通过对回读数据的校验来检验当前配置数据正确与否。回读与校验是检测单粒子翻转故障的重要方法。向配置寄存器发送如图7所示的回读命令,可以从帧数据输出寄存器FDRO中读取配置存储器内相应位置的配置信息,每一帧回读数据的内容都决定着这些位置的可编程逻辑资源所实现的功能。表3为Microblaze处理器中配置管理程序通过ICAP接口对XC2V3000进行动态回读的时间特性。

回读数据的校验一般有直接比较和编码校验两种方法。直接比较是将回读数据和标准数据逐位比对。一种实现方法是将标准数据文件(*.rbb)和屏蔽数据文件(*.msk)保存到专门的存储区域,并将上述文件中的数据RBB[i],MSK[i]和回读数据DATA[i]按照式RBB[i]=MSK[i]×DATA[i]进行校验。这种方法需要大量的存储空间,不适合应用于FPGA自主配置管理。另外还可以将PROM设置成配置后可读的模式,从PROM中读取标准配置数据同回读数据进行比对,虽然可以避免使用大的存储空间,但是逐位的比对依然会带来大量的时间开销,所以本文采用编码校验的方式,采用CRC算法来验证回读帧数据的正确性,16位CRC校验码的生成多项式为:

CRC16=x16+x15+x2+1在设计阶段应用16位CRC为每一配置帧 fri 。预先生成一个标准校验码 Cdi ,为提高可靠性,将校验码存储在对辐射效应免疫的PROM中。同时在FPGA内部集成16位CRC电路,实时计算回读数据帧校验码Cdi ,并在配置管理程序中将两者进行比较,以决定是否重新配置数据帧 fri 。

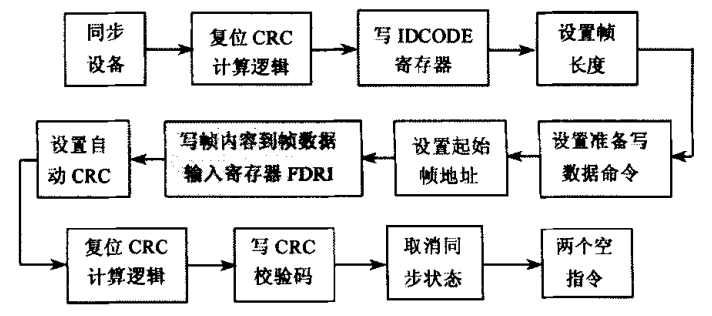

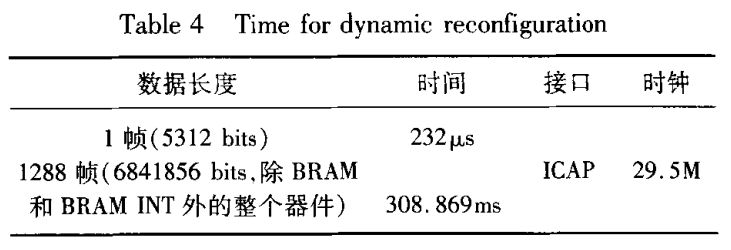

4.4 动态局部重配置

动态局部重配置是在不中断FPGA正常工作的情况下,通过ICAP接口重新写入部分配置信息的过程。局部重配置的目标有两点:(1)纠正SEU故障造成的电路逻辑错误;(2)在整个重配置过程中维持FPGA正常运行。局部重配置的最小单元为帧,通过图8所示的命令流程将一帧数据写人帧数据输人寄存器FDRI,从而实现配置信息的重新写入。表4为Microblaze中配置管理程序通过ICAP接口对XC2V3000进行动态重配置的时间特性。

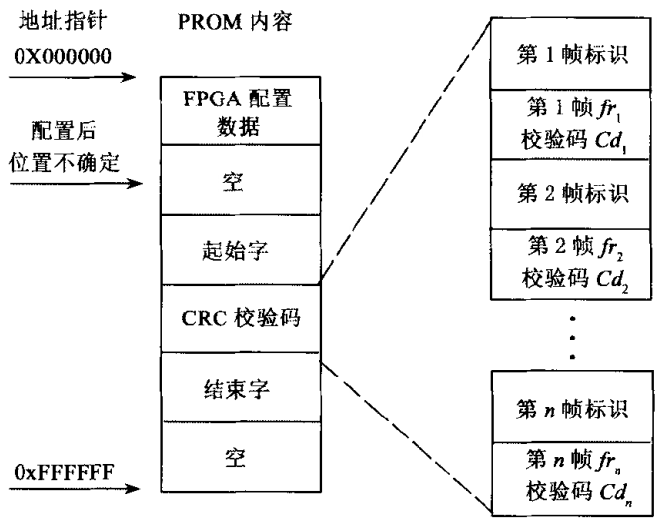

4.5 从PROM中读取数据

PROM是非可寻址的存储元件,复位后地址指针指向0位,按照时钟节拍地址指针不断累加,并将相应地址内容输出到总线。FPGA上电配置完成后,时钟信号停止输出。在配置位流文件产生时,配置选项设置不同会导致配置完成的最后阶段(设备启动阶段)占用的时钟周期不确定,因此无法确定PROM地址指针的当前位置,这样就不能可靠定位配置数据之后的CRC校验码数据。为了解决这个问题,设计中效仿配置数据的组织形式,在校验码数据之前加“起始字”,在数据最后加“结束字”,如图9所示。读取校验码时,将从PROM中读到的无关数据丢弃掉直到接收到起始字为止。为了更加方便、可靠的获取每一帧的校验码,在校验码之前又增加了一个帧标识。

图9 PROM中数据存放示意图

图9 PROM中数据存放示意图

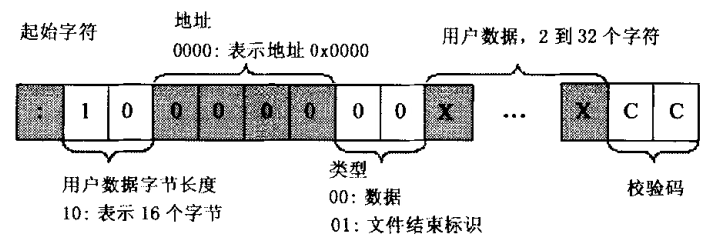

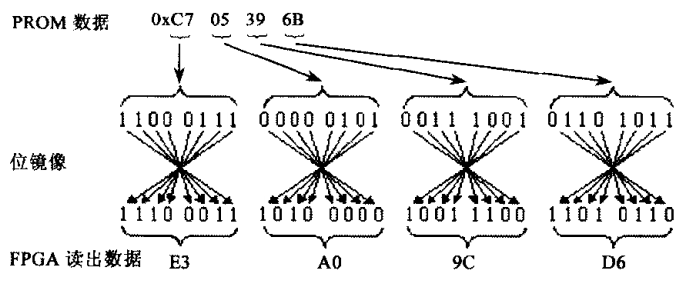

PROM的文件格式为Intel标准的MCS文件,Xilinx提供PROMGen工具将包含配置数据的位流文件转换为MCS文件。要将CRC校验码数据加入到此文件中,必须按照MCS文件标准对校验码数据进行包装处理,添加CRC校验码数据到图10中的用户数据位置。FPGA从PROM中读出的每个字节都是镜像排列的,如图11所示。应用PROMGen工具时,已经自动将配置数据进行了镜像处理。对于CRC校验码,为了保证能够读出顺序正确的数据,应当预先进行镜像处理或者在FPGA读入数据后再进行镜像处理。

4.6 硬件设计要求

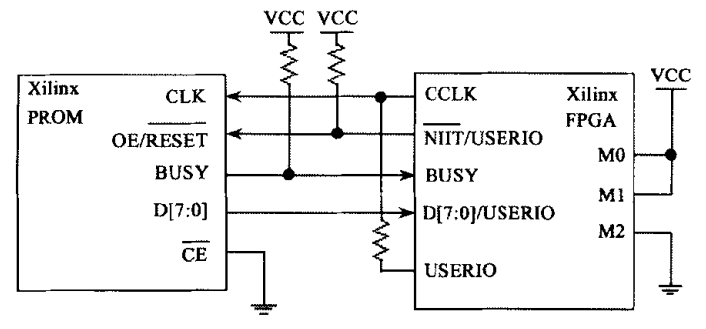

要在FPGA配置完成后读取PROM中存储的配置帧和校验码数据,必须考虑FPGA与PROM之间的接口设计。图12给出了FPGA与PROM之间的接口信号简图。与标准的SelectMap接口相比,有以下几点不同:(1)CE通常连接到FPGA的DONE引脚,配置完成后DONE输出高电平,可以令PROM进入待机状态,以降低电源消耗。因为要不间断的从PROM中读取数据,所以设计中直接连接到地,令PROM一直处于工作状态;(2)增加了用户I/O驱动PROM的CLK引脚。在FPGA上电配置完成之后,CCLK引脚即停止输出时钟信号,以防止PROM地址计数器溢出,此时需要用户I/O输出时钟信号驱动CLK引脚;(3)连接OE/RESET到FPGA的INIT引脚,允许在配置过程中在发现CRC校验错误时由FPGA重新启动配置。配置结束后,INIT引脚分配为用户I/O,控制此引脚可以复位PROM地址计数器;(4)D[7:0]从PROM中读入配置数据,配置结束后,D[7:0]分配为用户I/O,通过此8位总线读入配置帧和校验码数据。

4.7 资源利用要求

帧是FPGA中的最小重配置单元,当某一帧的回读校验结果错误时,虽然错误可能只是发生在某一个CLB单元,但是必须对其所在帧全部重新配置。Xilinx FPGA采用了无干扰过渡技术,所以在大多数情况下,对于配置单元的写操作不会影响当前的操作,即在写操作过程中依然能够维持正确的电路逻辑,这是能够实现动态在线重配置的关键。但是当LUT被配置成移位寄存器或RAM模式时,回读和写操作会对移位寄存器和RAM产生干扰,使得其丢失当前状态,从而导致整个电路实现的错误。因此设计时要移除LUT移位寄存器和LUT RAM。

五、结论本文以提高Xilinx FPGA的空间适应能力和抗辐射能力为目标,重点研究了FPGA的故障模式和单粒子效应缓解方法。提出了基于自主配置管理的FPGA容错方案。综合运用逻辑电路三模冗余,BRAM存储器EDAC校验及动态局部重配置等方法实现故障的屏蔽、检测和修复。通过ICAP接口对FPGA配置存储器进行读/写操作,从而在嵌入式处理器中方便的实现FPGA配置的自管理,与将配置管理放在外部控制器中相比,极大的减少了成本,缩小了体积,降低了系统的复杂程度。

参考文献[1] 邢克飞,杨俊,王跃科,等.Xilinx SRAM型FPGA抗辐射设计技术研究[J].宇航学报,2007,28(1):123-129.[Xing Ke-fei,Yang Jun,Wang Yue-ke,et al.Study on the anti-radiation technique for Xilinx SRAM-based FPGA[J]. Journal ofAstronautics,2007,28(1):123-129.]

[2] 郝志刚,杨孟飞.星用SRAM型FPGA的故障模式分析和容错方法研究[J].空间控制技术与应用,2009,35(1):5l一55.[Hao zhi-gang,Yang Meng-fei.Fault mode analysis and fault tolerant methodology for SRAM-based FPGA on spacecraft[J].Aero-space Control and Application,2009,35(1):51—55.]

[3] Cheathanl J A,Emmert J M,Baumgart S.A survey of fault tolerant methodologies for FPGAs[J].ACM Transactions on Design Automation of Electronic Systems,2006,11(2):501-533.

[4] Doumar A,Ito H.Detecting,diagnosing,and tolerating faults in SRAM based field pmgrammable gate arrays:a survey[J].IEEE Transactions on Very Large Scale Integration(VLSI)Systems,2003,11(3):386-405.

[5] Huang W J,McCluskey E J.Column-based precompiled configuretion techniques for FPGA[C].The 9th Annual IEEE symposium on Field-Programmable Custom Computing Machines,Rohnert Park,USA,March 29-April 2,2001.

[6] Dutt S,Shanmnugavel V,Trimberger S.Efficient incremental rerouting for fault reconfiguration in field programmable gate arrays [C].The 1999 IEEE/ACM international conference on Computer-aided design.San Jose,USA,November 7-11,1999.

[7] Keymeulen D,Zebulum R S,Jin Y,et al. Fault-tolerant evolvable haIdware using fieId-programmable transisor arrays[J]. IEEE Transactions on Reliability,2000,49(3):305-315.

[8] Oreifej R S,AI-Haddad R N,Tan H,et al.Layered approach to intrinsic evolvable hardware using direct bitstream manipulation of Virtex-II Pro device[C].The 17th International Conference on FieId ProgrammabIe Logic and AppIications. Amsterdam,Netherlands,August 27-29,2007.

[9] Ross R,Hall R.A FPGA simulation using asexual genetic algorithms for integrated self-repair[C]. The FirsI NASA/ESA Conference on Adaptive Hardware and Systems.Istanbul,Turkey,June 15-18,2006.

[10] Xilinx Virtex-II Platform FPGA User Guide[M/0L].USA:Xilinx company,2003[2011—2一11].http://www.xilinx.com/support/documentation/index.htm

[11] Swift G M,Rezgui S,George J,et al.Dynamic testing of Xilinx Virtex-II field programmable gate array(FPGA)input/oulput blocks(IOBs)[J].IEEE Transactions on Nuclear Science,2004,5l(6):3469-3474.

[12] Graham P,Caffrey M,Johnson D E,et al.SEU mitigation for half-tches in Xilinx Virtex FPGA [J]. IEEE Transactions on Nuclear Science,2003,50(6):2139-2146.

[13] Tan H. A multi-layer FPGA framework supporting autonomous runtime partial reconfiguration [D]. FL,USA: University of Central Florida Orlando,2007:70-72.

——————————分割线—————————— 历史文章导航 FPGA在SHA256高效数字加密研究 基于 FPGA 的 SHA256 高效数字加密系统中文摘要高效的哈希算法的研究是当前安全领域研究的热点。 通过从SHA256核到整个加密系统,都做了详细的测试和性能对比。通过一系列的参数对比,我们可以看出,FPGA相比目前高性能的CPU能够较快的完成数据的加密工作。 点击下方链接,点击进入原创文章 基于 FPGA 的 SHA256 高效数字加密研究(一)基于 FPGA 的 SHA256 高效数字加密研究(二)基于 FPGA 的 SHA256 高效数字加密研究(三)基于 FPGA 的 SHA256 高效数字加密研究(四)【总结】基于 FPGA 的 SHA256 高效数字加密研究(五)DRM系统的SHA256算法设计及FPGA实现(一)DRM系统的SHA256算法设计及FPGA实现(二) 基于FPGA的SHA256算法实现(一) FPGA基础入门到高手的相关知识 FPGA是英文Field Programmable Gate Array的缩写,即现场可编程门阵列,它是在可编程阵列逻辑PAL(ProgrammableArrayLogic)、门阵列逻辑GAL(GateArrayLogic)、可编程逻辑器件PLD(ProgrammableLogicDevice)等可编程器件的基础什么是FPGA上进一步发展的产物。 点击下方链接,点击进入原创文章 FPGA基础入门(一)FPGA基础入门(二) FPGA基础入门(三)从基础入门到高手的相关知识 Filecoin代码解析 从2014年发展至今天, IPFS 已经是一个很成功的的项目,其libp2p 模块在开源社区得到广泛应用,而2017年诞生的 Filecoin 项目重用了 IPFS 的绝大多数代码,其高技术起点吸引了全球的技术爱好者。 点击下方链接,进入原创文章 Filecoin代码解析—Lotus入门篇(1) Filecoin代码解析—Lotus入门篇(2):Seal简析之CAR格式篇