热门标签

热门文章

- 1Stable Diffusion ComfyUI 基础教程(六)图片放大与细节修复_comfyui怎么用放大算法

- 2中国蚁剑免费下载(这里是win版)_中国蚁剑下载

- 3中兴新支点命令篇——任务管理命令_新支点系统查看版本命令在哪

- 4【Unity】通过代码控制编译器的暂停_unity 暂停编辑器

- 5自然语言处理--Keras 实现LSTM循环神经网络分类 IMDB 电影评论数据集_lstm电影评价数据集

- 6计组实验报告(1)_支持veriloghdl的工具及获取方法

- 7维修服务系统,解决家居小问题

- 8Python中os.environ基本介绍及使用方法_os.environ.get

- 9阿里云ECS流量计算_如何查看阿里云流量使用情况csdn

- 10函数调用时长的关键点:揭秘参数位置的秘密

当前位置: article > 正文

实验四 用集成移位寄存器实现序列检测器_1101序列检测器

作者:weixin_40725706 | 2024-05-26 14:37:04

赞

踩

1101序列检测器

一、实验要求

用移位寄存器和与非门设计一个

1101

序列检测器。电路连续不停地工作,对 串行输入的序列进行检测,当连续检测 4

个码元符合检测码

1101

时,检测器输出 为 1

,指示灯亮,其他情况下输出为

0

,指示灯灭。

二、实验设备

1

.

Mini-FPGA

开发板(

Cyclone IV

系列

EP4CE6F17C8

);

2

.主要集成电路:

74LS194

双向移位寄存器、

2

输入与非门、

4

输入与非门

3

.软件:Quartus II 13.1

三、设计过程

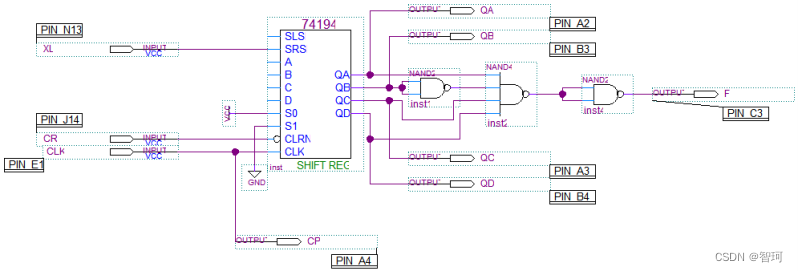

工作原理:

本实验用到了

7474LS194

双向移位寄存器,因只进行序列检测,故只用到了同步移 位功能。该实验中用到的移位功能为右移,因此将 S0,S1

分别接入

1

,

0

,同时序列输入 端接在右移串口输入端,再接好时钟信号和清零端。

在输出端,由于要检测的序列为 1101

, 且当连续检测 4

个码元符合检测码

1101

时,检测器输出为

1

,因而将输出端 接成

接成

仿真电路图:

四、实验结果及分析

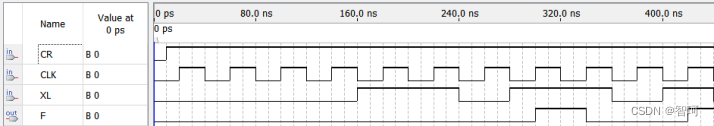

波形仿真及下载测试结果分析:

通过设计序列 XL 输入波形(0000110110100101111000),测试

Q

A

Q

B

Q

C

Q

D

对应所有可 能输出(0000,0001,...,1111)时和序列 1101 重复输出时对应的输出效果效果,结果输 出正常,符合实验要求。

波形仿真图(前半)

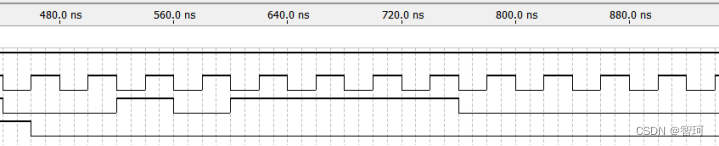

波形仿真图(后半)

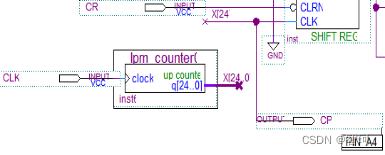

下载测试时,将

XL

定位到

sw7

,

CLK

和

CR 分别定位到时钟信号(E1)

和

key0

,注:这里的

CLK 时钟信号要经分配后(

本次实验为

25

分频

)

再接入 信号端,同时另接一个输出口定位到 LED2

,用 来观察其状态。

输出端

Q

A

Q

B

Q

C

Q

D

分别定位到 LED6,

LED5

,

LED4

,

LED3

,用来观察当前输 出序列。输出 F

定位到

LED7

。经测试,输出符合要求。

五、实验心得

经过此次实验,一方面我对 quartus 软件的使用更加熟练,另一方面对

7474LS194 双向移位寄存器的功能更加清晰,同时对序列检测器的设计和波形仿真有了更全面的认 识,理解了对序列重输出检测的波形设计。

声明:本文内容由网友自发贡献,不代表【wpsshop博客】立场,版权归原作者所有,本站不承担相应法律责任。如您发现有侵权的内容,请联系我们。转载请注明出处:https://www.wpsshop.cn/w/weixin_40725706/article/detail/627101

推荐阅读

相关标签