- 12019 Power BI最Top50面试题,助你面试脱颖而出系列<中>

- 2MySQL详细介绍:开源关系数据库管理系统的魅力

- 3算法数据结构——线性动态规划算法(Linear-DP)超详细总结加应用案例讲解_动态的线性规划问题

- 4私家云二代\比特米盒CumeBox2 配置CasaOs作为家庭轻nas\轻影院\网盘挂载\下载器使用(对应Armbian_21.08.1_Ubuntu_CumeBox2_5.10.602.img固件)_比特米盒刷casaos

- 5mysql 的left join、right join和join的区别_mysql left join 和 right join 和 join 的区别

- 6C/C++ 中三块难啃的硬骨头

- 7数据结构(五)——树与二叉树的应用_数据结构-树和二叉树及其应用

- 8Oracle集合类型

- 9MySQL数据库——多表查询(3)-自连接、联合查询、子查询_mysql自连接

- 10C++之继承(万字长文详解)_c++ struct 继承

基于Zynq的以太网传输工程教学:实现高效数据采集与传输,缩短开发周期_zynq在已有工程上增加以太网功能

赞

踩

基于zynq的以太网传输工程教学。

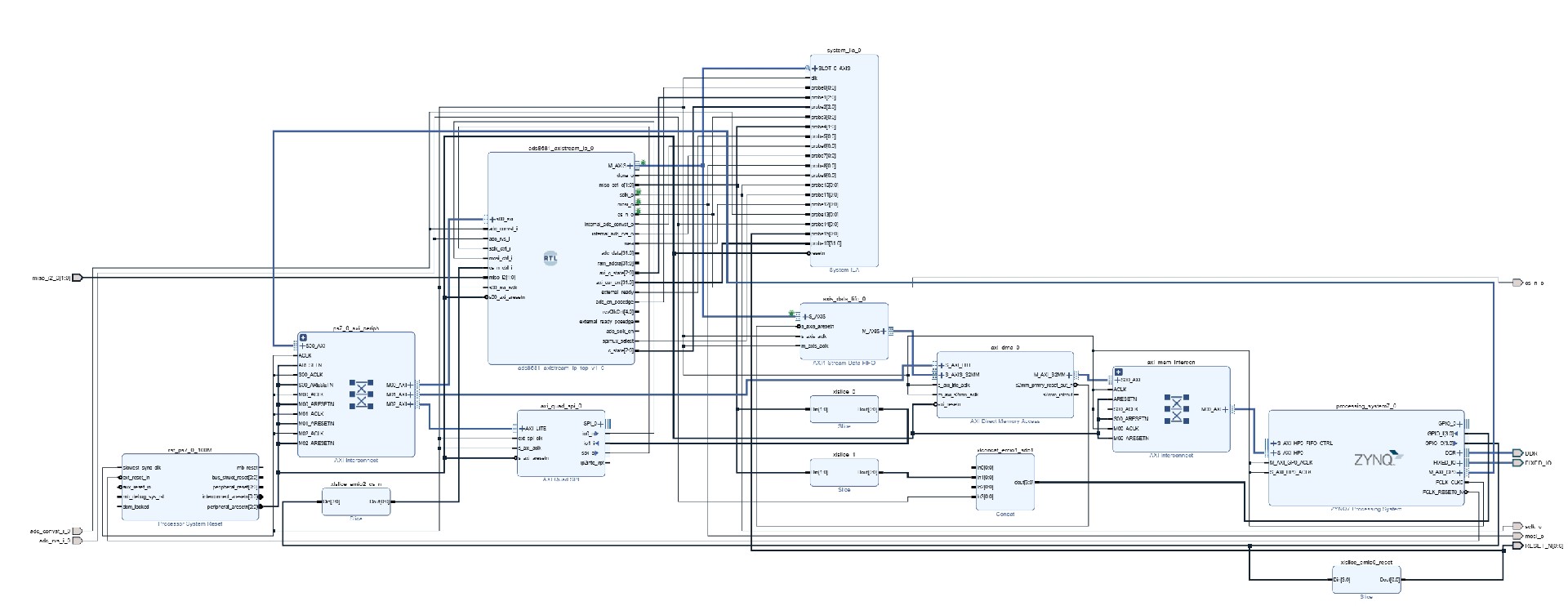

内容:这是一个框架 将fpga获得的数据通过dma存入ddr 再从处理器端将数据从ddr读取并通过千兆网传输给电脑

意义:作为一个开发框架 继续这个框架可以半天就能实现数据采集功能 对于基于adc或者dac项目的验证开发非常高效 缩短开发周期 今后类似项目全部可以复用 重新开发工作量小于20%

适合人群:模拟半导体芯片的测试或应用工程师、FPGA/ZYNQ需要的嵌入式工程师或者在校学生老师

FPGA工程 + vitis rtos 工程 + 工程说明文档

ID:86899730924441966

CommEngineer

基于Zynq的以太网传输工程教学

引言:

随着科技的不断发展,FPGA(现场可编程门阵列)技术在电子领域中扮演着越来越重要的角色。而基于Zynq的以太网传输工程则为开发者提供了一个高效且便捷的开发框架。本文将详细介绍这个框架的结构与功能,并探讨其在数据采集和验证开发等领域的重要意义。本文适合具备一定FPGA和嵌入式开发基础的人群,如模拟半导体芯片的测试或应用工程师、FPGA Zynq需要的嵌入式工程师以及在校学生和教师。

一、框架概述

基于Zynq的以太网传输工程是一个复杂而高效的开发框架。它的核心思想是将FPGA获得的数据通过DMA(直接内存访问)技术存入DDR内存,并通过千兆网传输至电脑。具体而言,该框架包括以下几个主要步骤:数据获取、DMA存储、DDR读取和以太网传输。

1.1 数据获取

在基于Zynq的以太网传输工程中,数据获取是整个框架的第一步。利用FPGA的强大处理能力,可以通过各种传感器或电路获取到需要采集的数据。这些数据可以是模拟信号,也可以是数字信号,具体取决于具体的应用场景。

1.2 DMA存储

数据获取完成后,接下来是将数据存储到DDR内存中。为了提高数据传输效率,我们使用DMA技术实现数据的高速传输。DMA直接访问内存,无需CPU的干预,能够大大提高数据传输速度,并减轻CPU的负担。

1.3 DDR读取

在数据存储到DDR内存后,我们需要从处理器端读取这些数据。通过使用Zynq内部的处理器,我们可以轻松地对DDR内存进行读取操作,并将数据传递给后续的处理过程。

1.4 以太网传输

最后一步是将数据通过千兆网传输给电脑。基于Zynq的以太网传输工程利用高速以太网接口,将DDR内的数据通过网络传输至电脑。这为后续的数据分析和处理提供了便利。

二、框架意义

基于Zynq的以太网传输工程作为一个开发框架,具有重要的意义和价值。以下是几个方面的重点:

2.1 高效实现数据采集功能

该框架能够帮助开发者快速实现数据采集功能。通过FPGA强大的处理能力和DMA技术的应用,数据采集的速度和效率都得到大幅提升。对于需要进行数据采集的项目,特别是基于ADC或DAC的项目,该工程能够显著缩短开发周期。

2.2 多项目复用性

基于Zynq的以太网传输工程在设计时考虑了多项目的复用性。通过构建一个通用的开发框架,类似的项目可以共享同一套开发工具和代码库,从而大大减少了重新开发的工作量。根据我们的实践经验,重新开发的工作量通常可以降低至原来的20%以下。

2.3 适用人群广泛

该框架适用于多个领域的开发人员和学习者。模拟半导体芯片的测试或应用工程师可以通过该框架方便地进行数据采集和验证工作。FPGA Zynq需要的嵌入式工程师可以借助该框架快速开发应用。同时,该框架也适合在校学生和教师进行教学和学习。

三、总结

基于Zynq的以太网传输工程是一个高效且稳定的开发框架,能够帮助开发者快速实现数据采集功能,并具备多项目复用性。该框架的设计和应用旨在提高数据处理和传输效率,缩短开发周期,并为模拟半导体芯片测试或应用、FPGA Zynq开发等领域的工程师和学习者提供便利。通过该框架的应用,开发者可以更加高效地进行数据采集和验证工作,从而推动科技的进步和创新。

注:本文所述框架售价为599元,同时提供每小时200元的远程1对1指导服务,旨在帮助初学者克服挑战,更好地理解和应用该框架。

【相关代码 程序地址】: http://nodep.cn/730924441966.html