- 1【C语言】学生宿舍信息管理系统_学生宿舍管理系统c语言

- 2ThreeJS:光线投射与3D场景交互_getraycastersbyobject3d

- 3深入解析 GPT-4o mini:强大功能与创新应用_gpt-4o mini技术详解

- 4深度学习论文精读[8]:ParseNet

- 5音频质量评价体系那些事

- 6推荐项目:VoxPoser——基于语言模型的3D值图进行机器人操作

- 7【Spring云原生】Spring Batch:海量数据高并发任务处理!数据处理纵享新丝滑!事务管理机制+并行处理+实例应用讲解_springbatch多线程处理数据

- 8链表基础知识(一、单链表、头插、尾插、头删、尾删、查找、删除、插入、求表长,合并链表)_单链表的尾插

- 9ubuntu22.04+ROS2 humble+Qt5.12.9+QtCreator11.0环境下,ROS搭配Qt进行GUI界面开发配置过程

- 102024测试工程师核心软技能「情绪管理」,2024最新软件测试算法相关面试大_测试工程师面试 软技能

流片到底为啥那么贵?贵在哪了?_芯片流片

赞

踩

为啥IC设计大厂追求流片Fisrt time rignt?

为啥好多公司流着流着片就消失了?

为啥流片风险那么大?费用那么贵啊?

今天讲讲流片那点事儿。

流片,就是芯片的“试生产”,是集成电路领域不可省略的生产过程。

流片的目的就是测试集成电路设计是否成功。从一个电路图到一块芯片,检验每一个工艺步骤是否可行,检验电路是否具备芯片Spec要求的性能和功能。

如果流片成功,就可以大规模地制造芯片。

如果流片失败,好一点的情况就是追踪BUG优化设计,差一点就是芯片废掉几年白干,更差一点就是砍掉业务或者公司倒闭。

对于一家DesignHouse来说,在芯片研发上的开销大头大概有这么几样:购买IP、购买EDA工具、芯片设计人力成本、芯片流片费用。

流片费用就是开销大头中的大头,最便宜的ASIC流片成本需要几十万一次。180nm的流片成本大概是50W元,55nm的成本在200W元。

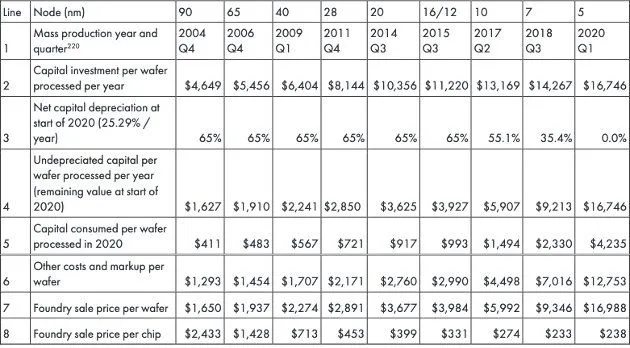

但随着半导体工艺的升级,芯片设计和流片费用都要呈指数级增长。有芯片大厂算过这么一笔账:

- 14nm工艺芯片,流片一次需要300万美元左右(折合人民币2170万)

- 7nm工艺芯片,流片一次需要3000万美元(折合人民币2.17亿)

- 5nm工艺芯片,流片一次更是达到4725万美元(折合人民币3.41亿)

流片到底为啥那么贵?贵在哪了?

其实流片最主要的花费是晶圆(wafer)和掩模板(mask)的制作。

先说晶圆。

根据台积电的代工价目表来看,最先进的制程3nm报价每片晶圆19865美元,折合人民币大概14.2万。

图片来源:The Information Network

如果只看晶圆代工价格,显然是达不到前面所说的百万千万、乃至上亿级别的。

这就不得不提到“层层叠加”的掩模板(掩膜版、光掩模)了。

再说掩模板。

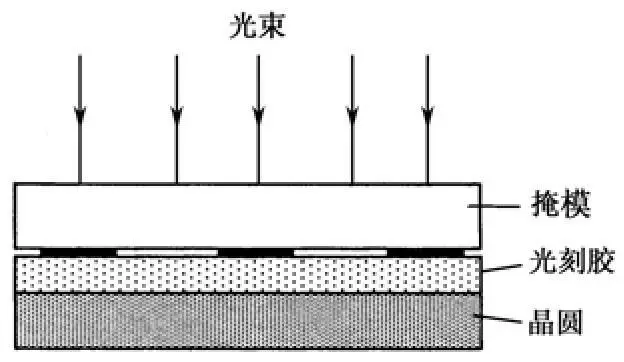

晶圆加工就是把芯片设计版图(包括形状、尺寸、层次等)复制到一块半导体硅片上,其原理类似于胶片照相机的成像和冲洗过程。而掩模,就相当于照相底片。

掩模是光刻过程中原始图形的载体,光刻会通过曝光和显影的过程,把这些图形信息将传递到晶圆片上。所以掩模板的质量就直接决定了光刻的质量。

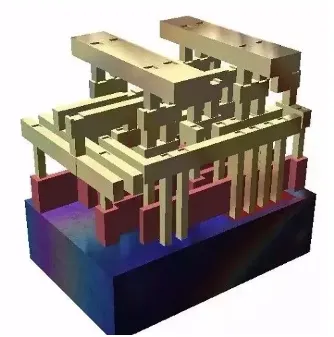

这里需要注意的是,这些图形信息并不是只有一层。因为芯片电路是多层次的、立体的,每层的图形形状也有所不同。芯片制造需要十几次甚至几十次光刻,所以每次光刻都需要一块掩模板。

每制作一层掩模板都需要涂一遍光刻胶,进行一遍前烘、曝光、烘烤、显影等流程。

28nm大概需要40层,14nm大概需要60层,7nm工艺就需要80层甚至上百层了。

之前有报道提到,台积电5nm全光罩流片费用大概在3亿人民币左右(台湾省习惯将掩模板称为光罩)。

用到的掩模板越多,就说明芯片规模越大、越复杂,成本也就越高。

上述的这种昂贵的流片方式叫做Full Mask(全掩膜),就是指承包本次流片所用到的所有掩膜,一般这么干的都是比较“壕横”的大公司。

换句话说,只有在设计完全有把握成功并且准备大批量生产、商用的时候,才会采用Full Mask的流片方式。

那么不能承包的公司/高校,或者产品首次流片还没有足够把握的时候,又该如何呢?

晶圆加工厂贴心地给出了Plan B——MPW(多项目晶圆),多个项目共享某个晶圆。也就是把多个具有相同工艺的集成电路设计放在同一晶圆片上流片加工服务。

这样一来,同一次制造流程就可以承担多个来自不同公司的IC设计的制造任务。等流片结束后,各家公司/高校按照芯片所占的面积分摊费用,领走各自的芯片产品。

这种操作方式可以让流片费用降低90%,也就减少了了芯片研发的成本。

除了晶圆和掩模板的制作费用之外,还有其他的一些费用。比如设备和技术研发投资、人力和维护成本都会分摊到芯片制造中。

还有很多芯片设计并非一次就能流片成功的,而重新流片就需要重复一系列工艺步骤,导致流片成本翻倍。

除了费用之外,流片之后还有另一个风险,那就是无论成功与否,市场可能已经发生变化甚至消失,或者竞争对手已经先一步占领市场。

之前有人说“我之前的公司就是被流片失败搞垮的”还真不是开玩笑,都是业内的血与泪。

对于盈利的商业公司来说,流片尚且要冒如此大的风险。对于经费有限的高校来说,流片肯定就更难了。

流片不易,且行且珍惜。