- 1跟我学Python图像处理丨图像分类原理与案例_图像分类案例

- 2zabbix监控交换机_zabbix添加锐捷交换机

- 3双目项目实战---测距(获取三维坐标和深度信息)_双目相机求解三维坐标点

- 4微信小程序访问webservice(wsdl)+ axis2发布服务端(Java)

- 5chromedriver和selenium的下载以及安装教程(114/116/117.....121版本)_chromedriver 121

- 6Window系统命令行调用控制面板程序_programs|and|features

- 701-Node.js 简史_nodejs历史版本

- 8【STM32】FSMC—扩展外部 SRAM 初步使用 1_stm32 外接 ram

- 9python爬虫爬取淘宝商品并保存至mongodb数据库_tbsearch?refpid=mm_26632258_3504122_32554087

- 10OpenWrt 软路由IPv6 DDNS Socat 端口映射_openwrt socat

【物联网】继续深入探索ADC模拟转数字的原理——Flash ADC&流水线ADC&逐次逼近型SAR ADC_数模转换芯片的工作原理

赞

踩

这篇文章主要弥补上一篇关于ADC的不足,更加深入了解ADC数模转换器的工作原理,举例常见的三种ADC,分别为Flash ADC&流水线ADC&逐次逼近型SAR ADC。

【物联网】深入了解AD/DA转换技术:模数转换和数模转换

前些天发现了一个巨牛的人工智能学习网站,通俗易懂,风趣幽默,忍不住分享一下给大家。点击跳转到网站:人工智能

一、模拟信号和数字信号

- 模拟信号是一种连续变化的信号,它可以在一定范围内取任意数值。在电子设备中,模拟信号通常由电压或电流的变化来表示。

- 数字信号是一种离散的信号,它只能取有限个数值。在数字设备中,通常使用二进制来表示数字信号,即用0和1来表示不同的状态。

举个例子:

假设从0V到8V,连续的过程就是模拟信号,如果每间隔1V识别一次电压,对应的电压值用二进制数表示,则对二进制数就是数字信号。

那我们要思考一个问题就是,一个连续变化的模拟信号是怎样变成数字信号的呢?

这就要使用我们ADC中最重要的部分——ADC模数转换芯片。

二、ADC转换芯片

1、Flash ADC

Flash ADC(快闪式模数转换器)是一种高速的模数转换器,它能够将模拟信号转换为数字信号。Flash ADC的原理是基于比较器和编码器的工作原理。

Flash ADC包含了一系列比较器,每个比较器都与一个参考电压相关联。当输入的模拟信号通过比较器进行比较时,每个比较器都会产生一个数字输出,表示输入信号与参考电压的大小关系。这些数字输出经过编码器进行编码,最终输出一个二进制数字,表示输入模拟信号的大小。

由于Flash ADC中的比较器数量很大,因此它可以实现非常高的转换速度。然而,由于需要大量的比较器和编码器,Flash ADC的成本和功耗较高,因此在实际应用中通常用于需要高速转换的场合。

实现的细节:

同样是使用上面0V到8V的例子,先将8V电压接地,中间接上8个相同阻值的电阻,点一个点7/8电阻得到7V,下一个点6/8个电阻得到6V…以此类推,得出7个电位的电压,然后在电阻间加上比较器,也就是1V电压到反相端,另一端接上输入信号,接入输入比1V高,比较器输出高电平1,相反,如果比1V小,就输出低电平0,以此类推在所有的电阻间都加上比较器,将所有输入引脚接在一起,假设输入的是5.1V,下面的5个比较器输出1,上面的比较器输出0,得到的二进制数字就是0011111,同理假设是4.9V,输出的二进制数字是0001111,按照这个规律得到每个区间的电压对应的二进制数字。

理论上模拟信号有无尽的小数,与基准电压不可能完全相等,所以并不会发生要冲裁的情况。

下一个环节就是加上D型锁存器,将所有控制端拉到外面来控制,当控制端是1,那输入端是多少,锁存器就输出相同的结果,这个过程会出现轻微震荡,会出现输出也跟着跳变,当控制端为0时,所有结果就会被锁定,这时候不论前面怎么变,后面输出都不会改变,所以可以把锁存器的控制端:

1理解为读取指令

0理解为锁定指令

下一步将这些结果转化为二进制数

0-1V-----000

1-2V-----001

2-3V-----010

3-4V-----011

4-5V-----100

5-6V-----101

6-7V-----110

7-8V-----111

- 1

- 2

- 3

- 4

- 5

- 6

- 7

- 8

正好八种结果用3bit二进制数表示,那么这部分就是要用编码器来完成。

上面使用的是3bit分辨率,所以只能识别1V的电压,要想精度更高,就需要更多位

分辨率为4bit,精度为0.5V,16个比较器和触发器

分辨率为10bit,精度为0.0078V,1023个比较器触发器

分辨率到16bit,精度为0.00012V,65535个比较器和触发器

所以Flash ADC的缺点就是精度越高,内部元器件越多,内部功耗和面积就会增大,要解决这个问题外面可以用流水线ADC。

2、流水线ADC

流水线ADC是一种高速的模数转换器,它将模拟信号转换为数字信号。它的工作原理基于流水线结构,可以实现高速的并行转换。

-

Sample and Hold(采样保持):首先,输入的模拟信号会经过采样保持电路,这个电路会对模拟信号进行采样并且在一定时间内保持这个采样值。

-

分段转换:流水线ADC将整个转换过程分成了多个阶段,每个阶段都负责对输入信号的一部分进行转换。每个阶段包含了一个比较器和一个数字编码器。比较器会将输入信号与参考电压进行比较,然后输出一个比较结果。数字编码器会将比较结果转换为数字输出。

-

Pipeline Stages(流水线阶段):每个阶段的转换结果会传递给下一个阶段,这样整个转换过程被分成了多个阶段,每个阶段都可以并行地进行转换。这样可以大大提高转换速度。

-

数字输出:最后,每个阶段的数字输出会被整合起来,形成最终的数字输出。

举例说明:

我们以4bit分辨率举例,参考电压为1V,0.5V为基准电压,超过0.5V输出1,低于0.5V输出0;假设我们检测0.7V,

- 第一层大于0.5V,所以应该输出1;

- 然后将(0.7V-基准电压0.5V)乘以2倍得到0.4V,这个时候第二层0.4V小于基准电压0.5V,所以输出0;

- 将上一层的0.4乘以2倍得到0.8V,所以第三层大于0.5V,输出1;

- 然后将(0.8V-基准电压)乘以2倍得到0.6V,所以第四层大于基准电压0.5V,所以输出的是1;

得到所有的的二进制数为1011,遵循的公式就是大于基准电压0.5V就减去基准电压再乘以二倍,小于基准电压直接乘以二倍。

Flash ADC和流水线ADC相比,同样是4bit,流水线只需要4个比较器,而普通Flash ADC需要16个比较器,功耗降低,体积变小,但是对制作工艺和电路要求高很多。

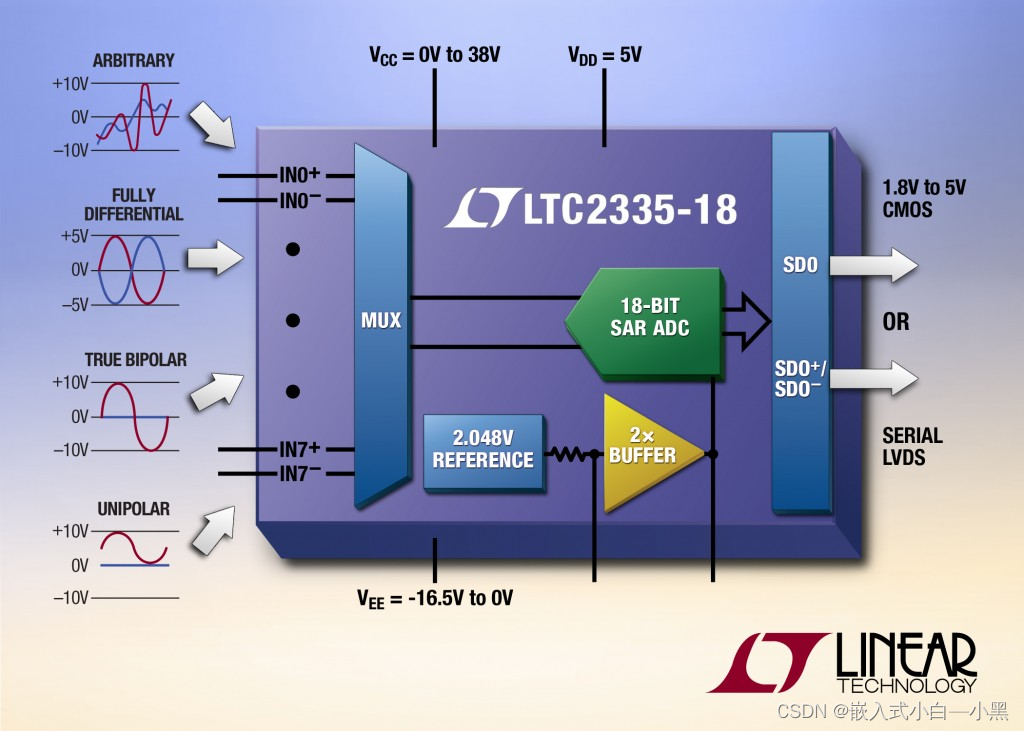

3、逐次逼近型SAR ADC

逐次逼近型SAR(Successive Approximation Register) ADC是一种常见的模数转换器,用于将模拟信号转换为数字信号。它的工作原理是通过逐步逼近的方式来确定模拟输入信号的数字表示。

-

采样保持:首先,输入的模拟信号会经过采样保持电路,这个电路会对模拟信号进行采样并在一定时间内保持这个采样值。

-

DAC输出:采样保持后的模拟信号会被送入一个数字模拟转换器(DAC),DAC会将模拟信号转换为数字形式,并将这个数字信号送入逐次逼近逻辑电路。

-

逐次逼近逻辑:逐次逼近逻辑会根据DAC输出的数字信号逐步逼近输入模拟信号的大小。它首先将DAC输出的最高位设置为1,然后将这个数字与输入模拟信号进行比较。如果DAC输出的数字大于输入模拟信号,逐次逼近逻辑将保持这个最高位为1,否则将其置为0。然后它会将次高位设置为1,再次进行比较。这个过程会一直持续下去,直到所有位都被确定。

-

数字输出:一旦逐次逼近逻辑确定了所有位的值,它就会产生一个完整的数字输出,表示输入模拟信号的大小。

举例说明:

以5bit分辨率为例,也就是2的5次方32个区间,假设参考电压为32mv,正好每个区间1mv,假设测量21.5mV,用32的一半16mV做比较,比它大首位输出1,下一个用16-32mV的一半24mV做比较,比它小输出0,再下一位用16-24mV的一半20mV作比较,比它大输出1,同理得到最终结果为10101。

逐次逼近型SAR ADC的优点是具有较高的分辨率和较低的功耗。它在许多应用中都有广泛的应用,比如传感器接口、音频处理和通信系统等领域。然而,由于逐次逼近的特性,它的转换速度通常比较慢,因此在一些需要高速转换的应用中可能不适用。