- 1Anaconda 安装、配置、使用详细教程_anaconda详细教程及使用教程惜

- 2清理Anaconda_anaconda占用空间太大

- 3Uncaught Error: [$injector:nomod] Module 'xxx' is not available! You either misspelled the m_angular中出现module 'ui.select' is not available! you

- 4真正的官方GPT4.0国内版

- 5部署你自己的导航站-dashy_dashy 配置

- 6如何用GPT进行成像光谱遥感数据处理?

- 7【 华为OD机试 2023】 上班之路/是否能到达公司(C++ Java JavaScript Python)_python机考:上班之路

- 8QT入门学习(三)_writedatagram

- 9【Linux权限】Shell命令及运行原理 | Linux权限管理 | 粘滞位_linux 怎样打开超级权限的shell

- 10【ES数据可视化】kibana实现数据大屏_怎么把kibana中的图标集成到自己的项目中

第一个Xilinx Vitis IDE入门helloworld程序

赞

踩

操作系统:Ubuntu 18.04.4 LTS

命令lsb_release -a

安装Vitis

https://www.xilinx.com/support/download/index.html/content/xilinx/en/downloadNav/vitis.html

在线安装网速很慢,离线下载安装包,Xilinx_Vitis_2019.2_1106_2127.tar 30.76GB

解压缩

tar xvf Xilinx_Vitis_2019.2_1106_2127.tar

安装,需要至少120G磁盘空间,最好150G以上

cd Xilinx_Vitis_2019.2_1106_2127/

./xsetup

安装完成

安装petalinux

略

进入正题

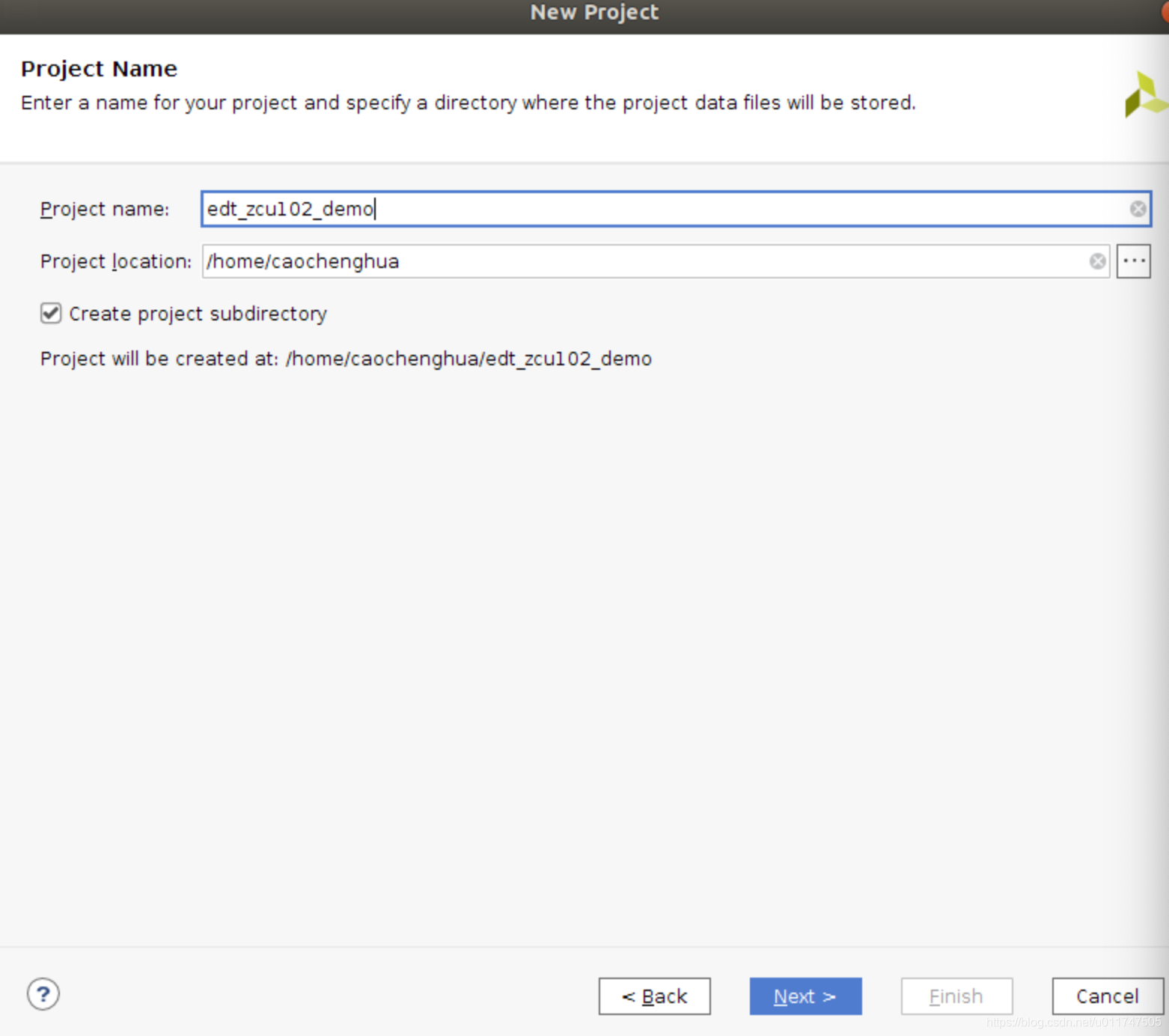

首先打开Vivado 2019.2,File->New Project

Next,项目名称edt_zcu102_demo

默认

接下来的两个界面Add Sources和Add Constraints都直接Next,然后选择Boards,选择ZCU102,Next

Finish,之后项目自动打开,点Create Block Design

设计名称edt_zcu102_demo,然后OK

Add IP,如下图红色箭头所示

输入znyq进行过滤,并选择Zynq UltraScale+ MPSoC

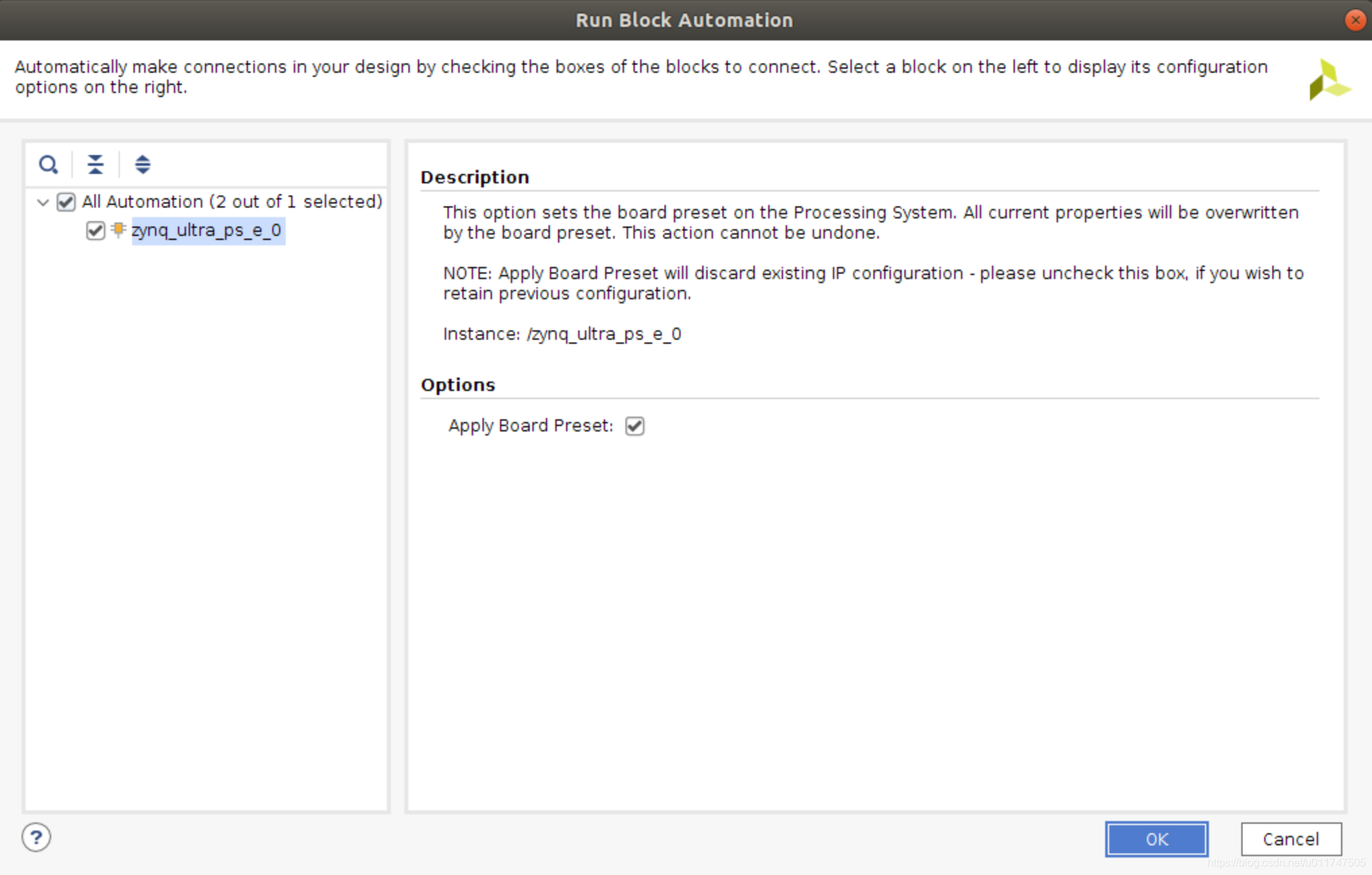

点击Run Block Automation

默认,点OK

双击红框位置,查看自动化效果

点左侧PS-PL Configuration,展开,并将红框中的勾选框取消勾选,结果如图,OK

空白处右键,点击Validate Design

验证成功提示

右键Design Sources下的文件,点击Create HDL Wrapper

默认,点OK

创建完成之后,展开edt_zcu102_demo_wrapper,右键左侧红箭头,然后点Generate Output Products…

默认,点Generate

并生成最终的edt_zcu102_wrapper.xsa文件【TODO:此过程参考另一个教程】

使用petalinux生成linux镜像

petalinux和bsp(Board Support Packages)文件这里下载https://www.xilinx.com/support/download/index.html/content/xilinx/en/downloadNav/embedded-design-tools.html

我的petalinux安装在~/Desktop/petalinux/下

执行命令source ~/Desktop/petalinux/settings.sh

进入bsp文件所在目录

创建工程命令petalinux-create -t project -s xilinx-zcu102-v2019.2-final.bsp

根据edt_zcu102_wrapper.xsa文件所在目录(注意不是文件,也不要拷贝.xsa至当前目录下)重新配置petalinux-config --get-hw-description='/home/caochenghua/project_1edt_zcu102/'

参考文献

ug1209-embedded-design-tutorial.pdf

下载地址https://www.xilinx.com/support/documentation/sw_manuals/xilinx2019_2/ug1209-embedded-design-tutorial.pdf