热门标签

热门文章

- 1多.net环境下, 配置C#运行与对应的.net版本环境

- 2ElasticSearch篇——实现京东搜索(含爬虫操作/解析数据到ES/精准查询/对接前端/高亮查询)一篇文章带你速通~~~~~~~~_elasticsearch加爬虫搜集

- 3php nfs上的性能优化,nfs的优化

- 4【毕业设计】基于微信小程序的校园失物招领小程序 微信失物招领小程序 失物招领微信小程序_失误巡回小程序毕业设计引言

- 5luci的实现框架 ----我的笔记(2.3)

- 6短视频去水印接口支持全网解析源码/自定义API接口_巨量创意去水印接口

- 7服务熔断Hystrix高级_## 服务熔断hystrix高级

- 8Mac OS卸载JDK_mac 卸载jdk

- 9Ubuntu Steam 玩游戏的一些踩坑_ubuntu中玩steam游戏

- 10健身房预约管理系统(源码+文档)

当前位置: article > 正文

【vivado】 clock wizard 时钟IP_vivado clock wizard ip

作者:不正经 | 2024-04-28 15:33:09

赞

踩

vivado clock wizard ip

一、前言

MMCM和PLL是在FPGA设计中不可避免需要使用到的时钟资源,对于其功能及使用方法的理解是正确进行FPGA设计的前提。

二、Xilinx 时钟 IP配置

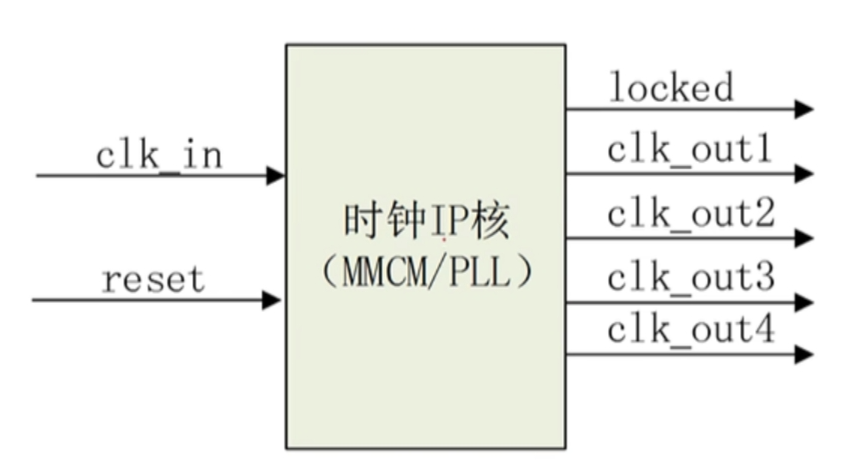

vivado中使用时钟向导(Clocking Wizard)配置时钟IP核,其框图如下:

clk_in 输入时钟,一般为班上晶振引入时钟或者serdes恢复时钟以及其他专用时钟引脚输入时钟;

复位信号RST需要连接到用户逻辑——如果在没有时钟的情况下RST直接接地会导致clk_wiz无法工作;

locked信号,从 0 变为1 ,表示输出的时钟达到稳定。

三、locked信号

MMCM或PLL的输出LOCKED信号一般用来作为复位完成的状态标志位。原因如下:与PLL输出时钟驱动的逻辑单元需要保持复位状态,直到PLL的LOCKED信号输出拉高为时,此刻表明时钟被锁定,PLL处于稳定的状态,因此LOCKED在设计常会用作复位信号。

四、约束

时钟IP会自动在综合实现中生成相应的时钟约束,因此不需要在约束文件中在对相关时钟进行时钟约束。

声明:本文内容由网友自发贡献,不代表【wpsshop博客】立场,版权归原作者所有,本站不承担相应法律责任。如您发现有侵权的内容,请联系我们。转载请注明出处:https://www.wpsshop.cn/w/不正经/article/detail/502984

推荐阅读

相关标签