- 1物联网数据处理技术课程设计——基于python实现的智能图书馆借阅管理系统(OpenCV+MySQL)_图书管理系统python

- 2码云Gitee 上传代码出现的错误(一)_error: cannot pull with rebase: you have unstaged

- 3Flink:详细的不能再详细的安装步骤(三)[安装步骤]

- 4『现学现忘』Git基础 — 36、标签tag(一)_python git tag

- 5什么是PSD(功率谱密度)_psd谱

- 6重装操作系统win10+重装sqlserver+数据库可视化工具_sql server可视化工具

- 7TransE模型的简单介绍&TransE模型的python代码实现

- 8微信小程序自定义tabbar导航栏,中间凸出样式_微信小程序底部tab栏特殊样式

- 9程序员如何通过被动收入实现“暴富”_程序员 被动收入

- 10ChatGPT爆火网络背后的故事?_chatgpt 故事背景

10G Ethernet Subsystem 基于K7芯片的UDP通讯_k7开源的udp ip核

赞

踩

I. 引言

背景介绍

以太网作为一种广泛应用于计算机网络中的通信协议,已经成为现代通信领域中不可或缺的技术。在嵌入式系统和网络应用中,以太网的应用也变得越来越重要。为了满足不同应用需求,Xilinx公司开发了Ethernet Subsystem软核,为设计师提供了一种快速、灵活且可定制的以太网解决方案。

Ethernet Subsystem是Xilinx Vivado开发套件中的一个重要组件,它提供了在FPGA上实现以太网功能所需的关键功能模块和IP核。通过使用Ethernet Subsystem,设计师可以轻松地集成以太网功能到他们的嵌入式系统中,而无需从头开始设计和实现复杂的以太网协议。

Ethernet Subsystem的核心组件包括MAC层、PHY层和处理器系统接口。MAC层是以太网通信中的介质访问控制层,负责处理帧的发送和接收,以及与PHY层之间的接口。PHY层是物理层,负责处理电气信号的发送和接收,以及与MAC层之间的接口。处理器系统接口提供了与处理器系统的连接,使设计师能够通过处理器来控制和配置Ethernet Subsystem。

Ethernet Subsystem的优势在于其高度可定制性和灵活性。设计师可以根据具体应用需求,选择不同的配置选项,包括速率、协议支持、接口类型等。此外,Ethernet Subsystem还提供了丰富的软件驱动程序和API,简化了软件开发和集成过程。

II. 技术概述

技术的定义和背景知识

以太网:以太网是一种广泛应用于计算机网络中的通信协议,它定义了数据在局域网中的传输方式和规范。以太网在局域网中得到广泛应用,支持高速数据传输和实时通信。

FPGA(Field-Programmable Gate Array):FPGA是一种可编程逻辑器件,具有灵活性和可重构性。它由一系列可编程的逻辑单元和可编程的连线资源组成,可以根据需要重新配置和重新编程,实现不同的数字电路功能。

Vivado开发套件:Vivado是Xilinx公司提供的一套综合设计工具,用于FPGA和SoC系统的设计、仿真、综合和实现。Vivado提供了丰富的IP核和开发工具,简化了硬件设计和开发过程。

IP核:IP核是一种可重用的硬件模块,提供了特定功能的设计和实现。Ethernet Subsystem作为一种IP核,提供了以太网通信功能的集成解决方案,简化了以太网功能的设计和开发过程。

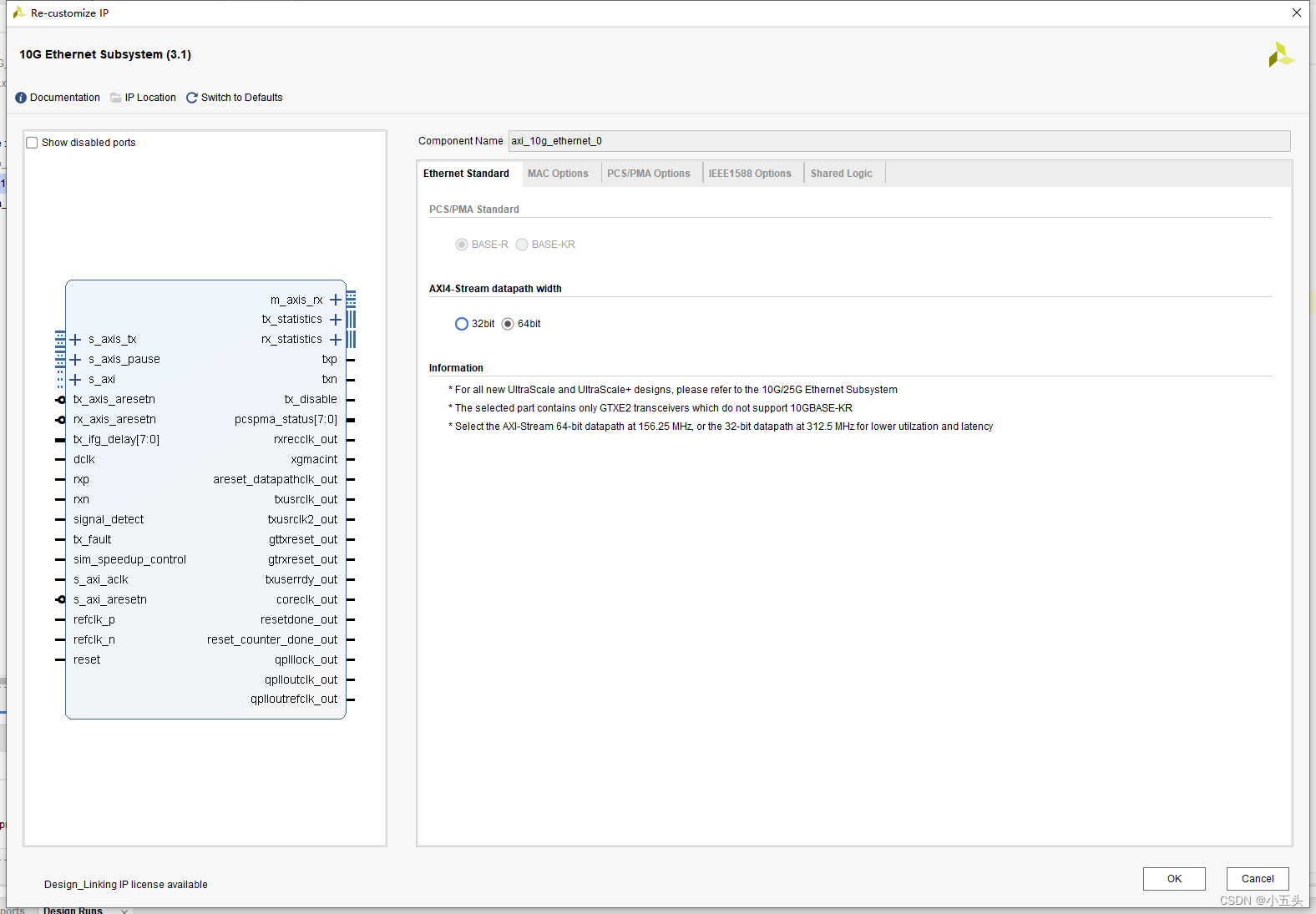

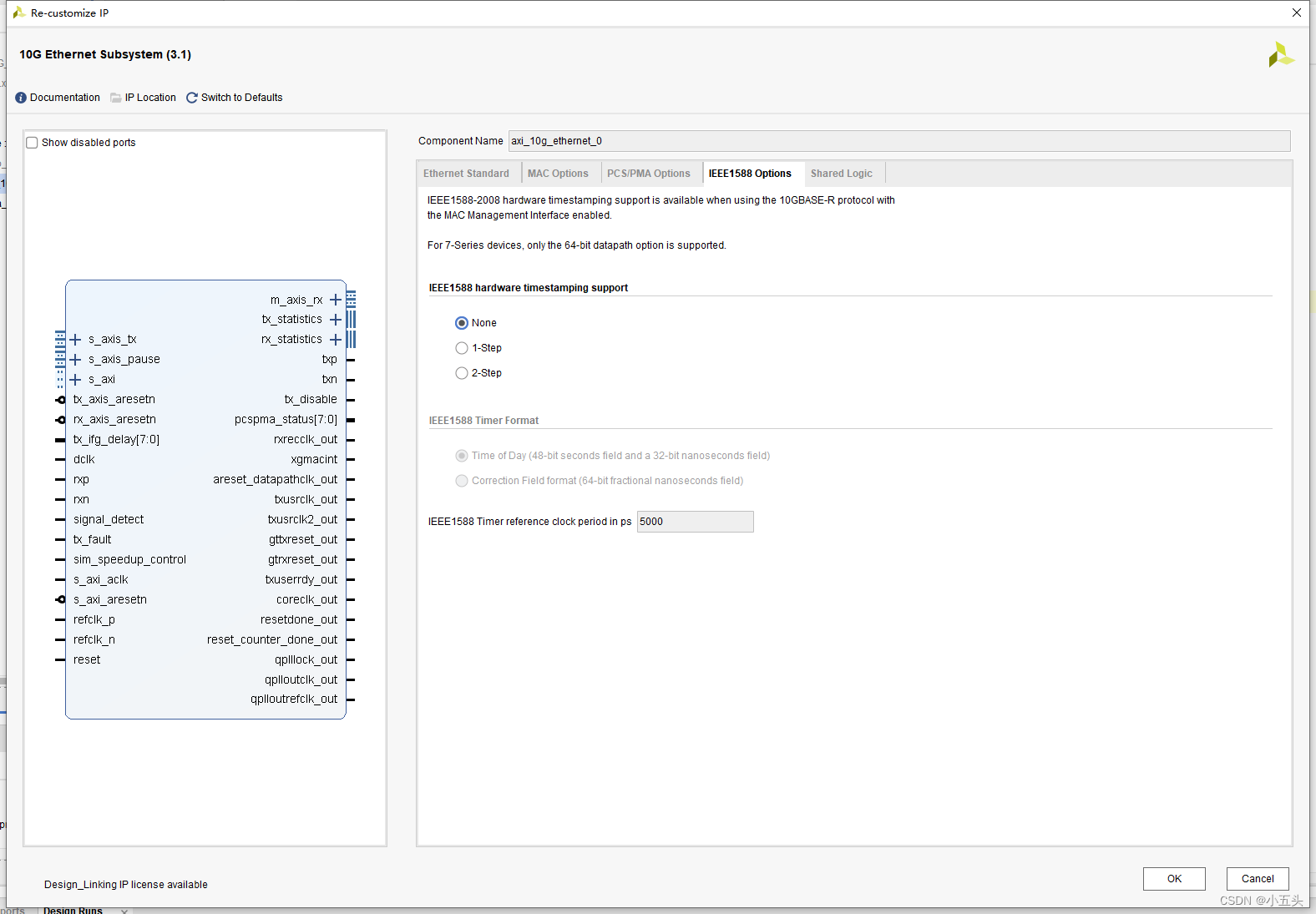

III.IP核的建立

此选项不进行共享时钟逻辑。优点接口少好操作,缺点只可以建立一个IP核。(我有一篇文章介绍了如何进行多个核互联)传送门:FPGA光纤Aurora_8B_10B_fpga aurora的实际带宽-CSDN博客

- //----------- Begin Cut here for INSTANTIATION Template ---// INST_TAG

- axi_10g_ethernet_0 your_instance_name (

- .tx_axis_aresetn(tx_axis_aresetn), // 复位 。 需拉低一段时间

- .rx_axis_aresetn(rx_axis_aresetn), // 复位 。 需拉低一段时间

- .tx_ifg_delay(tx_ifg_delay), // input wire [7 : 0] tx_ifg_delay

- .dclk(dclk), // DRP 时钟

- .txp(txp), // 光口

- .txn(txn), // 光口

- .rxp(rxp), // 光口

- .rxn(rxn), // 光口

- .signal_detect(signal_detect), // input wire signal_detect

- .tx_fault(tx_fault), // 检测光模块 状态信号

- .tx_disable(tx_disable), // 连接光模块的控制

- .pcspma_status(pcspma_status), // output wire [7 : 0] pcspma_status

- .sim_speedup_control(sim_speedup_control), // 使用此信号,可缩短计算时间1 用于仿真

- .rxrecclk_out(rxrecclk_out), // 时钟

- .s_axi_aclk(s_axi_aclk), // input wire s_axi_aclk

- .s_axi_aresetn(s_axi_aresetn), // input wire s_axi_aresetn

- .xgmacint(xgmacint), // output wire xgmacint

- .areset_datapathclk_out(areset_datapathclk_out), // output wire areset_datapathclk_out

- .txusrclk_out(txusrclk_out), // output wire txusrclk_out

- .txusrclk2_out(txusrclk2_out), // output wire txusrclk2_out

- .gttxreset_out(gttxreset_out), // output wire gttxreset_out

- .gtrxreset_out(gtrxreset_out), // output wire gtrxreset_out

- .txuserrdy_out(txuserrdy_out), // output wire txuserrdy_out

- .coreclk_out(coreclk_out), // output wire coreclk_out

- .resetdone_out(resetdone_out), // output wire resetdone_out

- .reset_counter_done_out(reset_counter_done_out), // output wire reset_counter_done_out

- .qplllock_out(qplllock_out), // output wire qplllock_out

- .qplloutclk_out(qplloutclk_out), // output wire qplloutclk_out

- .qplloutrefclk_out(qplloutrefclk_out), // output wire qplloutrefclk_out

- .refclk_p(refclk_p), // input wire refclk_p

- .refclk_n(refclk_n), // input wire refclk_n

- .reset(reset), // input wire reset

- .s_axi_araddr(s_axi_araddr), // input wire [10 : 0] s_axi_araddr

- .s_axi_arready(s_axi_arready), // output wire s_axi_arready

- .s_axi_arvalid(s_axi_arvalid), // input wire s_axi_arvalid

- .s_axi_awaddr(s_axi_awaddr), // input wire [10 : 0] s_axi_awaddr

- .s_axi_awready(s_axi_awready), // output wire s_axi_awready

- .s_axi_awvalid(s_axi_awvalid), // input wire s_axi_awvalid

- .s_axi_bready(s_axi_bready), // input wire s_axi_bready

- .s_axi_bresp(s_axi_bresp), // output wire [1 : 0] s_axi_bresp

- .s_axi_bvalid(s_axi_bvalid), // output wire s_axi_bvalid

- .s_axi_rdata(s_axi_rdata), // output wire [31 : 0] s_axi_rdata

- .s_axi_rready(s_axi_rready), // input wire s_axi_rready

- .s_axi_rresp(s_axi_rresp), // output wire [1 : 0] s_axi_rresp

- .s_axi_rvalid(s_axi_rvalid), // output wire s_axi_rvalid

- .s_axi_wdata(s_axi_wdata), // input wire [31 : 0] s_axi_wdata

- .s_axi_wready(s_axi_wready), // output wire s_axi_wready

- .s_axi_wvalid(s_axi_wvalid), // input wire s_axi_wvalid

- //axis_tx数据接口 发送

- .s_axis_tx_tdata(s_axis_tx_tdata), // input wire [63 : 0] s_axis_tx_tdata

- .s_axis_tx_tkeep(s_axis_tx_tkeep), // input wire [7 : 0] s_axis_tx_tkeep

- .s_axis_tx_tlast(s_axis_tx_tlast), // input wire s_axis_tx_tlast

- .s_axis_tx_tready(s_axis_tx_tready), // output wire s_axis_tx_tready

- .s_axis_tx_tuser(s_axis_tx_tuser), // input wire [0 : 0] s_axis_tx_tuser

- .s_axis_tx_tvalid(s_axis_tx_tvalid), // input wire s_axis_tx_tvalid

- .s_axis_pause_tdata(s_axis_pause_tdata), // input wire [15 : 0] s_axis_pause_tdata

- .s_axis_pause_tvalid(s_axis_pause_tvalid), // input wire s_axis_pause_tvalid

- //axis_rx数据接口 接收

- .m_axis_rx_tdata(m_axis_rx_tdata), // output wire [63 : 0] m_axis_rx_tdata

- .m_axis_rx_tkeep(m_axis_rx_tkeep), // output wire [7 : 0] m_axis_rx_tkeep

- .m_axis_rx_tlast(m_axis_rx_tlast), // output wire m_axis_rx_tlast

- .m_axis_rx_tuser(m_axis_rx_tuser), // output wire m_axis_rx_tuser

- .m_axis_rx_tvalid(m_axis_rx_tvalid), // output wire m_axis_rx_tvalid

- .tx_statistics_valid(tx_statistics_valid), // 数据有效信号

- .tx_statistics_vector(tx_statistics_vector), // 状态标志信号

- .rx_statistics_valid(rx_statistics_valid), // 数据有效信号

- .rx_statistics_vector(rx_statistics_vector) // 状态标志信号

- );

顶层接口定义

- module 10G_ethernet(

- input sys_clk_100m ,//板卡的系统时钟

- input refclk_n_0 ,//光口时钟

- input refclk_p_0 ,

- input rxn_0 ,//光口接收

- input rxp_0 ,

- output txp_0 ,//光口发送

- output txn_0 ,

- output led ,//工作状态指示信号

- output tx_dis //通道开启信号

- );

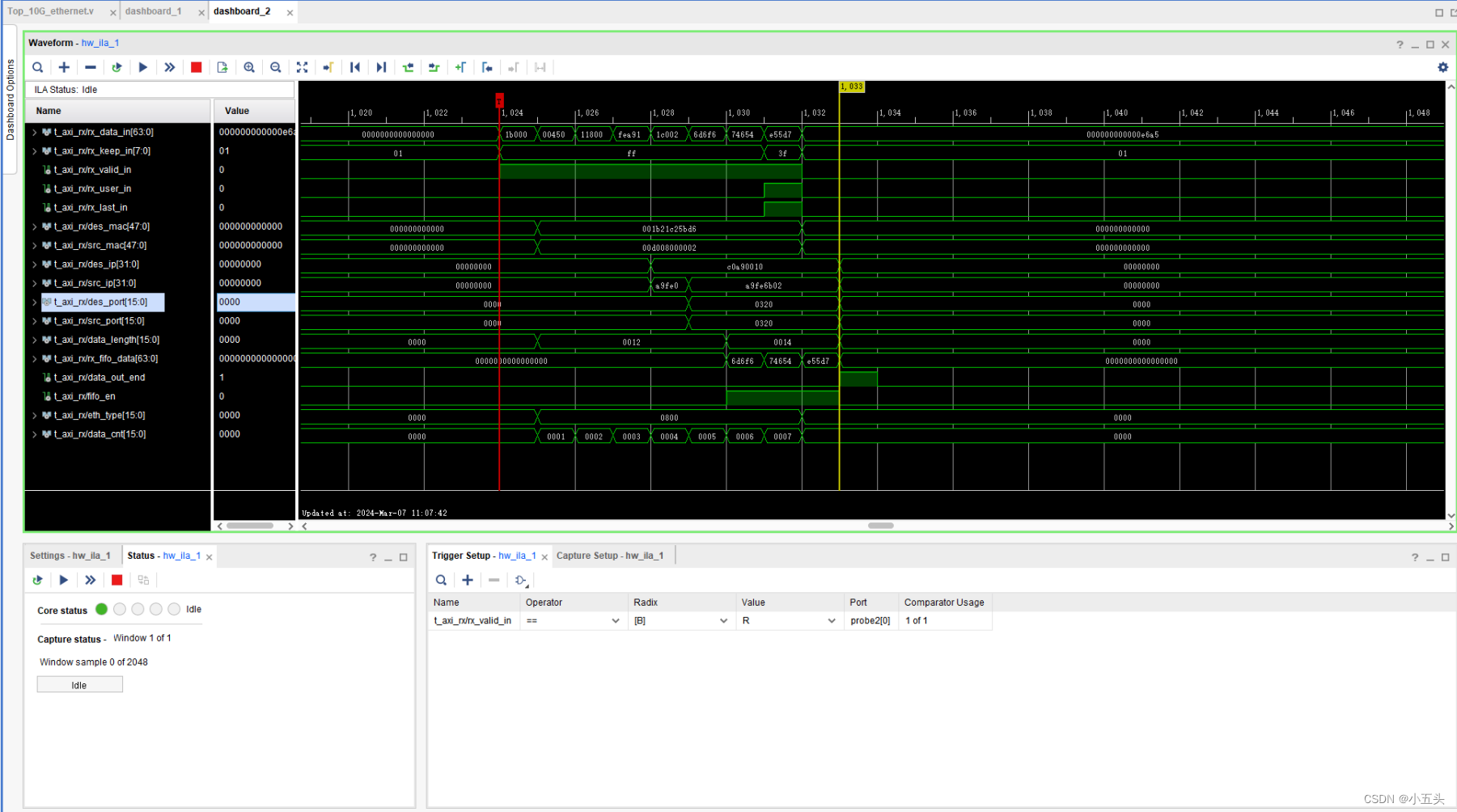

IV.功能验证

需要准备工具:10G网卡一个(PCIE接口)、支持10G的光模块两个、光纤线缆一对。

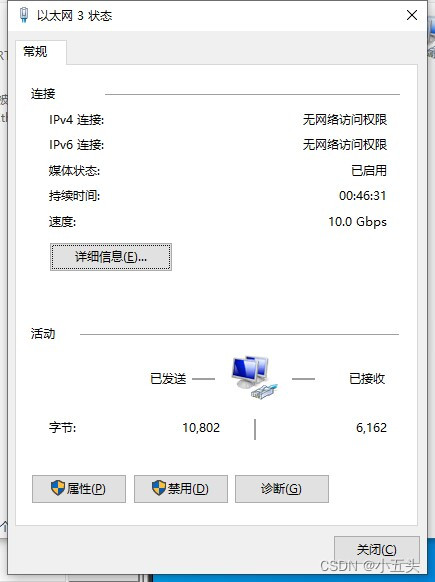

程序下载完成后,10G网卡灯亮起,证明与10G Ethernet Subsystem 核link成功,这时可查看电脑的网络现实状态。

配置好IP地址后,可使用网络传输助手进行通讯。

Des_ip : c0a900010 发送端主机的IP地址 192.168.0.16

Des_mac : 发送端主机的MAC地址 00-1b-21-c2-5b-d6

Des_port : 源端口号 0800

Eth_type : 长度类型

Src_ip :a9fe6b02 源ip 开发板ip地址 169.254.107.2

Src_mac :源mac地址 开发板mac地址 00-d0-08-00-00-02

Scr_port :目的端口号 与源端口号保持一致即可

Rx_last_in :表示一个数据包的结束

Rx_user_in:0表示接收的数据包坏的 , 1表示接收的数据包好的

Rx_valid_in :数据有效信号

Fifo_en :数据有效信号

Rx_data_in :数据信号

Rx_fifo_data :数据信号

V. 技术发展趋势

目前的技术趋势

高速化:随着通信需求的增加,以太网的传输速度也在不断提高。目前,以太网技术已经发展到了多千兆以太网(Multi-Gigabit Ethernet)和万兆以太网(10 Gigabit Ethernet)的级别。Ethernet Subsystem软核也在不断优化和升级,以支持更高的传输速度和更大的带宽需求。

硬件加速:为了满足高性能计算和数据中心的需求,以太网功能通常需要在FPGA上进行硬件加速。通过使用Ethernet Subsystem软核,设计师可以将以太网功能与其他硬件加速器和处理器系统相结合,实现更高效的数据处理和传输。

物联网(IoT)支持:随着物联网的快速发展,对于连接性和通信能力的需求也在不断增加。Ethernet Subsystem软核可以支持物联网设备的连接和通信,提供稳定可靠的以太网通信功能,使物联网设备能够与云端和其他设备进行数据交互。

安全性增强:随着网络安全威胁的增加,对于以太网通信的安全性要求也越来越高。Ethernet Subsystem软核在安全性方面也在不断改进,提供更强大的数据加密和身份验证功能,以保护通信数据的安全性和完整性。

软件定义网络(SDN)支持:软件定义网络是一种新兴的网络架构,通过将网络控制平面和数据平面分离,实现网络的灵活性和可编程性。Ethernet Subsystem软核可以与SDN技术集成,提供可编程的网络功能和灵活的数据流控制。

VI. 参考文献

1. Xilinx Inc. "Vivado Design Suite User Guide: Creating and Packaging Custom IP". [Online]. Available: https://www.xilinx.com/support/documentation/sw_manuals/xilinx2021_1/ug1119-vivado-creating-packaging-custom-ip.pdf

2. Xilinx Inc. "Vivado Design Suite User Guide: Using IP Catalog and IP Packager". [Online]. Available: https://www.xilinx.com/support/documentation/sw_manuals/xilinx2021_1/ug1118-vivado-ip-catalog.pdf

3. Xilinx Inc. "Vivado Design Suite User Guide: Designing with IP". [Online]. Available: https://www.xilinx.com/support/documentation/sw_manuals/xilinx2021_1/ug1116-vivado-ip.pdf

4. Xilinx Inc. "Vivado Design Suite User Guide: Embedded Design Using IPi". [Online]. Available: https://www.xilinx.com/support/documentation/sw_manuals/xilinx2021_1/ug1165-vivado-embedded-design.pdf

5. Xilinx Inc. "AXI Ethernet Subsystem Product Guide". [Online]. Available: https://www.xilinx.com/support/documentation/ip_documentation/axi_ethernet/v4_1/pg138-axi-ethernet.pdf

6. Xilinx Inc. "Vivado Design Suite Tutorial: Creating an Ethernet Subsystem using IP Integrator". [Online]. Available: https://www.xilinx.com/support/documentation/sw_manuals/xilinx2021_1/ug1114-vivado-tutorial-creating-ethernet-subsystem.pdf