热门标签

热门文章

- 1OpenGL ES基础-(2)着色器语言(GLSL)_opengl es glsl

- 2enum中使用中文 unity_Unity编辑器开发,使用CustomPropertyDrawer实现枚举中文显示

- 3【微信小程序】实现打开并下载服务器上面的pdf文件到手机_微信小程序下载pdf

- 4msvcr110.dll文件缺失的多种有效解决方法,一键修复msvcr110.dll

- 5RabbitMQ中死信队列和延迟队列_php rabbitmq队列和延迟队列有啥区别

- 62013国二c语言真题,2013年3月全国计算机二级c语言真题

- 7delphi 图像旋转速度_自动驾驶汽车视觉- 图像特征提取与匹配技术

- 8图形 4.2 SSAO算法 屏幕空间环境光遮蔽_u3d ssao

- 9LLaMA-Factory微调(sft)ChatGLM3-6B保姆教程_llamafactory微调

- 10大数据——Flink 知识点整理_flink机器学习

当前位置: article > 正文

利用Logsim实现4位一个二进制数的补码器电路

作者:不正经 | 2024-05-16 07:26:46

赞

踩

利用Logsim实现4位一个二进制数的补码器电路

提示:文章写完后,目录可以自动生成,如何生成可参考右边的帮助文档

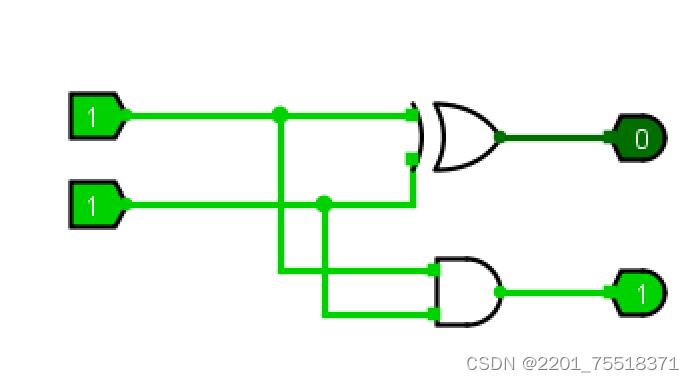

一、1bit半加器

、1bit半加器使用一个异或门和一个与门组成,异或门表示两个数相加后的数,与门表示其进制

二、1bit全加器

全加器可看作是两个半加器的叠加,与半加器相比还可接收一个低位进位输入信号

三、4bit二进制补码器

根据补码的规则,若输入的数位正数则补码和原码相同,若为负数则除符号位其余的全部取反再加1。因此,可将每位数同符号位用异或门进行计算,判断是否需要取反,然后进行计算

总结

此次实现补码器既是对补码原理的熟悉,也是对logsim的熟悉

声明:本文内容由网友自发贡献,不代表【wpsshop博客】立场,版权归原作者所有,本站不承担相应法律责任。如您发现有侵权的内容,请联系我们。转载请注明出处:https://www.wpsshop.cn/w/不正经/article/detail/577498

推荐阅读

相关标签