- 1毕业仅1年,干Python赚了50W!网友:不是吹的_学会python可以挣多少钱

- 2Text Summarization with Pretrained Encoders 论文笔记

- 3学习资料|常用的一些CMD运行命令,整理的比较齐全_cmd启动程序命令

- 4Gerrit SSH 配置使用_gerrit配置ssh

- 5一些常用linux的安全设置_linux系统安全配置

- 6算法笔记——DFS深度优先搜索_算法笔记你设想我们现在以第一视角身处一个巨大的迷宫中,没有上帝视角

- 7NUC980开源项目15-编译默认配置uboot_config_sys_bootm_len

- 8MongoDB的基础使用

- 9SLAM精度评估-EVO的使用_evo精度评估

- 1014 —— npm —— 基本使用 ——初始化项目

【友晶科技】基于FPGA的贪吃蛇游戏设计(一)——整体介绍_fpga贪吃蛇小游戏

赞

踩

基于FPGA的贪吃蛇游戏设计

DE10-Standard/DE1-SoC/DE2-115

贪吃蛇游戏源于1976年,是一款非常经典的游戏,这里不过多介绍,直接开始在FPGA上设计吧!

(本文为设计的总体介绍,关于每个模块的实现参见后期连载文章。)

准备工作

硬件平台:DE10-Standard、DE1-SoC和DE2-115三选一

软件平台:Quartus 18.1

其他配件:一根VGA线,一台VGA 显示器

硬件框架

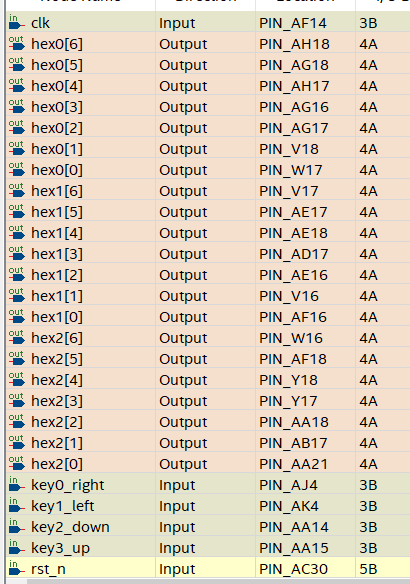

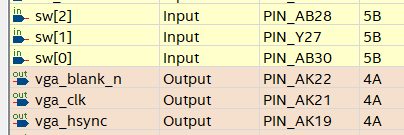

本系统要用到开发板的4个按键、4个滑动开关和3个数码管,然后外接1个VGA显示器。

游戏过程

游戏分四个状态:

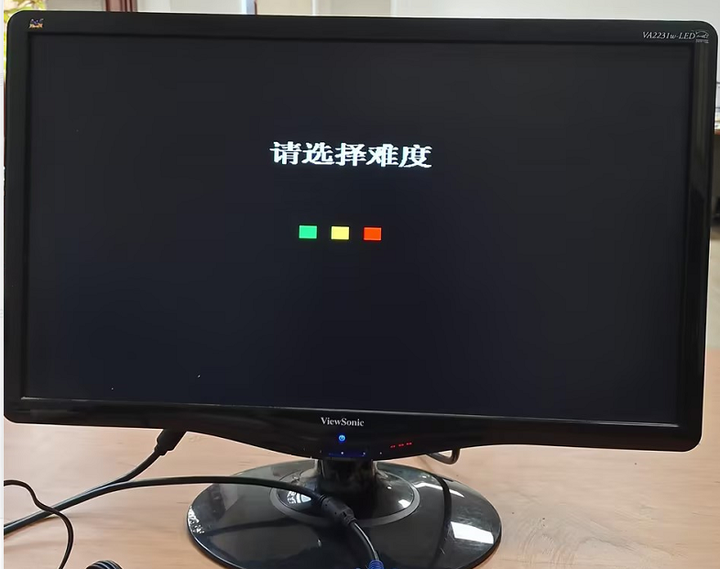

RESTART:系统复位以后进入重启状态,显示器先显示贪吃蛇的欢迎界面“欢迎来到贪吃蛇游戏Gluttonous Snake Game on FPGA”,6秒后显示游戏难度的选择界面,系统等待难度选择信号。

START:游戏有三个难度,使用滑动开关SW[2:0]选择其中一个难度后系统进入开始状态,此时按KEY0-KEY3的任意一个键可触发游戏进入PLAY状态。

PLAY:在该状态下蛇身移动,按上、下、左、右键改变蛇身方向。每吃掉一个食物后蛇身增长一格,蛇身最长16格。每次吃的食物个数会被累计并在数码管上实时显示。

DIE:当蛇撞到四周的墙壁,或者咬到自身或者累计分数达到100分时蛇闪烁3秒,然后VGA显示器显示总分,游戏结束。

原理讲解

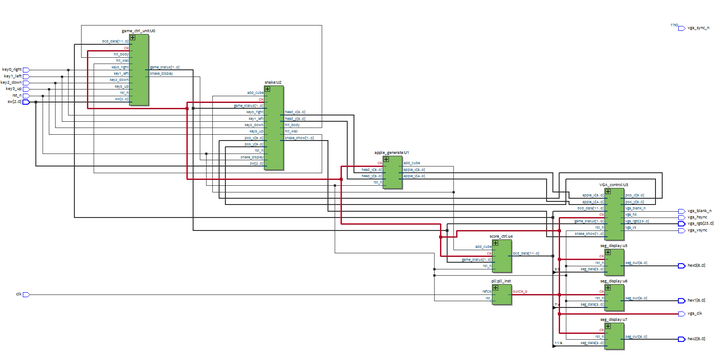

系统模块如下图,下面对每个模块的功能进行简要说明,具体实现方法参考源码中文注释以及后期连载的8篇文章。

snake_top.v: 最顶层模块,例化一个个子模块,并完成子模块之间的连接以及子模块与外部信号的连接。

game_ctrl_unit.v: 游戏状态控制单元,控制游戏状态的转变和不同状态下的输出。

snake.v:控制蛇身运动方向以及蛇身增长。

apple_generate.v:通过加法随机产生食物坐标。

VGA_control.v:控制VGA的显示,包括显示色块,字符和图片。

ROM IP:存储图片内容。

score_ctrl.v:累计游戏得分并将其转换成BCD码。

seg_display.v:控制数码管显示。

PLL IP:将系统时钟50MHz分频出25MHz。系统参考时钟是50MHz, 但是VGA显示选择640*480@60Hz,像素时钟是25MHz,所以其他模块时钟都用25MHz。

从系统RTL Viewer图也可以看到50MHz系统时钟进入PLL被分频为25MHz以后传递给系统其他每个模块:

引脚分配

DE10-Standard开发板引脚分配:

视频演示:

友晶DE10-Standard\DE2-115\DE1-SOC FPGA贪吃蛇VGA显示纯RTL实现

源码下载

DE10-Standard工程下载:

关注“友晶Terasic”公众号可获取源码下载地址。

移植到DE1-SOC、DE2-115时代码无需改变,只需修改引脚分配即可。

贪吃蛇系列连载文章:

1. 基于FPGA的贪吃蛇游戏设计(一)

2. 基于FPGA的贪吃蛇游戏设计(二)——数码管驱动模块

3. 基于FPGA的贪吃蛇游戏设计(三)——计分模块

4. 基于FPGA的贪吃蛇游戏设计(四)——VGA驱动模块色块显示

5. 基于FPGA的贪吃蛇游戏设计(五)——VGA驱动模块字符显示

6. 基于FPGA的贪吃蛇游戏设计(六)——VGA驱动模块图片显示

7. 基于FPGA的贪吃蛇游戏设计(七)——食物(苹果)的产生

8. 基于FPGA的贪吃蛇游戏设计(八)——状态机设计

9. 基于FPGA的贪吃蛇游戏设计(九)——蛇身控制