- 1DeprecationWarning: `np.float` is a deprecated alias for the builtin `float`.解决办法_`np.str` is a deprecated alias for the builtin

- 2异步fifo的设计(FPGA)_异步fifo深度

- 3【数据结构】 二叉搜索树 和 哈希表(Map、Set 集合底层数据结构)_哈希表数据结构 二叉树

- 4SpringBoot基于RabbitMQ实现消息可靠性_消息可靠性 rabbitmq springboot

- 5巴比特 | 元宇宙每日必读:从“被死亡”到净利润增长320%,美图如何靠AI翻身?这份财报里或许有答案...

- 69种单片机常用的软件架构

- 7输入一个字符,找出他的前驱字符和后继字符(C)_c语言前驱字符和后继字符

- 8图书管理系统(javaee)_menu = bookmanager.info

- 9探讨时间复杂度_for(inti=l;i< n;ix = 2) for(intj = 0;j

- 10VSCode 使用 Keil5 插件推荐 附带Keil5安装教程_vscode+keil

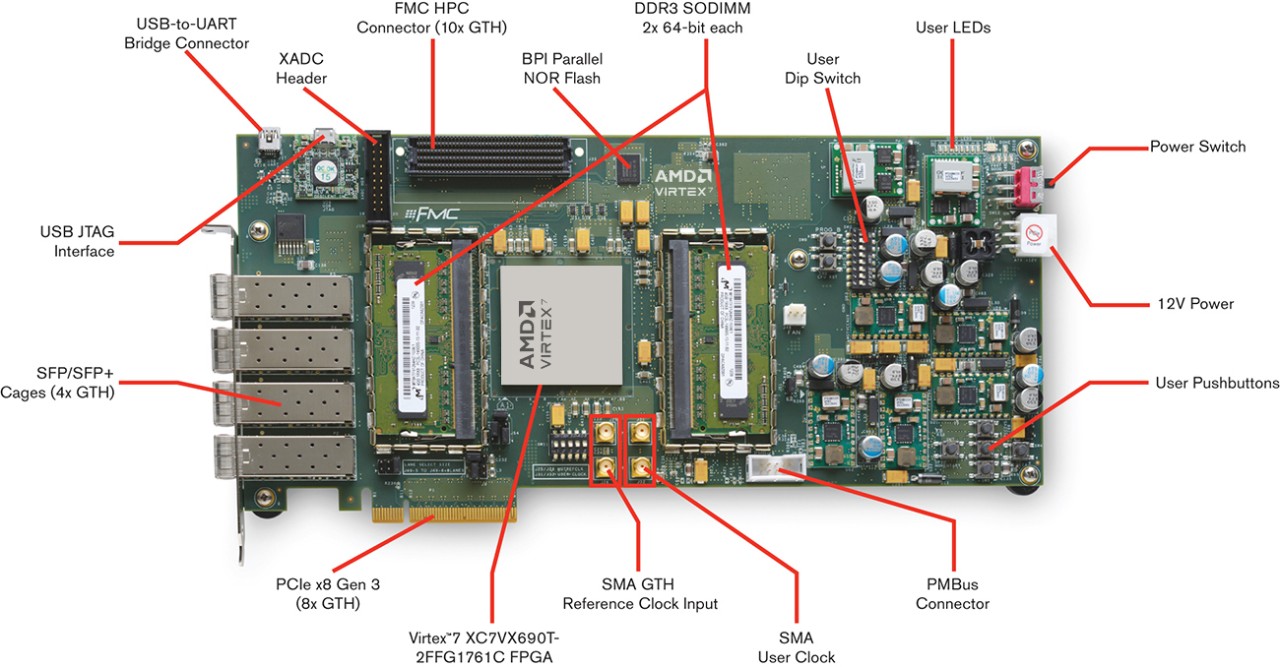

产品推荐 | 基于AMD Virtex 7 FPGA VC709 的高速连接功能开发板

赞

踩

01 产品概述

Virtex™ 7 FPGA VC709 连接功能套件是一款速率为 40Gb/s 的高速平台,您可以通过评估和开发连接功能,迅速为包含所有必要软硬件和 IP 核的高带宽和高性能应用提供强大的支持。它包括一个含有 PCI Express Gen 3、Northwest Logic 公司推出的 DMA IP 核、10GBase-R、AXI 以及与外部 DDR3 存储器相连的虚拟 FIFO 存储器控制器的 40Gb/s 目标参考设计。

为了控制和监控此设计,本套件还包含一个在含有所有软件驱动程序的 Fedora Live OS 基础上构建的连接功能 GUI。此外,套件包含设计启用的 2 个光纤电缆和 4 个收发器组件。

02 性能和优势

-

使用 Virtex 7 VX690T FPGA,实现面向高带宽、高性能应用的 40Gb/s 连接功能平台

-

硬件、设计工具、IP、以及预验证参考设计

-

演示特色 10GBase-R 接口连接至外部 DDR3 存储器

-

高级内存接口,可支持 2 个4GB DDR3 SODIM 内存, 速度可达 933MHz/1866Mbps。

-

实现与 PCIe Gen3x8、4 SFP+、SMA Pair 和 UART 的串行连接功能

-

支持包含 MicroBlaze、soft 32位 RISC 的嵌入式处理

-

开发网络以及其它支持 4 SFP/SFP+ 端口的串行应用

-

扩展 I/O, 包含 FPGA Mezzanine Card (FMC) 接口

03 产品参数

芯片规格

| 逻辑单元 | 693,120 |

| DSP slice | 3,600 |

| 内存 (Kb) | 52,920 |

| GTH 13.1 Gb/s 收发器 | 80 |

| I/O 引脚 | 1,000 |

时钟技术

-

固定的振荡器,带有差分 200MHz 输出

-

用作 FPGA “系统”时钟

-

固定的振荡器,带有差分 233.33MHz 输出

-

用作 “存储器” 时钟

-

用户可编程 (IIC) 差分振荡器 (范围: 10MHz - 810 MHz、156.250 MHz 默认)

-

差分 SMA 时钟输入

-

差分 SMA GTH 参考时钟输入

-

抖动减弱时钟

-

用于支持 CPRI/OBSAI 应用,从一个用户提供的 SFP/SFP+模块执行时钟修复

通信与网络

-

SFP/SFP+ 屏蔽罩 (4 个)

-

GTH 端口至FMC

-

UART 至 USB 的桥接器

-

PCI Express 8-通道边缘连接器

存储器

-

DDR3 SODIMM (2 个) - 各 4GB (最大 933MHz/1866Mbps)

-

BPI 并行 NOR 闪存: 32MB (256Mb)

-

IIC EEPROM: 1KB (8Kb)

配置

-

板上 JTAG 配置电路通过 USB 实现配置

-

BPI 并行 NOR 闪存: 32MB (256Mb)

扩展连接器

-

FMC-HPC (局部分布) 连接器

-

GTH 收发器 (x10) 、 160 个单端或 80 个差分 (34 LA & 46 HA) 用户定义信号

-

VADJ 固定在 1.8 伏

控制 & I/O

-

个用户按钮开关 (x5)

-

用户 DIP 开关 (8-位)

-

用户 LED (x8)

功耗

-

AC 功耗适配器 (12V) 或 ATX

04 接口图

05 物料清单

来源:AMD