热门标签

热门文章

- 1[C++]STL-set/multiset容器_std::multiset自动排序

- 2hadoop大数据开发基础_大数据,Hadoop生态详解

- 3Java:MybatisPlus--配置及其注解_mybatisplus的configuration配置

- 4Flink作业的逻辑与物理拓扑详解

- 5液冷数据中心走红,什么是液冷?_风液比

- 6Android Studio实现内容丰富的安卓手机购物商城APP_android studio购物app

- 7【Linux】信号

- 8redis持久化_redis持久化文件存在哪里

- 9MySQL中执行SQL的BufferPool缓存机制

- 10MyBatisPlus 多数据源配置_mybatisplus多数据源配置

当前位置: article > 正文

树莓派对FPGA板子上的流水灯程序的控制

作者:不正经 | 2024-05-17 14:05:39

赞

踩

树莓派对FPGA板子上的流水灯程序的控制

分别在DE2-115开发板和树莓派上编写串口通信程序, 实现树莓派串口指令对FPGA板子上的流水灯程序的控制,控制方式自定。

一 树莓派使用教程

参考:b站树莓派教程

需要注意的几点:

1、如果遇到ping不通的情况,不要着急,把共享网络关掉,树莓派关机,再重开以及共享网络就可能会ping通,我就是在碰到这的时候没有重开,选择重新安装了几次系统都不行。最后关掉共享网络再重开就又可以了。

2、这个视频教程中,烧系统到SD卡时没有选择用户配置在过去是有默认用户名和密码。但现在已经没有了,需要在烧系统时自己设置好密码和用户,并且要开启ssh,然后后续登录使用你设定的用户和密码。

3、一般进去了会要下东西,因为官方的软件源是比较慢的,肯定需要采用换源策略,修改了文件后,一定要重启重启重启(重启一次就行),我也在这踩了几次坑!!!

4、如果需要使用gpio口,会要你下载wiringPi。可以去github上下载最新的wiringPi的zip包然后移动到vnc里去build。这样会快很多。传送门

以上便是我初步使用树莓派的血的教训。

二 树莓派串口代码

fpgaUart.c

#include <stdio.h> #include <wiringPi.h> #include <wiringSerial.h> int main() { int fd =serialOpen("/dev/ttyAMA0",115200); //打开串口 if(fd == -1){ //如果打开串口失败则退出程序 printf("serialOpen failed!\n"); return 0; } printf("serialOpen success!\n"); while(1){ serialPrintf(fd,"A"); delay(2000); serialPrintf(fd,"B"); delay(2000); } return 0; }

- 1

- 2

- 3

- 4

- 5

- 6

- 7

- 8

- 9

- 10

- 11

- 12

- 13

- 14

- 15

- 16

- 17

- 18

- 19

- 20

- 21

编译命令

gcc -o fpgaUart fpgaUart.c -lwiringPi

三 Verilog代码

串口接收模块:uart_rx.v

module uart_rx ( input clk , input rst_n , input din , //pc端发送给FPGA的数据 output reg [7:0] dout , //发送给tx 让他串行的传出去 output reg dout_vld //当这一次8bit接收完成 再传给tx ); parameter BAUD = 434 ; //使用波特率115200 发送1bit所需要的时钟周期 reg [8:0] cnt_bsp ; wire add_cnt_bsp ; wire end_cnt_bsp ; reg [3:0] cnt_bit ; //计数当前到了哪一bit了 计数9bit 起始位加上数据 wire add_cnt_bit ; wire end_cnt_bit ; reg din_r0 ; //同步到时钟上升沿 reg din_r1 ; //打拍 延时一个时钟周期 wire nedge ; //下降沿 reg flag ; //计数器计数的标志 下降沿到来之后开始计数 传输数据完成了就停止计数 reg [8:0] data ; //寄存数据 always @(posedge clk or negedge rst_n)begin if(!rst_n)begin cnt_bsp <= 9'b0; end else if(add_cnt_bsp)begin if(end_cnt_bsp)begin cnt_bsp <= 9'b0; end else begin cnt_bsp <= cnt_bsp + 1'b1; end end else begin cnt_bsp <= cnt_bsp; end end assign add_cnt_bsp = flag; assign end_cnt_bsp = add_cnt_bsp && cnt_bsp == BAUD - 1; always @(posedge clk or negedge rst_n)begin if(!rst_n)begin cnt_bit <= 4'b0; end else if(add_cnt_bit)begin if(end_cnt_bit)begin cnt_bit <= 4'b0; end else begin cnt_bit <= cnt_bit + 1'b1; end end else begin cnt_bit <= cnt_bit; end end assign add_cnt_bit = end_cnt_bsp; assign end_cnt_bit = add_cnt_bit && cnt_bit == 8; //起始位加上8bit数据位 always @(posedge clk or negedge rst_n)begin if(!rst_n)begin din_r0 <= 1'b1; din_r1 <= 1'b1; end else begin din_r0 <= din; din_r1 <= din_r0; end end assign nedge = ~din_r0 & din_r1; always @(posedge clk or negedge rst_n)begin if(!rst_n)begin flag <= 1'b0; end else if(nedge)begin flag <= 1'b1; end else if(end_cnt_bit)begin flag <= 1'b0; end else begin flag <= flag; end end always @(posedge clk or negedge rst_n)begin if(!rst_n)begin data <= 9'b0; end else if(cnt_bsp == (BAUD >> 1) && flag)begin data[cnt_bit] <= din; //串并转换 LSB end else begin data <= data; end end always @(posedge clk or negedge rst_n)begin if(!rst_n)begin dout <= 8'b0; dout_vld <= 1'b0; end else if(end_cnt_bit)begin dout <= data[8:1]; //第0位是起始位 舍弃掉 dout_vld <= 1'b1; end else begin dout <= dout; dout_vld <= 1'b0; end end endmodule

- 1

- 2

- 3

- 4

- 5

- 6

- 7

- 8

- 9

- 10

- 11

- 12

- 13

- 14

- 15

- 16

- 17

- 18

- 19

- 20

- 21

- 22

- 23

- 24

- 25

- 26

- 27

- 28

- 29

- 30

- 31

- 32

- 33

- 34

- 35

- 36

- 37

- 38

- 39

- 40

- 41

- 42

- 43

- 44

- 45

- 46

- 47

- 48

- 49

- 50

- 51

- 52

- 53

- 54

- 55

- 56

- 57

- 58

- 59

- 60

- 61

- 62

- 63

- 64

- 65

- 66

- 67

- 68

- 69

- 70

- 71

- 72

- 73

- 74

- 75

- 76

- 77

- 78

- 79

- 80

- 81

- 82

- 83

- 84

- 85

- 86

- 87

- 88

- 89

- 90

- 91

- 92

- 93

- 94

- 95

- 96

- 97

- 98

- 99

- 100

- 101

- 102

- 103

- 104

- 105

- 106

- 107

- 108

- 109

- 110

- 111

- 112

- 113

- 114

- 115

- 116

- 117

- 118

- 119

- 120

- 121

流水灯模块:led.v

module led ( input clk, input rst_n, input tx, output reg[7:0] led ); wire [7:0] dout; wire dout_vld; uart_rx uart_rx_inst ( .clk (clk), .rst_n (rst_n), .din (tx), .dout(dout), .dout_vld (dout_vld) ); always @(posedge clk or negedge rst_n) begin if(!rst_n) begin led <= 8'b0; end else begin case (dout) 8'h41 : led <= 8'b0000_0001; 8'h42 : led <= 8'b0000_0010; default: led <= led; endcase end end endmodule

- 1

- 2

- 3

- 4

- 5

- 6

- 7

- 8

- 9

- 10

- 11

- 12

- 13

- 14

- 15

- 16

- 17

- 18

- 19

- 20

- 21

- 22

- 23

- 24

- 25

- 26

- 27

- 28

- 29

- 30

- 31

- 32

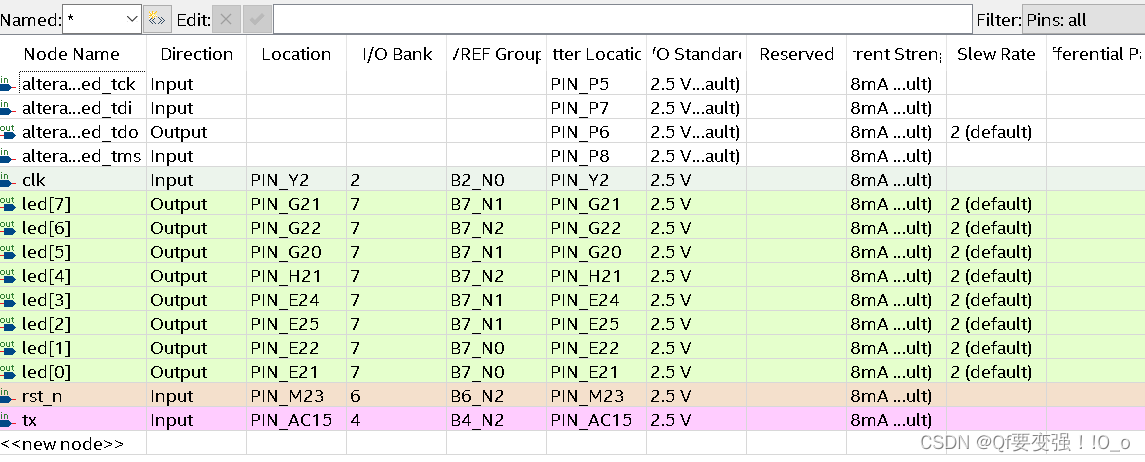

四 quartus引脚绑定

可以选择其它灯,看数据手册

五 运行效果

总结

这次实验初步使用了树莓派,了解了其创始人,是一个很伟大的人…本次串口的实验,效果不是特别好,代码多点几个灯是下载进去了,但是流水灯的效果不明显,感觉是时序上出现了一些问题。那个灯到处乱跳。但是收获挺大的,树莓派确实是个好东西。

声明:本文内容由网友自发贡献,不代表【wpsshop博客】立场,版权归原作者所有,本站不承担相应法律责任。如您发现有侵权的内容,请联系我们。转载请注明出处:https://www.wpsshop.cn/w/不正经/article/detail/583901

推荐阅读

相关标签