- 1大模型“四小龙”激辩AGI的未来:价格战可以打,但不能亏本|2024智源大会精彩回顾...

- 2供应链管理(SCM):如何在颜值和体验上发力

- 3Hadoop伪分布模式安装_安装hadoop集群在data目录的作用

- 4xilinx FPGA multi boot之镜像切换_multiboot

- 5【经典算法】Leetcode.83删除排序链表中的重复元素(Java/C/Python3/Go实现含注释说明,Easy)_删除链表的重复元素

- 6Paper Reading - CNN+CNN: Convolutional Decoders for Image Captioning

- 7Python网络爬虫实现HTTP请求、解析网页和数据存储(简单静态网页爬取)_python爬虫如何解析网页(1)_python解析网页

- 8Python酷库之旅-第三方库openpyxl(02)

- 9swagger工具编写接口文档_swagger 写法

- 10windows下编译tensorflow Faster RCNN的lib/Makefile

Logisim平台上的单周期和多周期MIPSCPU设计(计组课设)_mips单周期cpu设计logisim

赞

踩

目录

实验一、单周期MIPS CPU的设计

1.实验目的

--掌握硬布线控制器设计的基本原理

--在Logisim平台中设计实现MIPS单周期CPU

2.主要任务

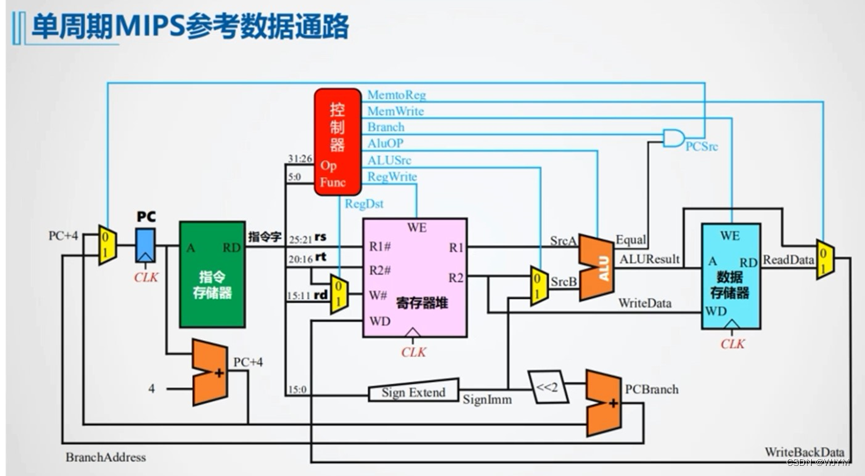

--绘制单周期MIPS CPU数据通路:对应子电路图“单周期MIPS(硬布线)”

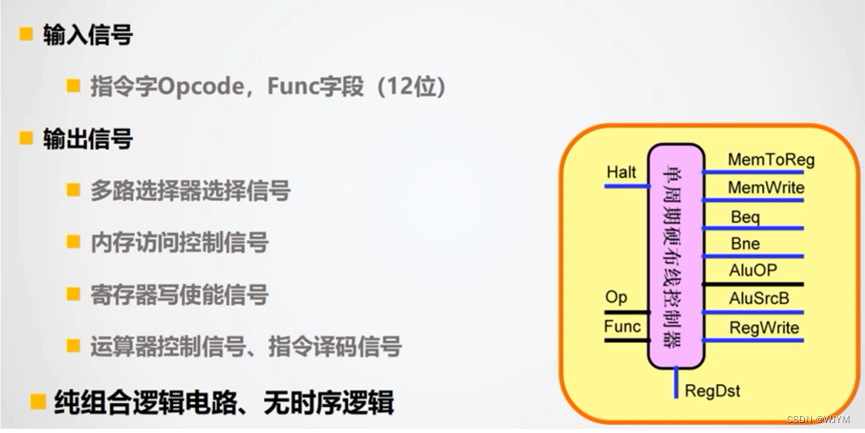

--实现单周期硬布线控制器(纯组合电路):对应子电路图“单周期硬布线控制器”

--测试联调

3.实验过程

步骤二.单周期硬布线控制器的设计

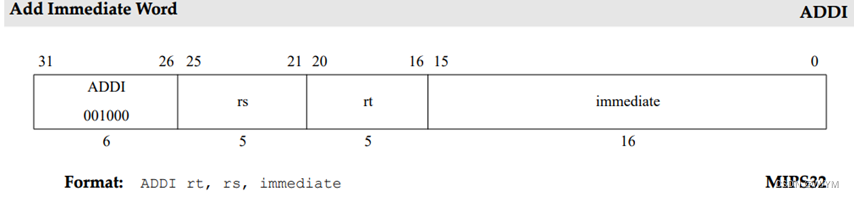

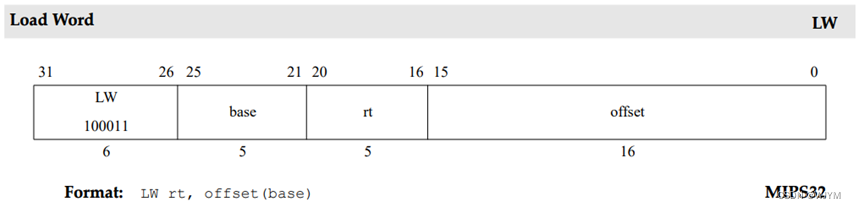

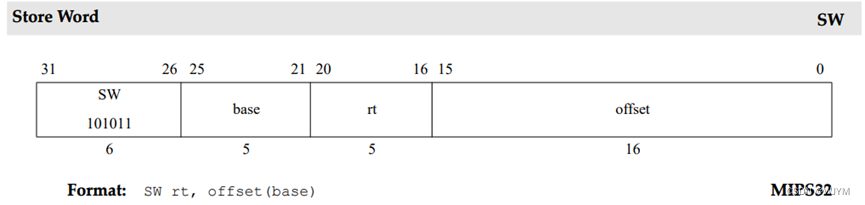

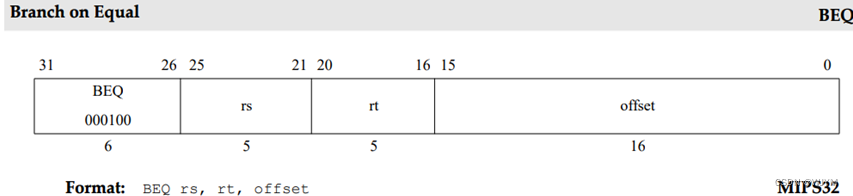

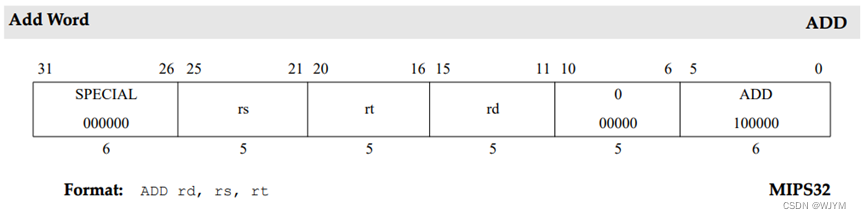

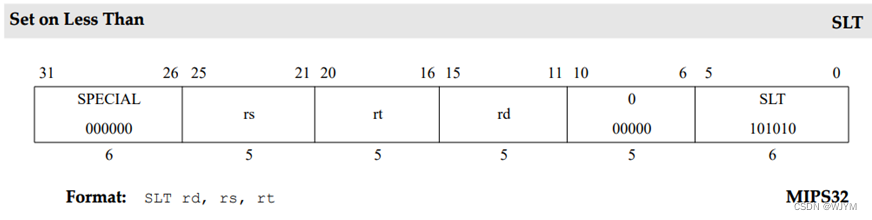

以下是本实验用到的指令译码

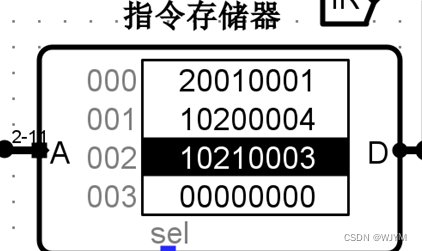

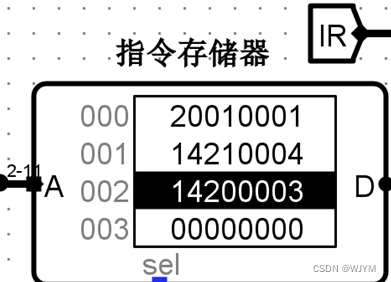

步骤三.CPU测试

利用Logisim中的电路仿真对八条指令进行单独测试以及一个排序算法的测试,可利用时钟单步和时钟连续来进行对指令的执行。

4、电路图及相关说明

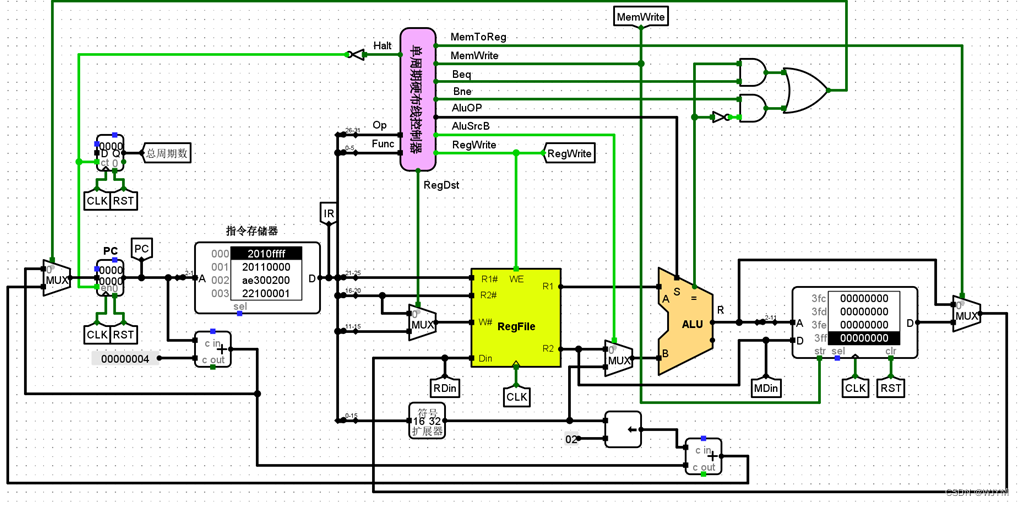

单周期MIPS通路

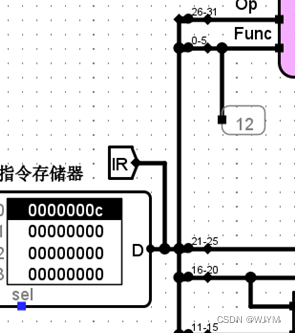

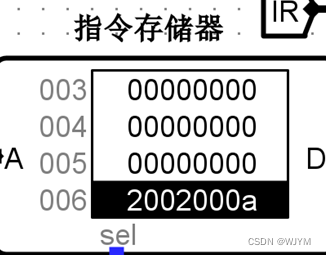

指令存储器: 用于存储在程序计数器 (PC) 指向的地址处的指令代码。CPU从指令存储器中读取基于 PC 的指令,并将其送到下一个级别的组件处理。

程序计数器: 存储当前正在执行的指令的内存地址。CPU通过对 PC 加 4 生成下一条指令的内存地址。

控制单元: 确定当前指令的操作类型,并控制数据通路中其他组件的操作。控制单元根据指令的操作码(pr_opcode)生成操作控制信号,并将其传递给下一个级别的组件。

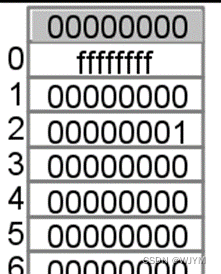

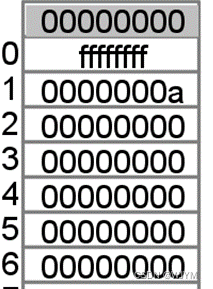

寄存器文件: 由 32 个 32 位通用寄存器组成。对于一个指令的寄存器操作数,寄存器文件可以读取数据或将数据写入寄存器。

ALU (算术逻辑单元, Arithmetic Logic Unit): 执行算术操作、逻辑操作和移位操作。ALU从寄存器中的数据和立即操作数进行计算,并将结果写回寄存器。

数据存储器: 存储程序中的数据。当指令需要从或向存储器中读取或写入数据时,数据存储器接收来自寄存器或立即数的数据,并将其写入或从所需内存地址读取数据。

符号扩展器: 根据指令中的立即数生成 32 位数。当指令操作需要进行有符号扩展操作时,符号扩展器将 16 位数扩展为 32 位数。

Mux (复用器): 令 CPU 能够将不同的输入数据传输到 ALU、寄存器文件、数据存储器和 PC 等组件。这个组件可以为总和设置多个输入,并在根据指令类型或其他因素选择不同的输入。

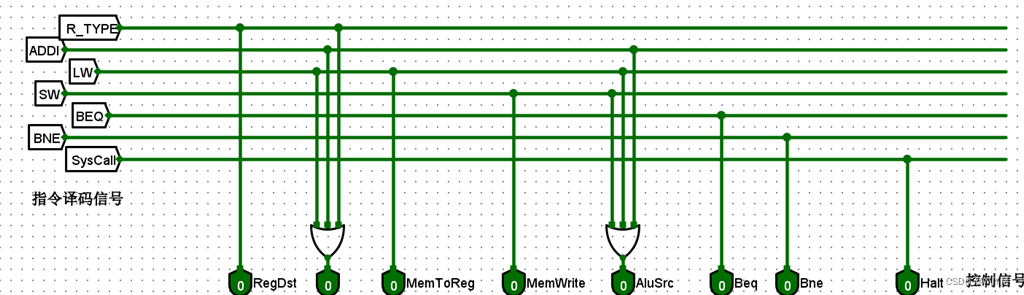

控制信号电路

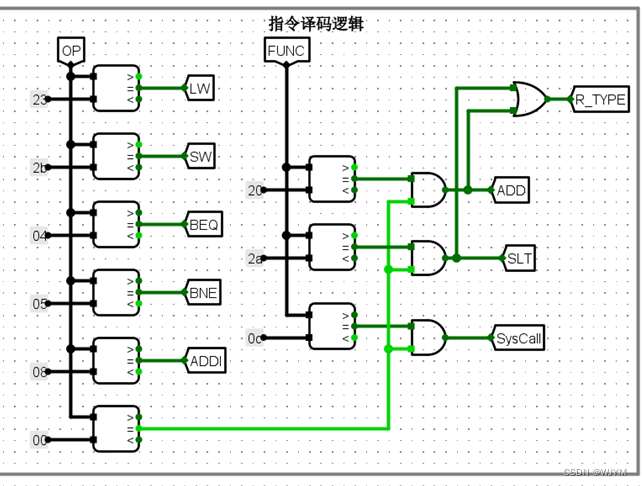

指令译码电路

比较器用于比较指令中的操作码 (opcode) 和功能码 (funct)。比较器将操作码和功能码与预定义的值进行比较,生成相应的比较结果信号。如果操作码或功能码与预定义的值匹配,则输出为 1,否则为 0。

与门用于将多个比较结果信号组合起来形成更复杂的逻辑条件。例如,可以将两个比较结果信号相连,以便仅当两个比较器的结果都为 1 时,与门的输出才为 1。

或门用于将多个逻辑条件合并为一个条件。例如,可以将两个与门的输出信号相连,以便仅当这两个信号中至少有一个为 1 时,或门的输出才为 1。

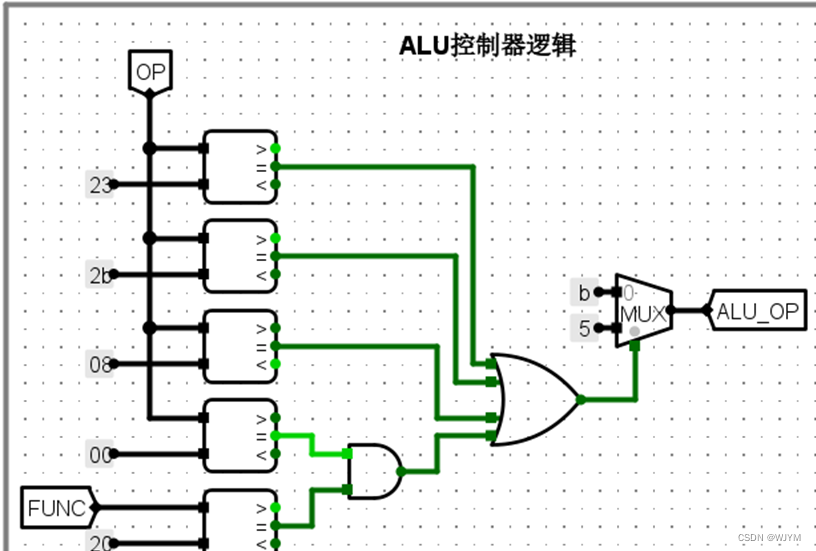

控制器电路

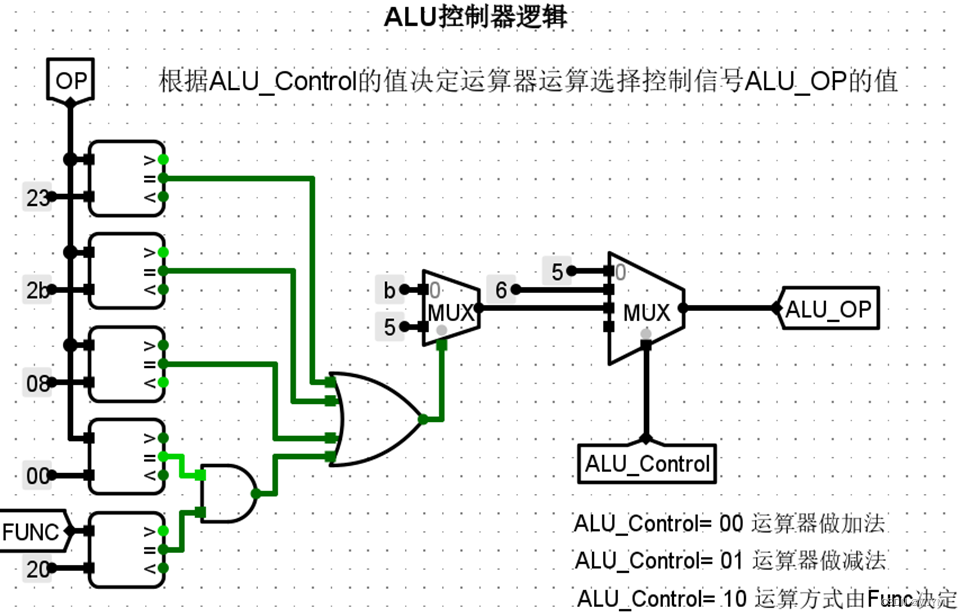

比较器用于比较指令中的算术操作码,生成相应的比较结果信号。例如,从指令中提取的操作码可能对应于加法操作、减法操作、逻辑与操作等。

或门用于将多个比较结果信号组合成更复杂的逻辑条件。例如,可以将两个比较结果信号相连,以便仅当这两个比较器的结果中至少有一个为1时,或门的输出才为1。

多路选择器接收来自比较器、或门等的信号,并决定 ALU 应该执行哪种操作。例如,当 ALUOp 为 00 时,多路选择器将选择 ADD 操作;当 ALUOp 为 01 时,多路选择器将选择 SUB 操作。

通过或门,将一些单独的控制信号合并成传向 ALU 的控制信号。例如,RegDst 控制信号用于选择 ALU 结果存储的寄存器,而 RegWrite 控制信号用于指示 ALU 是否将其执行结果写入寄存器。

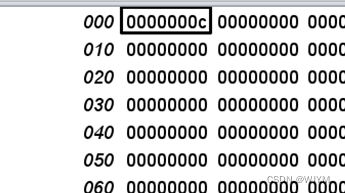

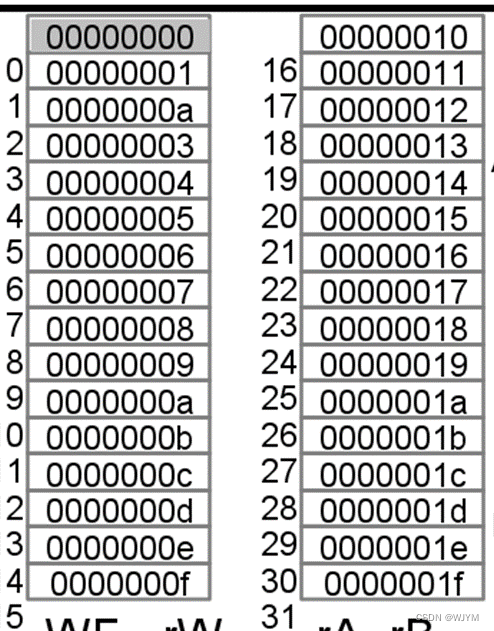

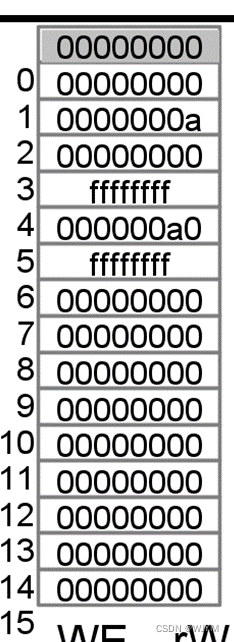

5、实验数据测试与截图

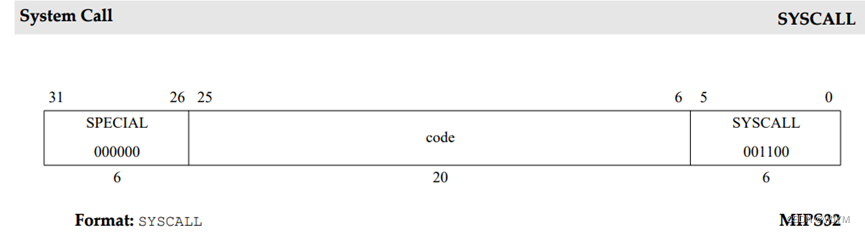

#测试syscall功能,$v0=10,停机,$V0=34,显示¥a0的值

对应的指令字为:0000000c

Func的值为001100(12)

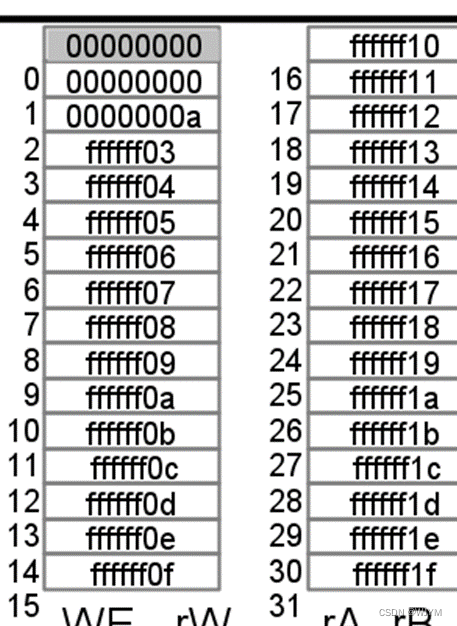

#测试addi指令,分别将3~31号寄存器修改为0xffffff03,0xffffff04 ...0xffffff1f

#测试add指令,分别将3~31号寄存器修改为0x03,0x04 ...0x1f

#测试beq指令,第一次beq应该不跳,第二个应该跳转

#测试bne指令,第一次bne应该不跳,第二个应该跳转

#测试slt指令,第2条指令应该将$3置位为1,第3条指令将$3复位为零

#测试sw指令,写入3个数据,base=128,offset=-32,0.32, 写入数据位e0,-1,-32

#测试lw指令,写入1个数据,读出一个数据,6号寄存器应该为-1

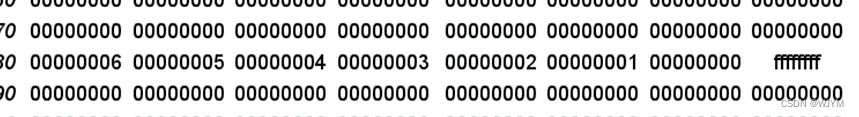

#本程序实现(字节地址0x200,字地址0x80)开始的8个字单元的降序排序

实验二、多周期MIPS CPU的设计

1.实验目的

-熟悉多周期MIPS CPU设计原理

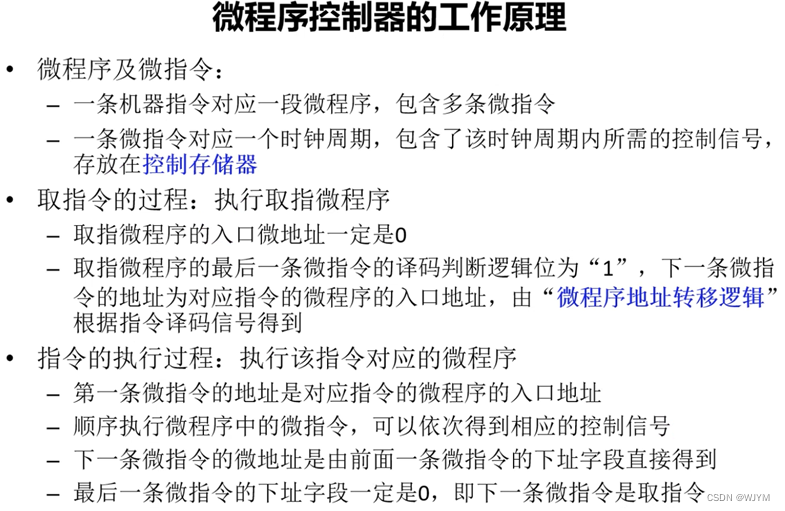

-掌握微程序控制器的基本原理

-利用微程序控制器的设计实现多周期MIPS处理器

2.主要任务

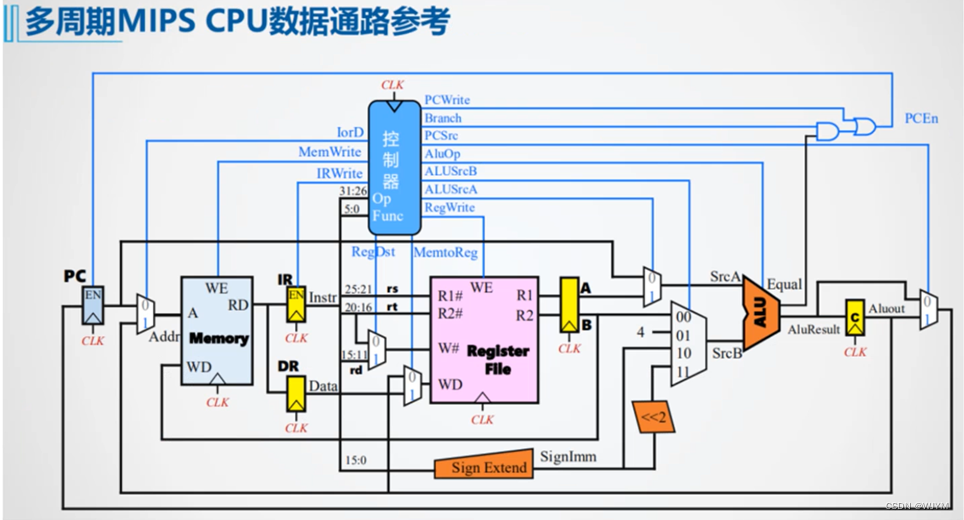

绘制多周期MIPS CPU数据通路

实现微程序控制器

测试联调

3、实验过程

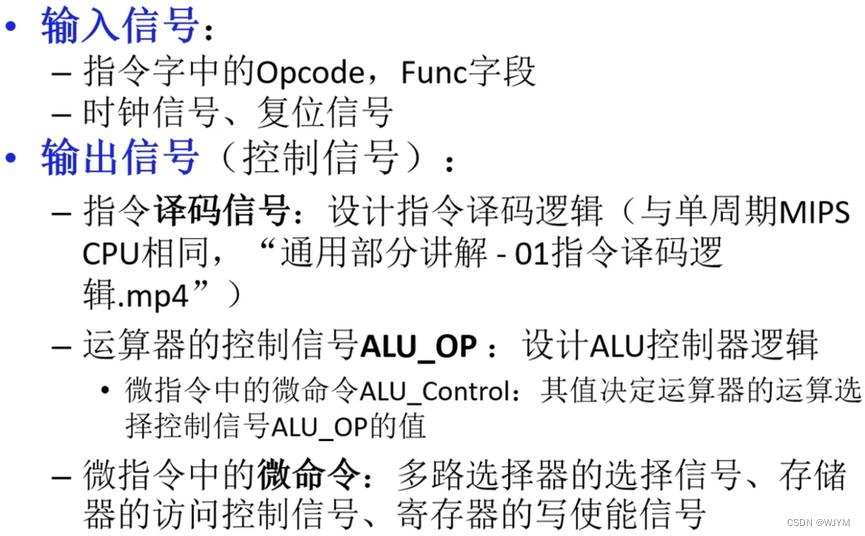

步骤一.构建MIPS主机通路

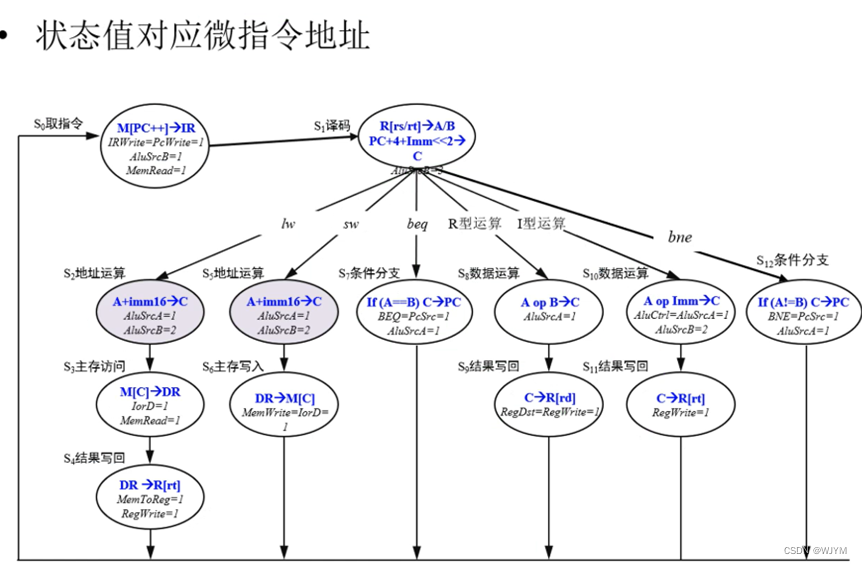

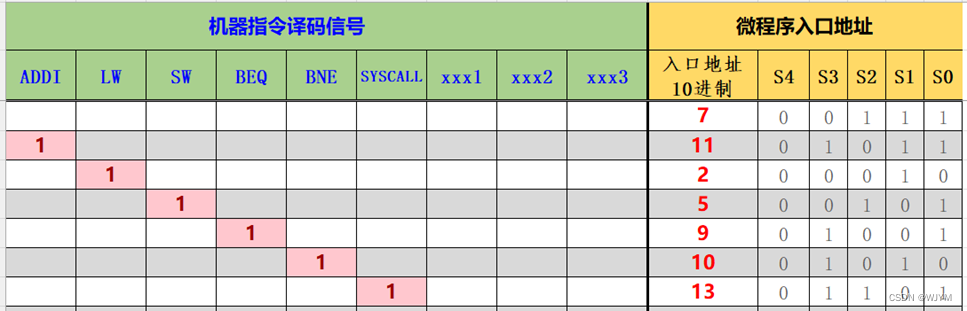

步骤二.实现微程序地址转移逻辑

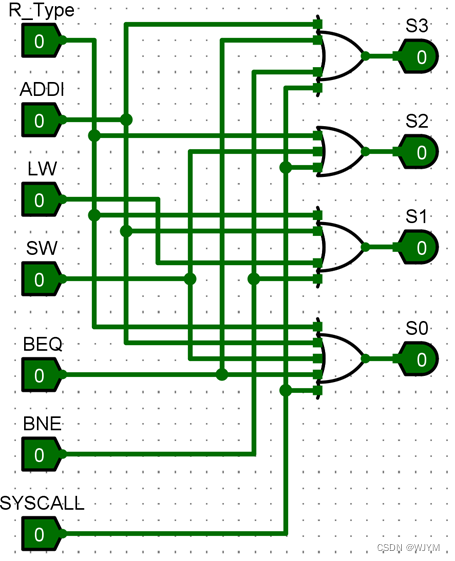

其实现的功能为根据指令译码的结果,得到其微程序的入口地址

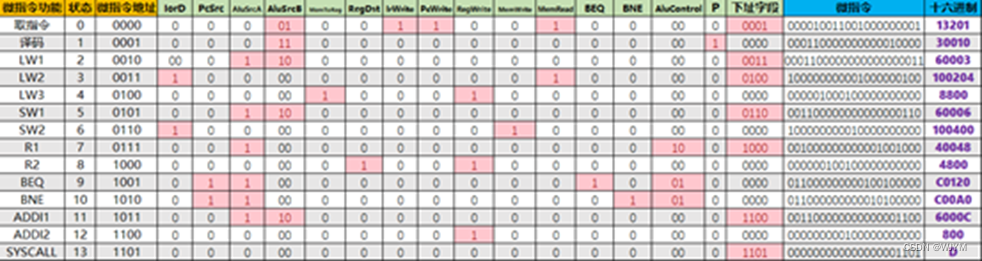

由指令状态变换图可得

R_Type的微程序入口地址为7;ADDI的微程序入口地址为11

LW的微程序入口地址为2;SW的微程序入口地址为5

BEQ的微程序入口地址为7;BNE的微程序入口地址为10

SYSCALL的微程序入口地址为13

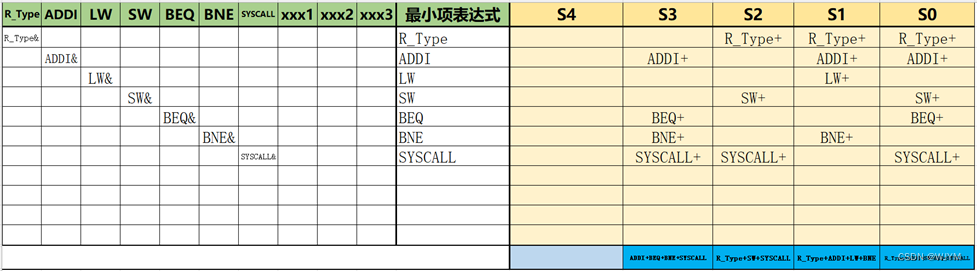

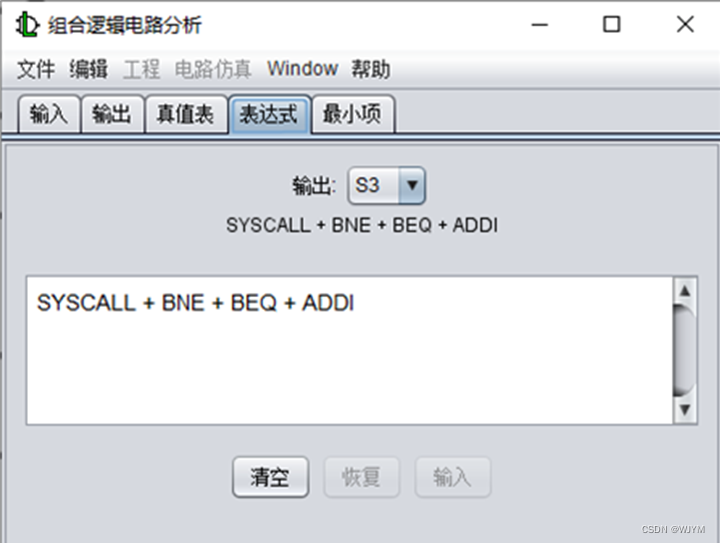

利用微程序地址转移逻辑自动生成自动生成逻辑表达式

将表达式输入至组合逻辑电路分析表达式中,即可自动生成微程序地址转移逻辑。

步骤三.设计微程序控制器

根据状态图构建微程序,得到总的微指令

步骤四. CPU测试

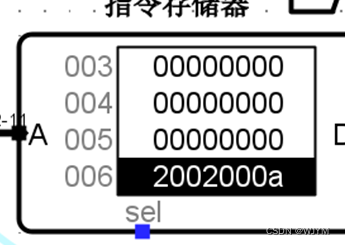

利用Logisim中的电路仿真对一个排序算法进行测试

4.电路图及相关说明

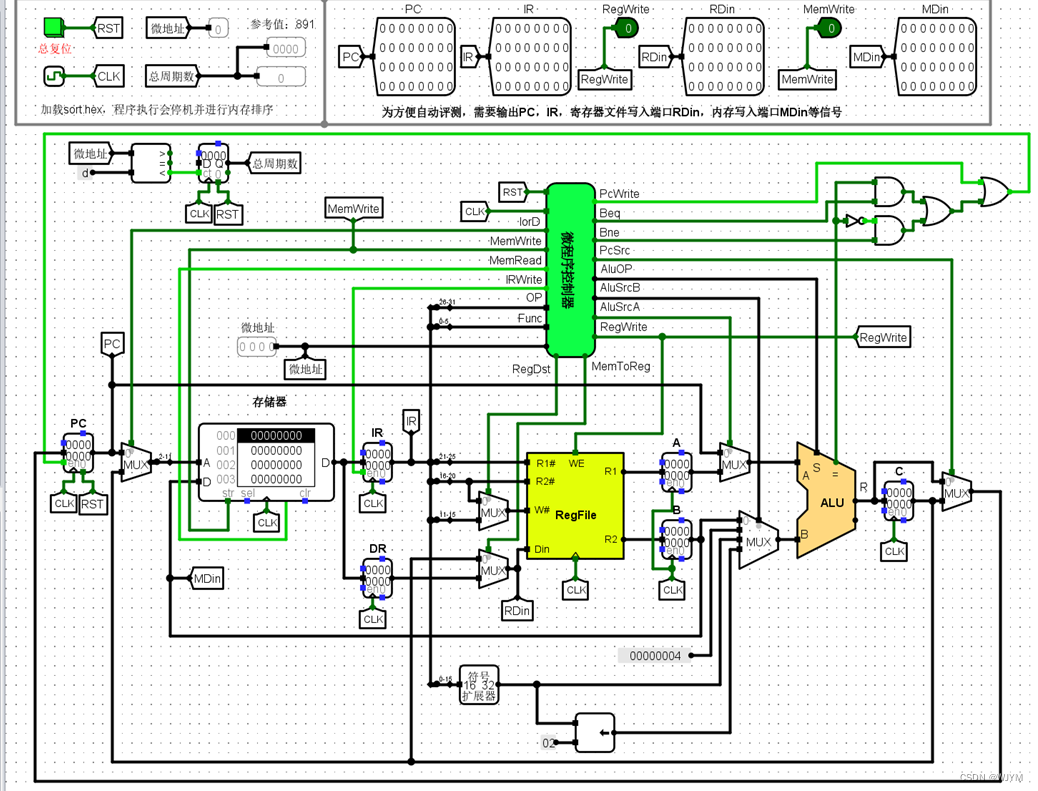

多周期MIPS通路

微程序地址转移逻辑电路

ALU控制器

当AluOP=5时,ALU执行加法;当AluOP=6,ALU执行减法;当AluOP=(0B)H时执行有符号数比较。

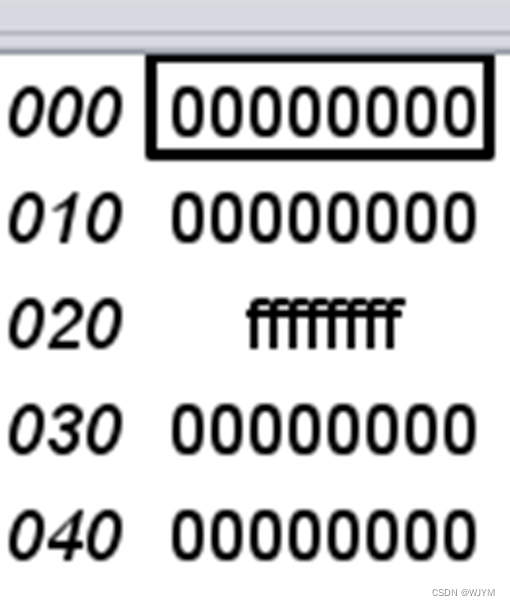

5.实验数据测试与截图

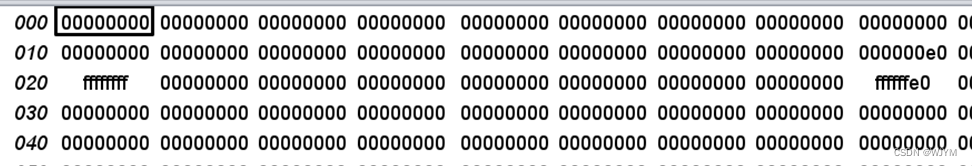

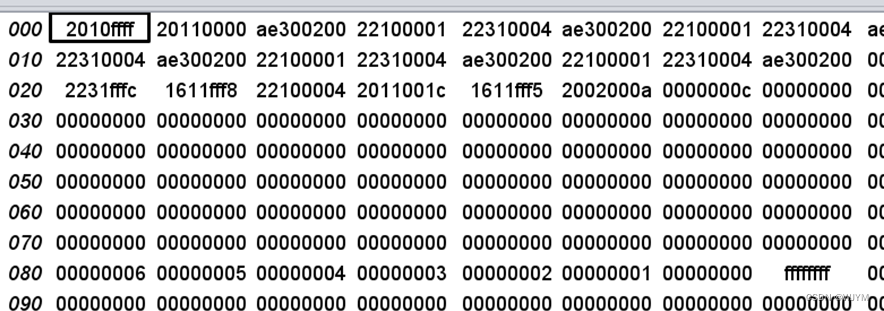

在存储器中载入排序程序与sort.hex。

多周期的指令和数据存放在同一寄存器中

载入的程序与单周期MIPS控制器相同,说明它们的功能相同,只是实现的方式不同

程序停机后查看数据存储器中的排序情况有符号降序排列

实验心得

在单周期MIPS CPU设计实验中,我学到了单周期CPU的基本结构和实现方法。它的主要特点是能够同时执行一条指令,因此每个指令在执行前要完成多个步骤,例如取指、译码、执行、写回等。这些步骤会组成一个时钟周期。在实现时,我首先学习了指令格式,然后设计了控制器来实现不同指令的不同操作,同时利用组合逻辑和时序逻辑来完成指令的各个步骤。最后,我测试了CPU的正确性,并通过运行一些程序验证了它的性能。

在多周期MIPS CPU设计实验中,我学到了多周期CPU的优点和实现方法。它的主要特点是利用多个时钟周期执行一条指令,因此每个指令分成了多个阶段,例如取指、译码、执行、访存、写回等。这些阶段可以分成不同的时钟周期来完成。在设计时,我首先学习了指令格式和流水线结构,然后分阶段实现了控制单元、数据通路和存储器等部件。最后,我测试了CPU的正确性,并通过运行一些程序验证了它的性能和运行效率。

总的来说,单周期MIPS CPU和多周期MIPS CPU的设计实验让我对CPU的内部结构和运行原理有了更深入的了解。通过实践,我发现单周期CPU相对来说更简单、易于实现,但性能较低;而多周期CPU虽然更复杂,但能够有效提高运行效率,适用于更高性能的系统中。两种实验都让我对硬件电路的设计有了更深刻的认识,也让我对计算机系统结构方面有了更全面的了解。