- 1联邦学习后门攻击总结(2019-2022)_联邦学习无目标攻击

- 2ChatGPT Plus价格太贵,可以约上三五知己一起上车体验一下,这个项目就能帮到你_chatgpt-web-plus

- 3校园网络的组建与设计——计算机网络大作业【计算机高级应用】

- 4Win10 下 RabbitMQ 的 安装 配置

- 5Android 之 Bluetooth 框架_android 蓝牙通话架构图

- 6海康WEB3.3控件开发包 V3.3 前端vue项目调用实时监控画面

- 7绝望!导师只给我一周时间.......

- 8使用Jena-TDB存储RDF本体、知识图谱文件_怎样存rdf格式 java

- 9filebeat 配置

- 10STM32CubeMX + freeRTOS线程操作(二)_oskernelsystick

Allegro 16.6使用说明及技巧_allegro使用教程

赞

踩

1.导入导出系统设计参数

- 导出:File→Expeort→parameters;全选(基本设置、光绘设置、色彩设置、文本尺寸、命令参数)→Export,选择合适的目录保存为.prm文件;

- 导入方法1:File→Import→parameters,加载之前保存的.prm文件,点击import;

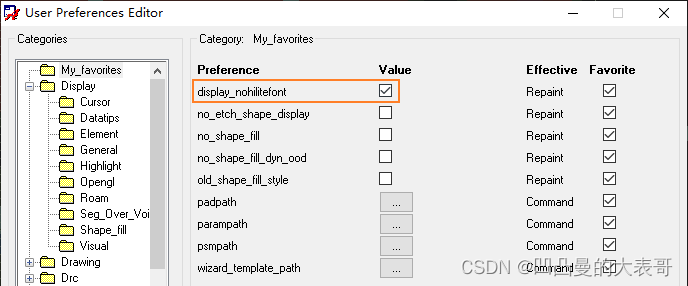

- 导入方法2:执行 setup—user preferences 菜单操作,打开 user preferences editor 设置框,

找到 path—library 选择 parampath,在路径里面加载你放置 parameters 文件的文

件夹名字;注意路径一定要正确!

执行 file—import—parameters 菜单命令打开 import parameters file 设置对话框,单击 library,打开对话框直接选择你要导入的.prm 文件,点击import:

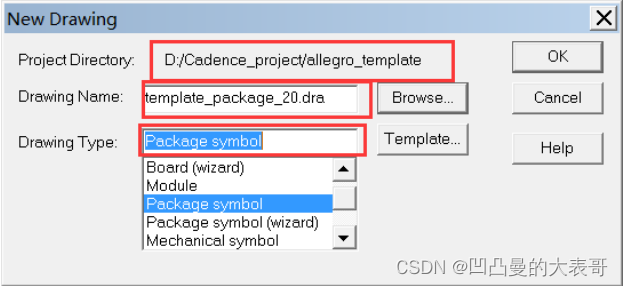

2.建立模板文件

- File—new;选择类型,选择路径(这个一定要记住,在设置路径的时候是

需要调用的),命名(这里命名的时候根据自己需要区分标示)

- 设置好 格点、尺寸、字体、规则、 颜色等参数后保存文件;

- 设置模块路径:执行“setup—user reference”菜单命令。打开环境变量设置标签页。选择 paths—config,选择 next 找到 wizard_template_path,设置路径。

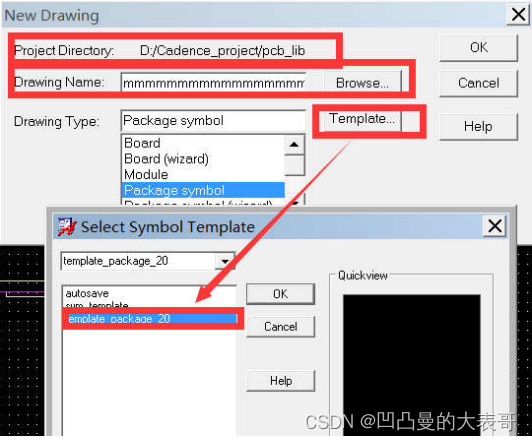

- 调用模板文件: File—new,这里的话,和制作封装的时候路径,封装类型,命名都是一样的,只是我们要选择 template 选择一下我们已经设置好的模板,点OK;

3.快捷键

- Tools→Utilities→Aliases/Funckeys可以查看所有快捷键;

- F1:显示整个PCB、F4:show element、F9:Cancel、F10:grid显示/隐藏、F11:Zoom In、F12:Zoom Out、+/-:换层、Shift+F4:Show Measure、Shift+F7:取消所有高亮、Ctrl+D:Delete、ix ±100:相对左/右移动100;iy ±100:相对上/下移动100;

- 自定义快捷键方法:打开D:\Cadence\Cadence_SPB_16.6-2015\share\pcb\text\env文件:

末尾添加:funckey ' ' iangle 90 空格键翻转90°;

funckey ~R iangle 45 Ctrl+R翻转45°;

4.Tab键,在重叠的数个对象之间逐个切换;

- 设置封装高度:Setup--Areas--Package Height,勾选shape后点击place_bound_top区域,输入高度;

5.多层板设置:Setup--Cross Section,内层勾选Negative Artwork,内层即为负片;

6.除了Z-copy,还可以使用Setup--Areas直接绘制相应层:

7.导入dxf:File--import--DXF,载入DXF文件,点击Edit/View Layers,勾选Select all,在Class、Subclass选项选择一个层,如Board Geometry outline,点击Map---OK:

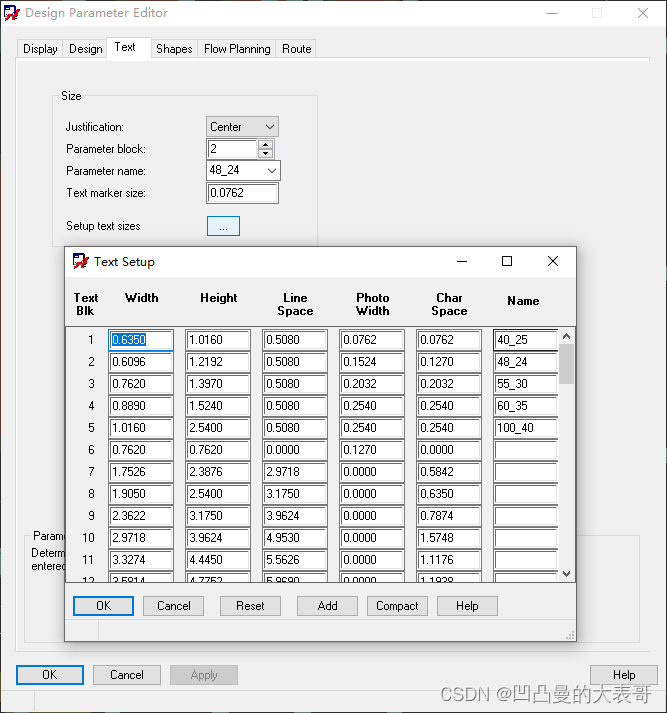

8.Text字体参数说明:Line space--字符行间距、photo width--字符丝印线宽、char space--字符字体间间距:

9. 显示设置:Display

10.布局模块复用:

- 选择 placement edit 模式、创建模块和复用模块中的元件不要出现 FIX 属性;

- 首先完成标准电路模块布局,框选后右击place replicate create:

- 在 FIND 里面设置我们要建立模块所包含的元素后点击确定:

- 提示选择设置模块的原点坐标,这里点击的是左下角(如果需要精确的就需要

先 show element):

- 弹出一个对话框,默认路径在工程目录下,命名模块,并保存,模块生成.mdd文件;

- 调用模块,把类似的元器件放在一个地方,框选后右键—Place replicate apply—Browse选择创建的.mdd模块名,打开 place replicate unmatched component interface 对话框:

- 两个模块的元件全部对应(如上图除了 R170 和 R178),那么我们直接单击OK(这里不再提示),有的时候就会存在上面的情况(R170 和 R178),个别元件不能对应,这样的话就需要我们自己手动对应(也可以多框选一些器件);过程如下:

第一步:取消勾选 Match 下面的选项;

第二步:左侧栏逐个选择未匹配的元件(R170 和 R178),在右侧选择对应的器件进行匹配;

第三步:匹配好所有的之后,如下图,单击 OK,被复用的电路模块附庸在鼠标上,选择一个坐标位置放置即可 ;

11.约束管理器

- Neck:走线变细。F3快捷线走线,右击Neck Mode线即变细,注意Max Leagth必须设置;

- Differential Pair:Primary Gap差分对间距;

- Region选项为区域内单独设置的规则;

12.尺寸标注显示单位:option Text上加入:%v%u(小写);

13.Gloss设置

- 不想为gloss的net增加No_gloss或FIXED属性,选中net,右击Edit property,左边勾选No_Gloss,右边apply即可;

- 某个区域不想被优化,增加Maunfactuing--No_gloss_all区域层即可;

14.铺铜设置

- 实心铜变网格铜:铜皮选中,右键Parameters,Fill style设置xHatch;

- 禁止铺铜区:Setup--Areas--shape keepout;

- 十字焊盘十字宽度设置:Shape--Global Dynamic Shape Parameters--use fixed themal width of(如10mil改为12mil);

- 十字焊盘内部与铜皮间距设置:约束管理器--Same net Space--NET--pins--GND--SMD_pin to shape参数(如10mil改为20mil);

15.Gerber输出

- 钻孔新增符号:Maunfacture--NC--Drill Customization--Auto generate symbols;

- Maunfacture--NC--Drill Customization--Library drill report可以浏览所有pad参数;

- PCB外围如果没有photoplot_outline层,或者该层没有把钻孔表包围,则导出会有问题;

- 导出坐标文件:File--export--placement:

- 指定输出Gerber路径:Setup--use preference--File_management--output_dir,ads_sdart填写Gerber,则在PCB目录下出光绘文件时自动生成Gerber文件夹:

16.Shape变Line:Shape--Decompose,框选中shape,右键done;

17.Line变Shape:Shape--compose,框选中Line,右键done;

18.Ref Des丢失,直接在改层增加Text,先选中元件,再点一下空地,输入位号;

19.Board Geomery/Ref_Cross_Top层显示位号与元件连接关系,注意EDA SKILL对齐有影响;

20.EDA365 skill加载.il插件步骤:

- 第一步将.il文件放到D:/candence/eda355 skill/plugins目录下;

- 第二步改文件名:序号.菜单名=调用命令(原文件名不能改)=密码(无密码则为No)=提供者.il;

20.allegro中先点击Move,切换到orcad,框选中部分器件,返回allegro则被选器件吸附在鼠标上可一起move:

21.Line倒角

- Maunfacture--Drafting--chamfer导直角;

- Maunfacture--Drafting--Fillet导圆弧;

22.焊点统计

- 打开Tools--quick report--Summary Drawing Report;

- 注意,总pin数包含了元件封装本身的非金属孔,即Non-Plated;

- 插件pin数目:电气Plated孔—VIA:Thru孔—PCB中实际非pin脚的电气Plated孔如螺丝孔;

- SMD数目:总pin数—(总打孔—VIA:Thru孔);

23.xnet跨器件net合并设置使用

- 需要做等长线时如果线段跨接了电阻或电容将线分成了两段,就需要设置xnet将两段线合并起来做等长;

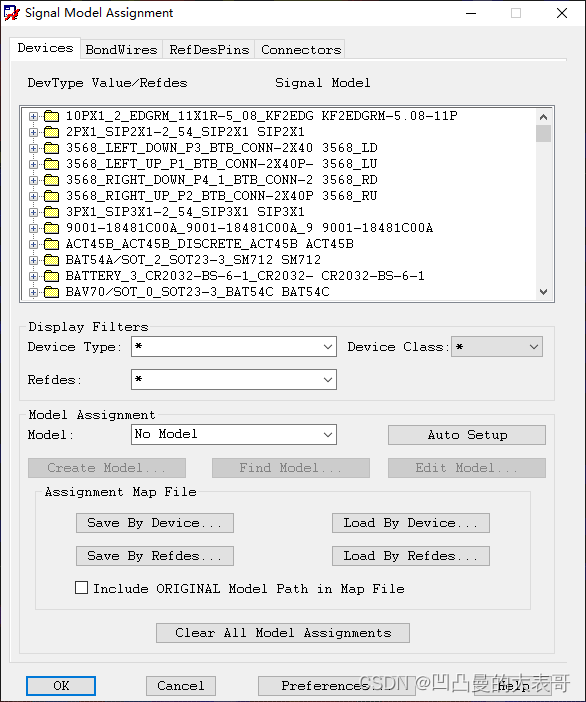

- 首先点击Analyze--Model Assigment,直接点OK,是,弹出下图:

- 点一下跨接连接线的电阻电容,在选项中选中对应的器件位号,也可以对照原理图一个个分别选中操作;点击Create Model、一路OK,对应的元件后面就加上了xnet属性;(如果要取消,Model选项框里下拉选择“No Model”);

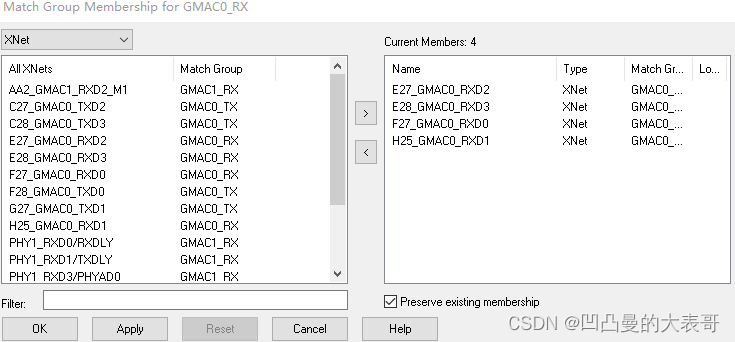

- 此时进入规则管理器,electrical---Net---Relative Propagation Delay,找到要配置等长的Match Group,右击选择Match Group members,弹出的对话框,坐标选择xnet,即可显示出以及配置好的网络:

- 将xnet添加到Group里,此时在Match Group名称上右击点Select,发现包含跨接电阻的整个cline都被高亮了,此时做等长绕线的时候就将整条cline包含进去,如果不是xnet,每次绕等长就只能以电阻为界限两边各自绕;

24.Region特殊规则区域使用

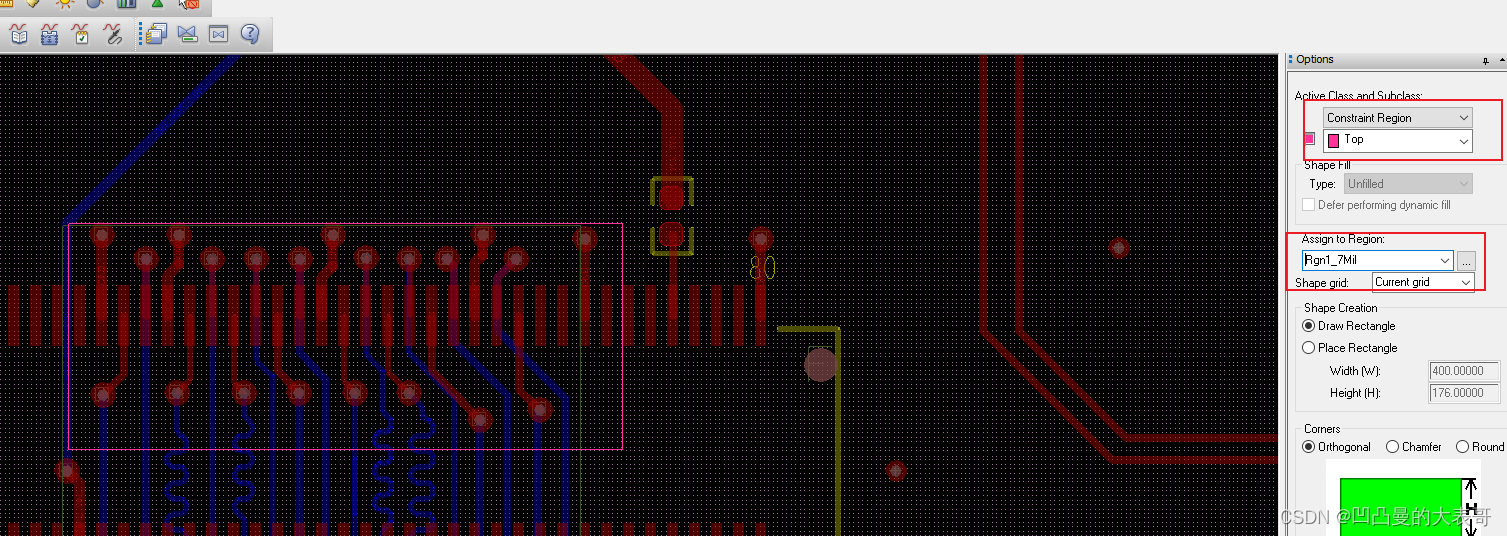

- 布线的时候原本线距12mil走得好好的,接入连接器或者芯片pin脚的时候间距只能走7mil,满屏的DRC,此时就需要在连接器或芯片周边放一个Region属性的shape,表示此处的space规则比较特殊;

- 第一步建立Region规则,依然是打开约束管理器,Spacing---Region---ALL layers,右边objects name下右键Creat ---Region,取名后OK,并填写相应的规则值:

- 使用方法:随意选择shape按钮,右上角层类选择Constraint Region,下面根据需求选择TOP\BOTTOM,主要要选上Region名称,然后要需要放置Region特殊规则的位置画框即可,此时框内的Space规则是Region指定的,框外的space规则是Spacing内的object指定的:

25.金属螺丝孔与GND铜皮额外间距设置

通常金属孔与GND铜皮间距在设计规则中以及设置好,与其他元器件规则相同,比如20mil,但是若想将二者间距扩大至100mil又不影响其其他规则,就需要单独设置螺丝孔的属性实现:

选择pin,选中螺丝孔,右击edit property---Dyn_clearance_Oversize_array---assign----Adn_ALL输入80,点击两次OK即可。