- 1java基于springboot+vue高校招生宣传网站管理系统maven源码_高校招生宣传管理系统

- 2WARN util.NativeCodeLoader: Unable to load native-hadoop library for your platform...的解决方案_warn [main] util.nativecodeloader: unable to load

- 3实战:QT车牌识别系统综合设计_实验三十七 综合实战:车牌识别

- 4【无人机编队】基于二阶一致性实现无领导多无人机协同编队控制附matlab仿真_无人机集群协同matlab仿真

- 5中文大模型评估基准:C-EVAL: A Multi-Level Multi-Discipline Chinese Evaluation Suite for Foundation Models

- 6Java本地缓存框架系列-Caffeine-1. 简介与使用_caffeine.newbuilder()

- 750强人工智能面试问题与解答

- 8华为OD机试Js - 提取字符串中的最长合法简单数学表达式_华为机试js提取字符串中的最长合法简单数学表达式

- 92021年Github项目Top100_tinymce springboot github

- 10【卷积神经网络】1*1卷积的作用、深度可分离卷积原理及实现_conv2d 1*1卷积

LVDS接口设计及应用(1)——以AD9253为例

赞

踩

因为是从项目出发,所以这里我就拿市面上应用比较广泛的AD9253为例,来重新回顾一下我的设计过程。

1、芯片简介

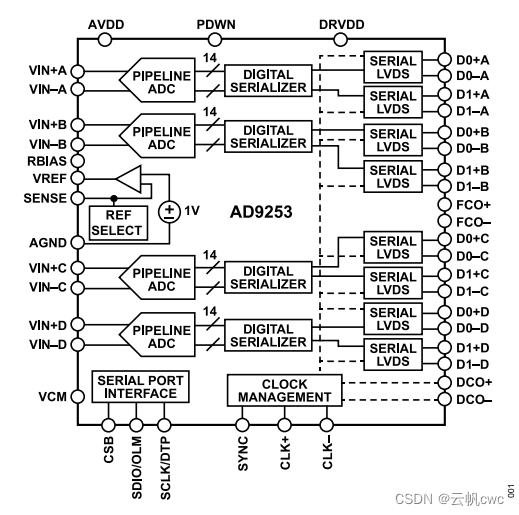

在应用前先简要了解一下这颗芯片,其功能框图如下所示:

由框图可以看出,AD9253是一颗14位分辨率,最高可达125M采样率的四通道高速ADC,工作电压为1.8V,分为模拟供电AVDD和数字供电DRVDD。高速ADC常用于通信系统当中,一般比较关注交流性能,AD9253信噪比为75.3dBFs,无杂波动态范围为98dBc,是极其优秀的水平,当然实际应用中选型还要关注功耗成本等,与实际项目综合考虑。

其硬件应用电路主要由以下几个部分组成:

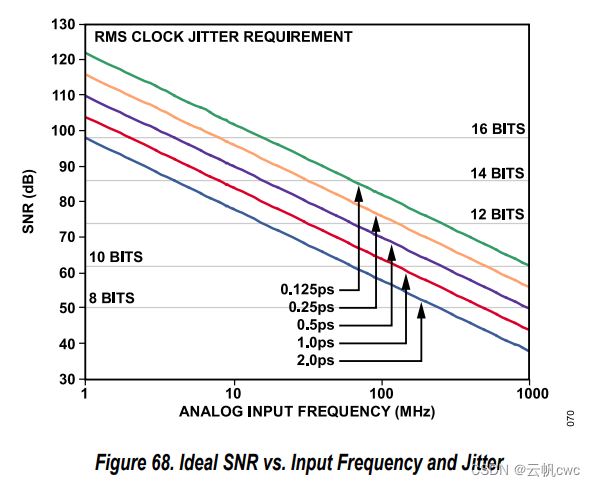

1)供电,要注意电源噪声要尽可能小,否则会影响ADC性能,2)前端差分输入,前端单端转差分可以通过全差分运放、变压器和巴伦实现,为了实现最佳性能,一般使用双巴伦电路尽可能减小相位不平衡,3)差分时钟输入,时钟的关键指标在Jitter,时钟Jitter会显著影响信噪比,如下图所示:

4)数据输出接口,这颗ADC的数据输出用的就是LVDS接口,该接口具体时序下一节再细说,5)控制接口,主要是控制ADC内部寄存器的读写,对ADC进行配置,AD9635采用的是三线制SPI通信,分别为CS片选,SCLK时钟,SDIO数据输入输出,SPI通信可以在FPGA中实现SPI模块,这个有很多参考代码,我的项目中应用的是MicroBlaze进行控制,这用起来比较方便清晰。

针对硬件电路的设计主要还是多实验多总结,常常是一个电容改变了几pF,性能就改变了几个dB。

2、如何通过7系列FPGA实现LVDS高速ADC接口

2.1、应用LVDS串行接口的原因

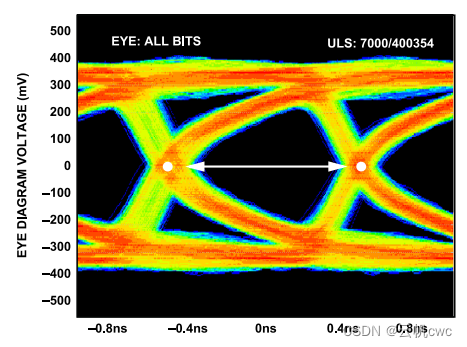

LVDS串行接口中有三个关键词,低压,差分和串行。首先是为什么选择串行,其实在ADI官网也可以找到一些LVDS并行接口的ADC,但当采样率进一步提高,LineRate进一步提高,全部选用的都是串行数据输出,串行通信在物理上减少了走线,同时相比于并行传输在时序上更宽裕,只需要差分对内的等长,时钟和数据之间的等长要求不高,这个在写FPGA驱动时就有体现。然后是低压,电压摆幅更低时,信号的上升时间更小,高速传输时在板材等条件一致时,即通道带宽一致时,能传输的信号频率更高,信号带宽在经验上一般是0.35/上升时间。对于低压,有两个标准,即LVDS-ANSI标准,信号压差为700mv,和LVDS-IEEE标准,信号压差为400mv。最后差分的应用是用于抑制共模干扰,差分走线在高速应用中基本已经是必须的了。下图是AD9253 LVDS输出眼图示例。

2.2、LVDS时序说明

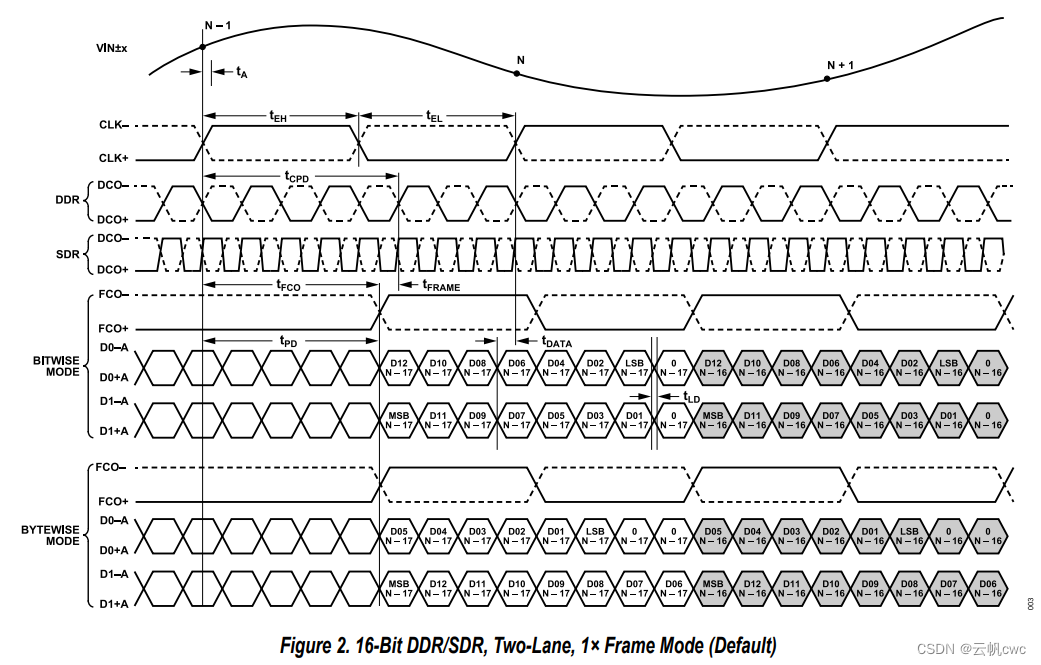

下图是AD9253的输出时序图:

时序图中ADC对VIN±x输入的信号进行模数转换,转换的码值经过并转串从DATA引脚输出,输出接口中通过DCO指示串行clock,通过FCO指示数据帧。DCLK的频率由ADC的Sample Rate,Resolution,输出Lane数和DDR还是SDR传输模式决定,以125Msps,14Bit,SDR传输,2个Lane为例,DCLK计算示例如下所示:

那么,在875MHz频率下的DCO下,在每个DCO的上升沿输出一位数据,FCO作为一个数据帧,在每个上升沿输出一个新的转换码值。由于AD9253为14BitADC,时序图中每个FCO下输出16位数据,那么两个Lane的情况下,当配置为BITWISE MODE,数据在两个Lane上交叉输出,舍弃最低位,当配置为BYTEWISE MODE时,在第一个Lane上输出BIT0-BIT6,舍弃低两位,在第二个Lane上输出BIT13-BIT7。

有个细节点,可以看到当VIN转换第N个数据时,DATA输出第N-17个数据,这是Pipeline型ADC的特点,其内部一般分为为多级转换,每级一般为Flash型ADC,同时并串转换也会加入delay,在两者的影响下,转换的数据时,经过17个CLOCK后才从ADC输出。

2.3、为什么要用ISERDESE2进行串并转换

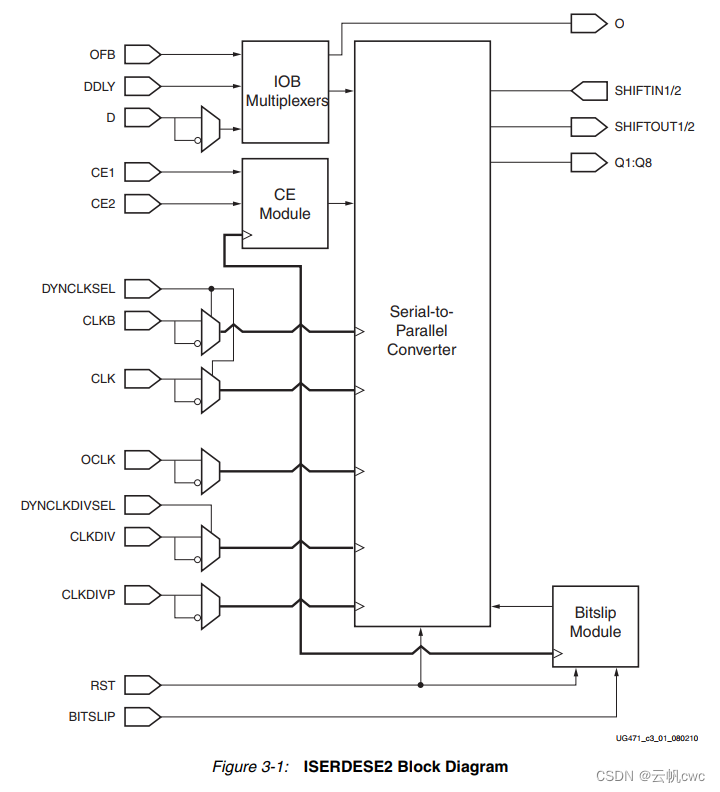

首先FPGA内部是并行运行的,为此AD9253驱动程序的核心就是对LVDS串行输出的DATA进行串并转换。相信初学者对于串并转换想到的就是在每个CLOCK边沿进行移位,但是通过上面对DCLK的计算可以看到,在875Mclock下该方式已经不是时序不满足了,而是时序爆炸,这个我会在跨时钟域处理中介绍时序报告的查看,并以400MHz和200MHzclock为例进行对比。基于此原因,Xilinx FPGA中集成了SelectIO资源,其中有专用的串并转换模块ISERDESE2,如下图所示:

基于此模块,无需复杂操作即可实现高速串行数据采集工作。时间原因,这周写一些介绍性内容,下周按照以下目录实现LVDS接口程序设计。