- 1BERT用于序列到序列的多标签文本分类_vanilla bert

- 2电脑装系统如何选择版本(w10安装多个版本sqlserver的步骤)_安装两个sqlserver

- 3Hive配置Spark计算引擎,速度快!_hive使用spark引擎

- 4宝塔面板部署腾讯云的域名

- 5Flask+Echarts搭建全国疫情可视化大屏_疫情大屏

- 651单片机程序存储器和数据存储器_8051单片机的存储器分为哪几个空间?中断服务程序的入口地址分别是什么?

- 7MySQL面试精华汇总

- 8Python flask请求上下文(RequestContext)和应用上下文(AppContext)_python app_context

- 9通过权威数据共享使跨政府变得成功_数据资源共享的例子

- 10Create2024百度AI开发者大会记录

Xilinx Aurora 64B/66B 协议板间传输数据_64b/66b txsequence_in

赞

踩

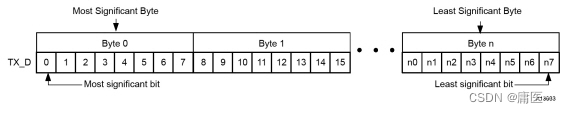

接口传输时序

帧接口组帧方式:

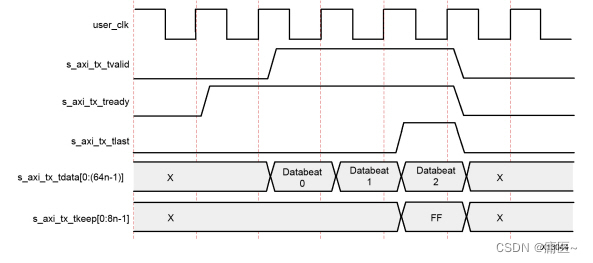

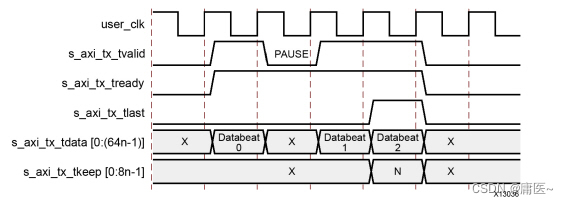

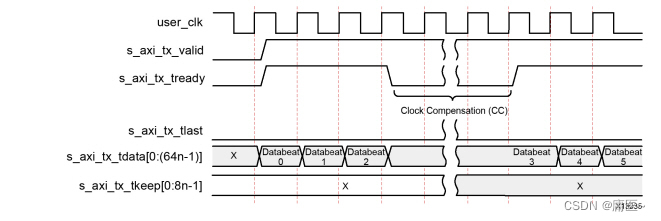

帧接口时序

简单传输

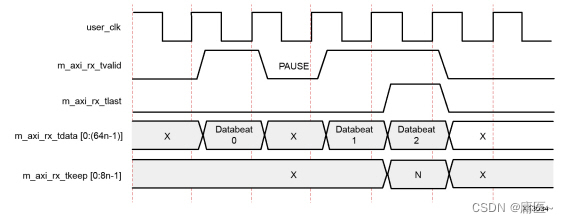

数据暂停传输

时钟补偿式数据传输

显示核心自动中断数据传输时,时钟补偿序列被发送。数据传输暂停时钟补偿

数据接收

帧式传输方式传输效率

有两个因素影响极光64B/66B核心的传输效率:

1. 帧的大小。

2. 来自gearbox 的数据无效请求,每32个user_clk(txusrclk2)周期后发生一次。

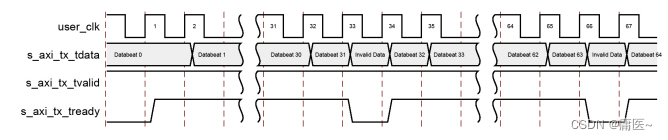

GTX和GTH收发器中的gearbox 需要定期暂停,以考虑时钟分频比和64B/66B编码。这在AXI4-Stream接口中显示为背压,用户数据需要在每32个周期后停止一个周期(如图)。来自Aurora 64B/66B核心的用户界面中的s_axi_tx_tready信号在一个周期内被解除,每32个周期一次。暂停周期用于补偿gearbox 的64B/66B编码。

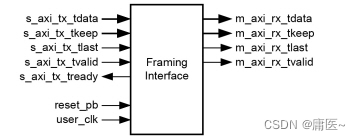

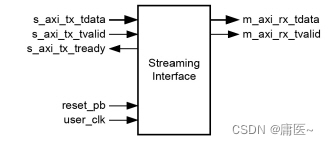

流式数据接口

流式接口时序

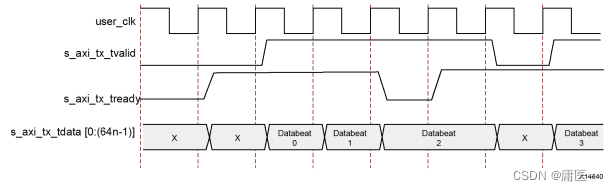

发送时序

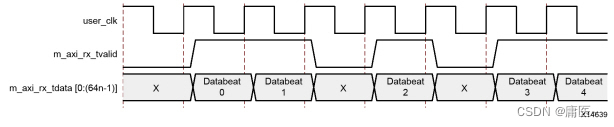

接收时序

调试经验

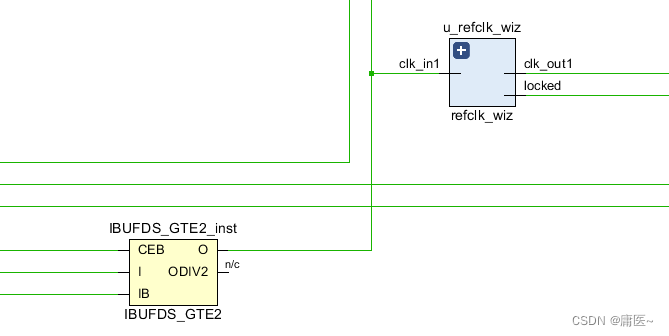

PMA_INIT为同步复位信号,需要在ref_clk来到之后拉低该信号进行复位,可以采用如下的方式,差分ref_clkp/ref_clkn经过IBUFDS_GTE2后输出时钟ref_clk提供给aurora IP核,同时例化一个PLL,ref_clk经过PLL后产生init_clk和drp_clk提供给aurora IP核,同时产生locked信号,取反后作为IP核复位信号。这样就保证了同步复位。

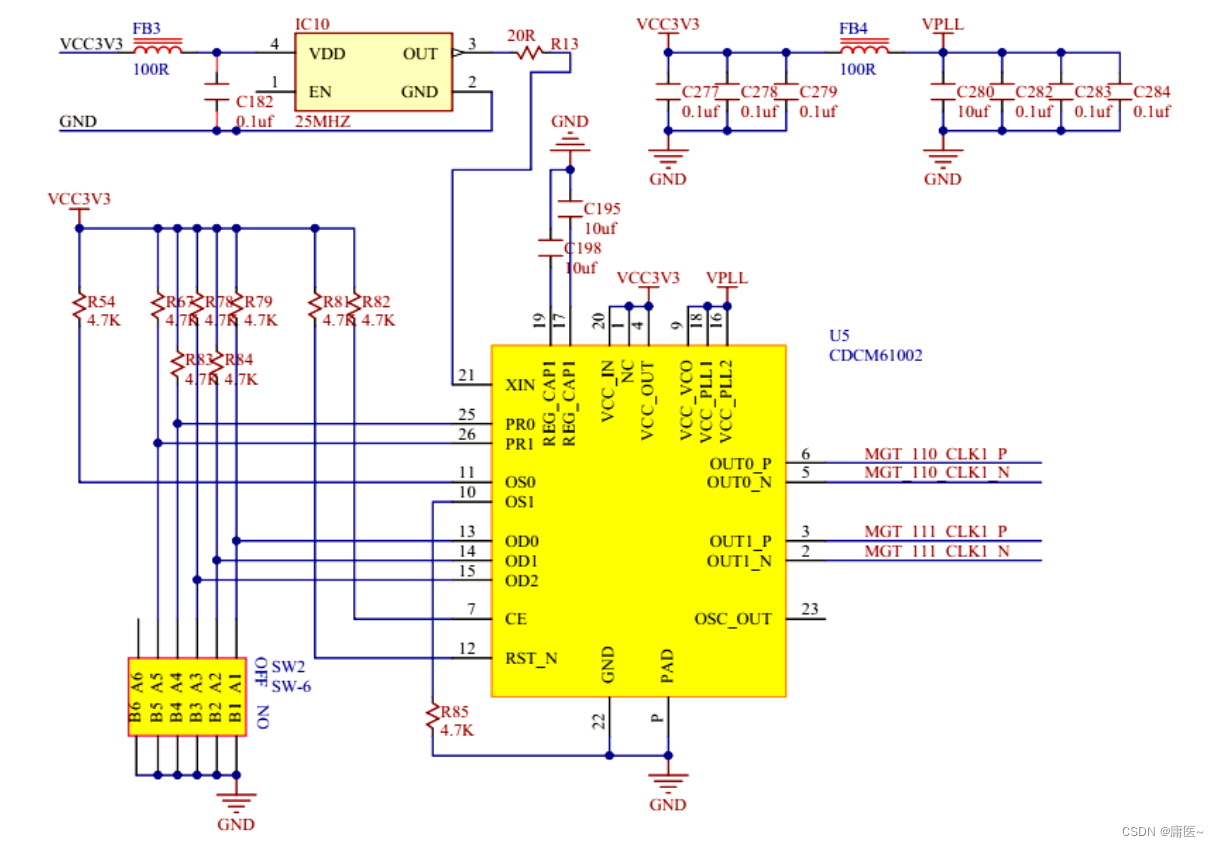

对于开发板的编程晶振时钟,拨码开关的高低电平根据电路图进来拨码,“on”代表开关打开,并不代表置1,要根据电路图,下图拨到“on”后,电路与GND导通,此时提供给编程晶振的为低电平。

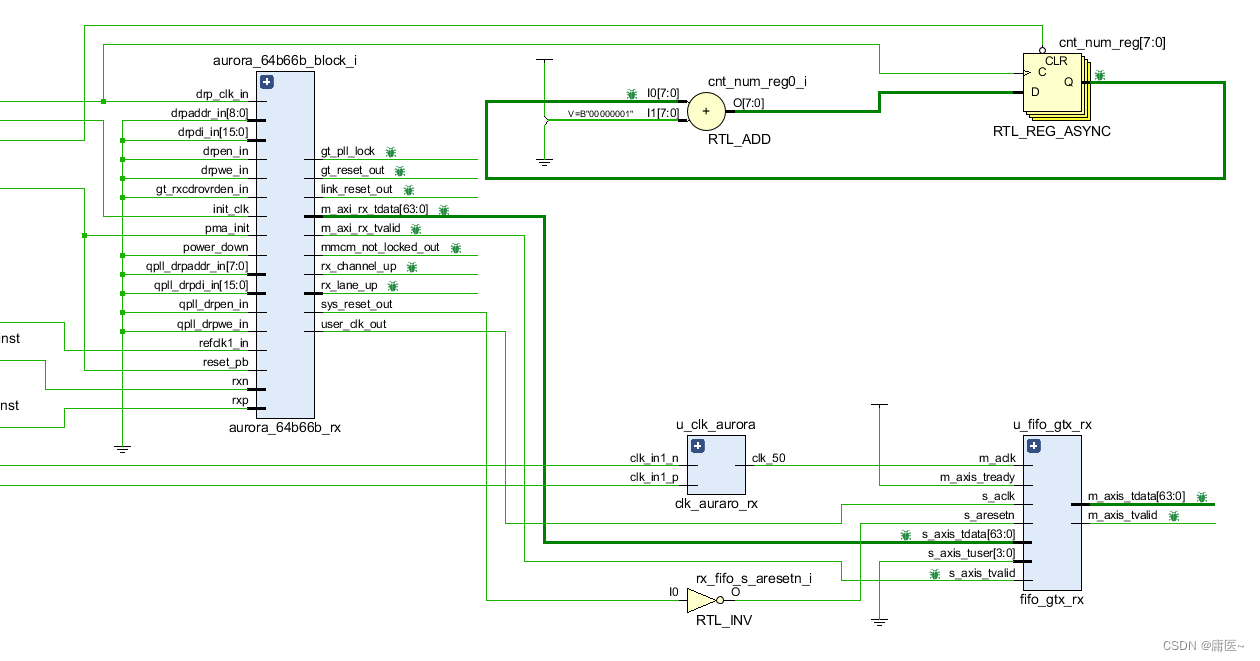

对于TX端,可连接一个异步FIFO,这样解决了数据源的数据到aurora IP核tx_data的跨时钟域问题,

同样对于RX,连接一个异步FIFO

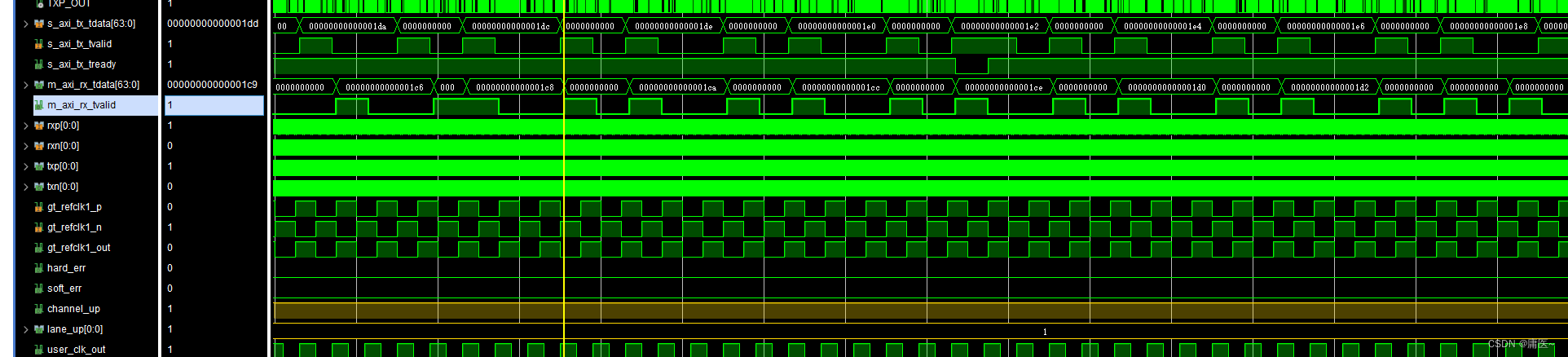

在进行验证时,lane_up和channel_up代表链路建立和通道建立,gt_pll_lock和gt_qpllock_out代表PLL锁定,该信号可在调试过程中验证时钟是否给入并频率正确,调试成功的很大一部分因素在于输入时钟

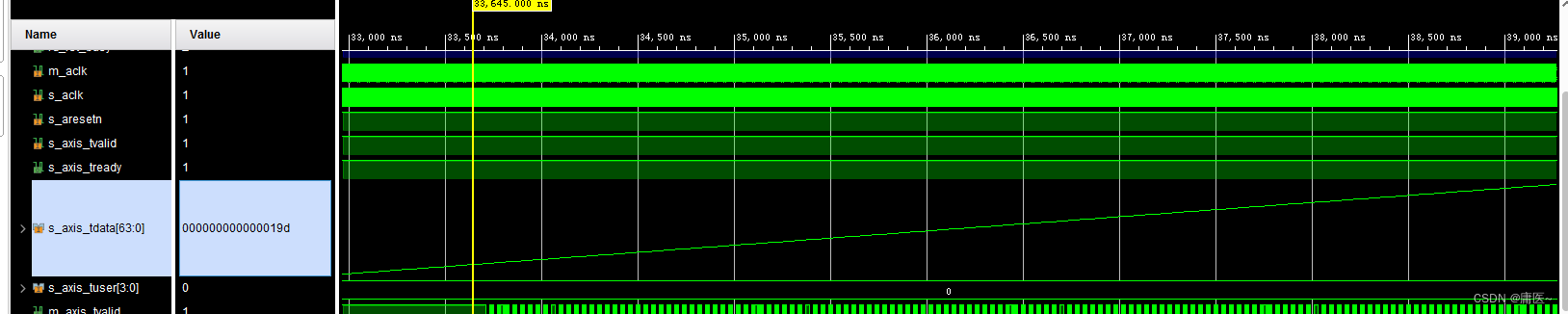

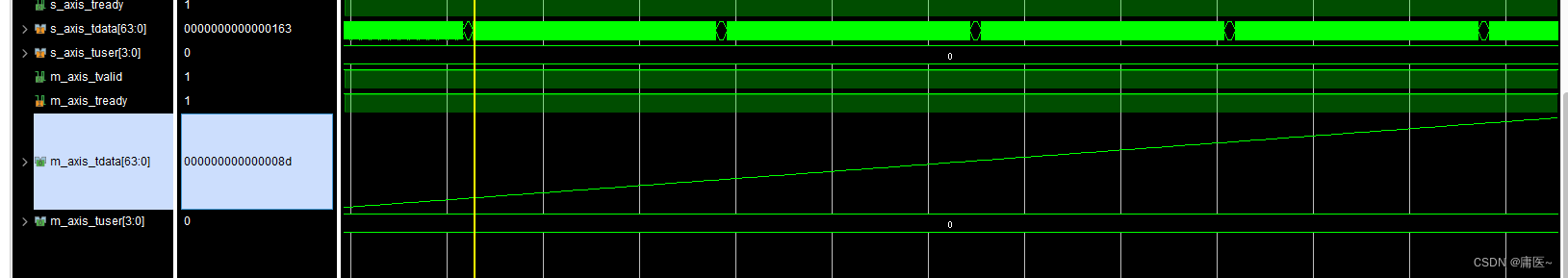

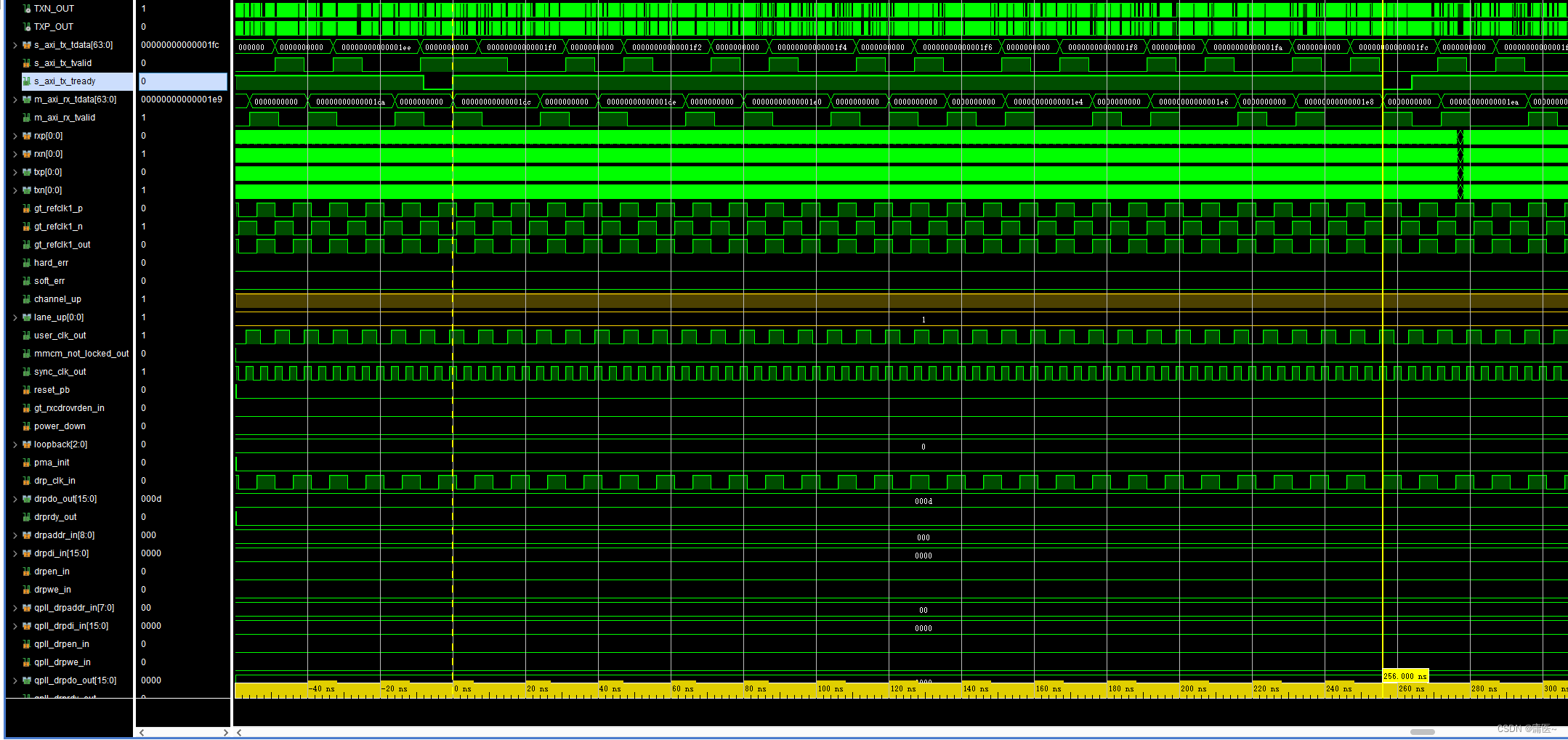

下图是流式传输数据的仿真图,tx_tready和tx_tvaild同时拉高时数据有效传输,rx_tavild拉高时代表RX接收的数据有效

tx_tready每隔256ns拉低一次,clk_user的周期为8ns, 说明IP核每隔32个时钟周期进行一次时钟补偿,

对于tx_fifo的输入和rx_fifo的输出,tx_fifo的写时钟和rx_fifo的读时钟速率小于clk_user, 所以对于可以向tx_fifo一直写入数据,rx_fifo中也一直由数据读出。