- 1Python中collections模块中的deque_from collections import deque

- 2DS18B20温度传感器学习笔记_ds18b20测量范围

- 32022科大讯飞AI开发者大赛,来了!_led生产封装瑕疵检测识别代码

- 4“AI作曲家”Suno引爆音乐圈!_suno 元标签详解

- 5eclipse 提交git失败_简单10步教你使用eclipse整合gitee码云实现共享开发

- 6关于分布式和集群的介绍_分布式集群作用

- 7【数据结构】树、二叉树与堆(长期维护)

- 8python学习-pandas基础

- 9微信小程序使用openid生成唯一数字ID(哈希算法)_微信openid生成规则

- 10系统集成项目管理工程师~关于成本的计算题_系统集成计算两种材料投入数量

FPGA时钟:驱动数字逻辑的核心

赞

踩

一、引言

在FPGA(现场可编程门阵列)设计中,时钟信号是不可或缺的关键要素。时钟信号作为时序逻辑的心跳,推动着FPGA内部各个存储单元的数据流转。无论是实现复杂的逻辑运算还是处理高速数据流,都需要精确的时钟信号来保证时序的正确性和数据的准确性。本文将详细介绍FPGA时钟的基本概念、时钟电路结构原理以及时钟设计中的重要考量。

二、FPGA时钟的基本概念

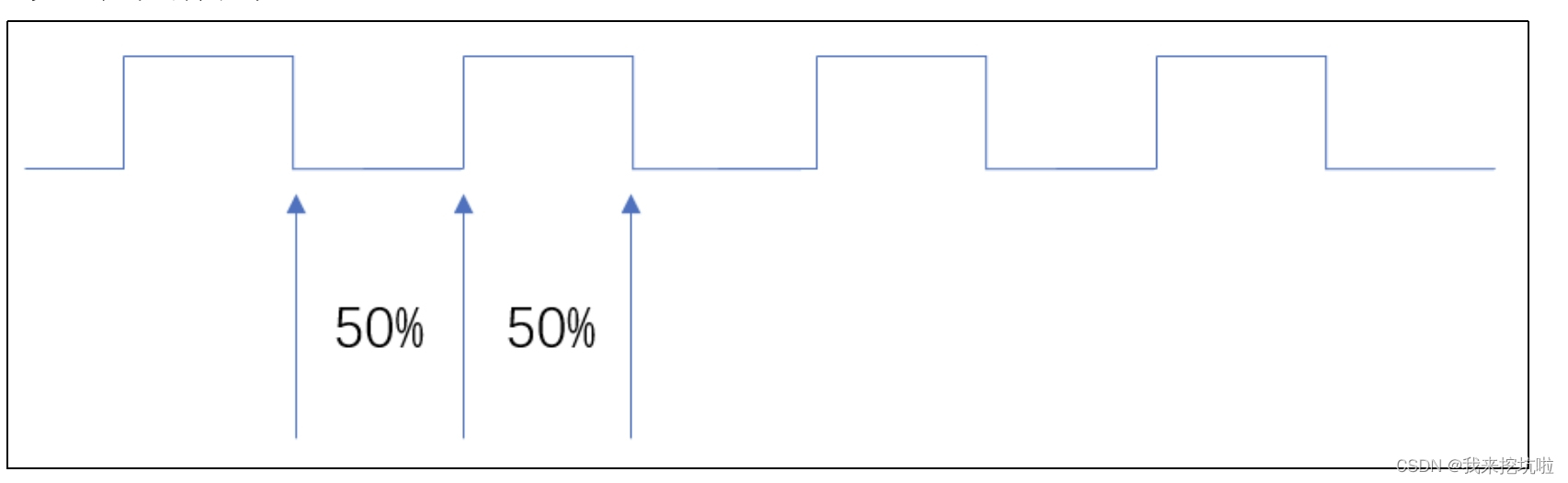

FPGA中的时钟信号通常具有固定的周期和频率,以方波的形式存在。时钟周期是指一个时钟边沿到下一个同类时钟边沿之间的时间间隔,而时钟频率则是时钟周期的倒数。时钟信号的基本特征包括占空比,即波形处于高电平占周期的时间比。

理想的时钟模型是一个占空比为 50%且周期固定的方波。时钟是 FPGA 中逻辑运行的

一个基准。如下图所示:

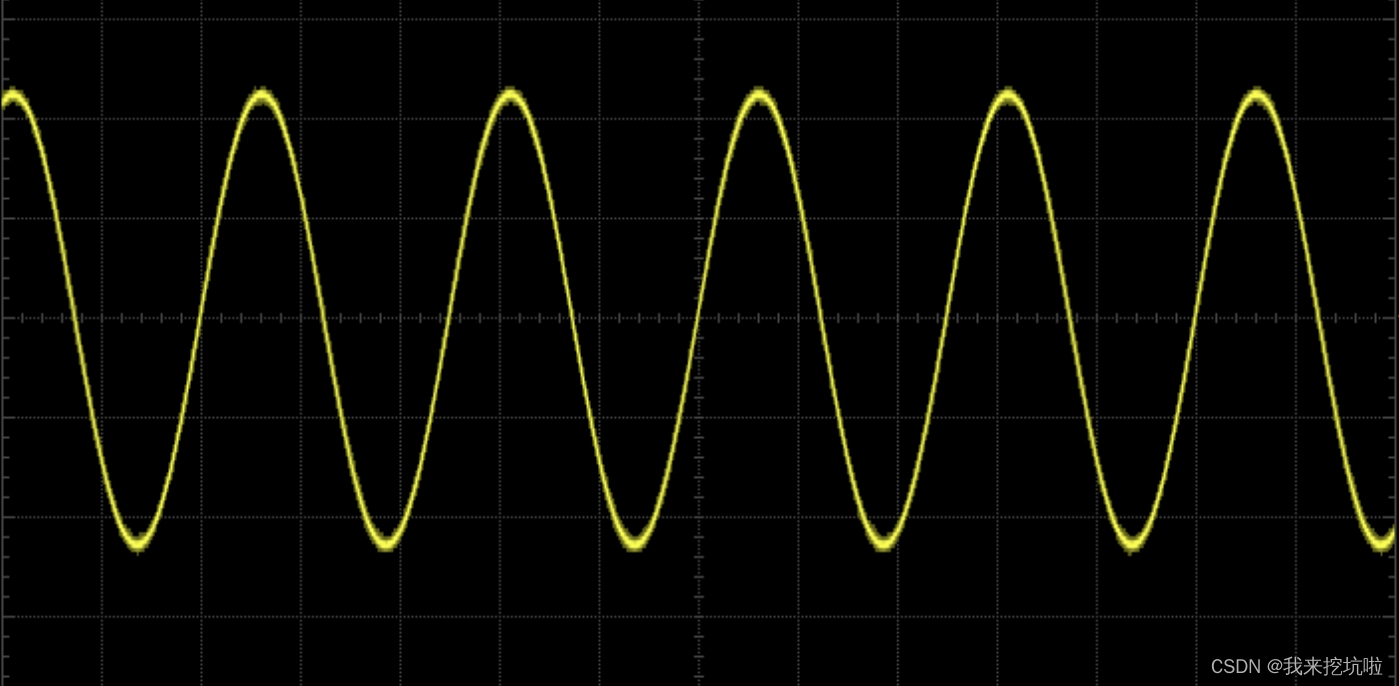

实际电路中输入给 FPGA 的晶振时钟信号其实是正弦波,这个波形不影响 FPGA 对时

钟的识别。

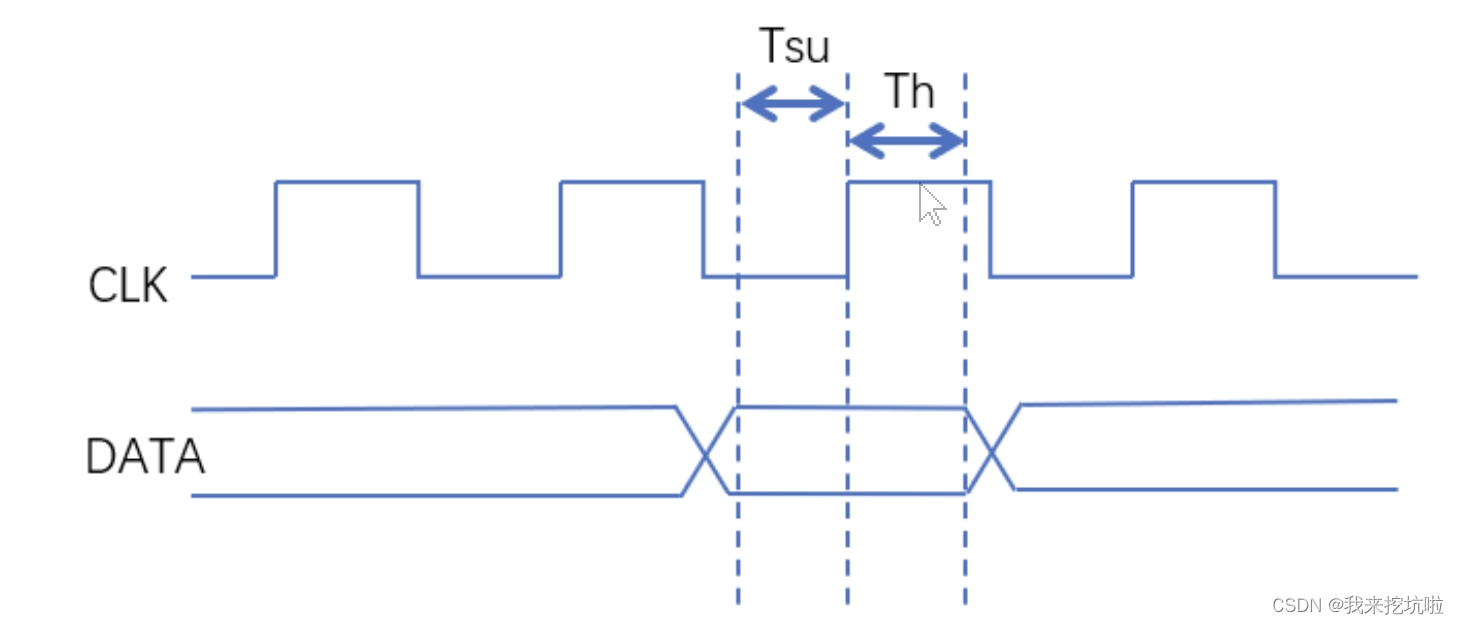

时钟信号在FPGA设计中起着至关重要的作用。它用于同步数字信号发射器和接收器,确保数据传输过程中的同步性。在数据传输过程中,发射器可以在时钟信号的每个上升沿或下降沿发送数据位,而接收器则可以使用相同的时钟信号来读取数据。时钟的有效边沿(即上升沿或下降沿)对于确保数据传输的正确性至关重要。

三、FPGA时钟电路结构原理

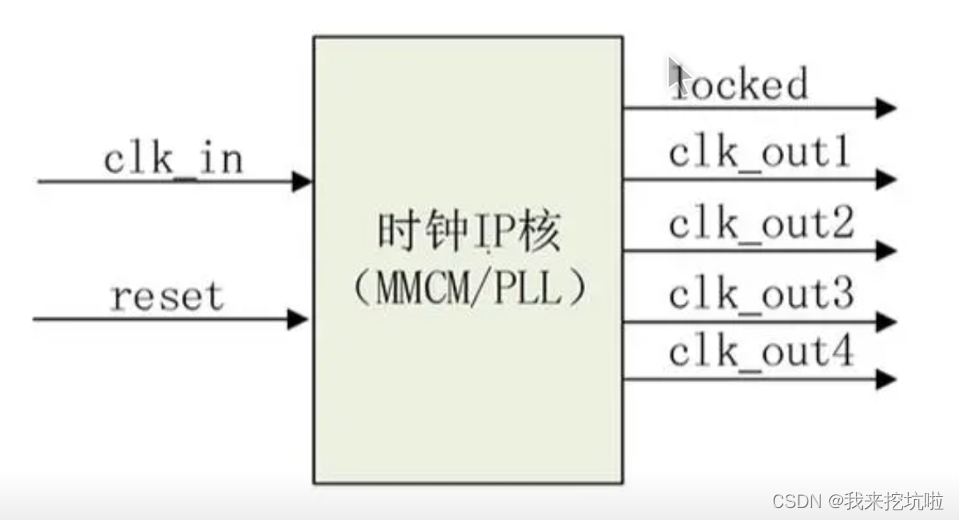

FPGA中包含了一些全局时钟资源,这些资源由时钟管理器(CMT)产生。以AMD公司近年的主流FPGA为例,时钟资源包括DCM(数字时钟管理器)、PLL(相位锁定环)和MMCM(混合模式时钟管理器)等【后续会对这些IP核进行比较系统的讲解】。其中,DCM在旧器件中应用较多,但目前已逐渐被淘汰;PLL是较为常见的时钟资源,可以实现分频、倍频及相位调节等功能;MMCM在PLL的基础上提供了更为强大的高阶功能,如动态相位调节、时钟扩频功能及时钟分配动态变化等。

在FPGA设计中,时钟信号的分配和布线是至关重要的。正确的时钟信号分配可以确保数据在正确的时间被处理和传输。时钟信号的布线质量对设计的性能和功耗有很大影响。此外,当设计中存在多个时钟域时,需要正确处理不同时钟域之间的数据传输,以防止时序违规和异步时钟域之间的不稳定性问题。

四、FPGA时钟设计的重要考量

- 时钟频率和时序约束:在设计FPGA时,需要根据应用需求选择合适的时钟频率。同时,为了确保时序要求得到满足,需要设置适当的时序约束,包括时钟频率约束、时序路径约束和时钟域约束等。

- 时钟缓冲与时钟延迟:在FPGA中,时钟缓冲和时钟延迟对时钟信号的传播和同步至关重要。需要注意时钟缓冲的插入和时钟延迟对设计的影响。

- 时钟偏移和抖动:时钟信号可能存在偏移和抖动,这可能导致时序不稳定或违反时序约束。因此,在时钟设计中需要考虑时钟信号的稳定性和可靠性。

- 门控时钟和多级逻辑时钟:在某些应用中,可能需要使用门控时钟或多级逻辑时钟来优化功耗或实现特定的功能。然而,这些时钟设计方式可能会引入额外的时序问题,需要仔细分析和验证。

五、结论

FPGA时钟是驱动数字逻辑的核心。在FPGA设计中,时钟信号的正确性、稳定性和可靠性对系统的性能和功能有着至关重要的影响。因此,在FPGA设计中需要充分考虑时钟信号的设计和实现方式,以确保系统的正确性和可靠性。