- 1操作系统教程 ( Linux) 版 学习笔记_自己话讲._现在linux主要使用在pc机和嵌入式,或者一些小型企业的服务器;而unix垄断着大型企

- 2Android Studio 的六种基本布局_android studio布局

- 3解决ImportError: cannot import name 'imread' from 'scipy.misc'(Anaconda3\lib\site-packages\scipy\misc)

- 4web安全:QQ号快速登录漏洞及被盗原理_超文本浏览框 qq快速登录

- 5Ubuntu为知笔记私有化部署_为知笔记 udp端口

- 6CLOUD 云计算进阶(十一)-Zookeeper Kafka集群_d1ykcogya1zkir cloudfront net

- 7【UE5】【WebUI】如何清除WebUI中的缓存_清除ue5的缓存文件

- 8大模型 Copilot 和 Agent 有什么区别?

- 9VsCode实用插件及使用_vscode 注释插件

- 10【云原生-Docker】快速搭建日常应用部署_docker要依赖iptables吗

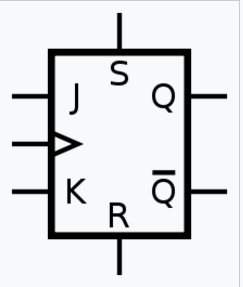

JK触发器计算机符号,JK触发器

赞

踩

JK触发器是数字电路触发器中的一种基本电路单元。JK触发器具有置0、置1、保持和翻转功能,在各类集成触发器中,JK触发器的功能最为齐全。在实际应用中,它不仅有很强的通用性,而且能灵活地转换其他类型的触发器。由JK触发器可以构成D触发器和T触发器。

中文名

JK触发器

外文名

JK flip-flop功能:

置0、置1、保持和翻转

基础:

主从RS触发器

特点:

不用考虑一次变化现象

JK触发器功能描述

编辑

语音

JK触发器[1]

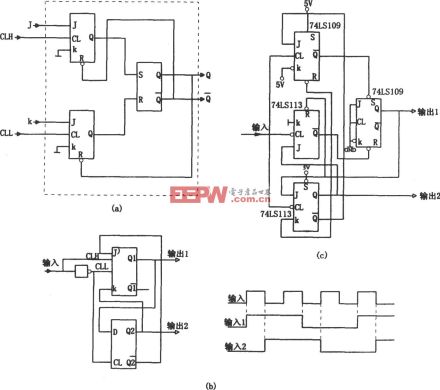

逻辑简图如图1所示

图1

JK触发器和触发器中最基本的RS触发器结构相似,其区别在于,RS触发器不允许R与S同时为1,而JK触发器允许J与K同时为1。当J与K同时变为1的同时,输出的值状态会反转。也就是说,原来是0的话,变成1;原来是1的话,变成0。 对应表如下:JK触发器运算

JK动作QQnext动作

00保持XX不变

01重置X0重置

10设置X1设置

11反转1(0)0(1)反转

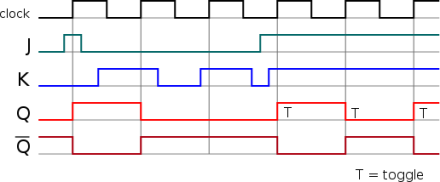

JK触发器的时序图

脉冲工作特性如图2所示

图2 JK触发器该触发器无一次变化现象,输入信号可在CP 触发沿由1变0时刻前加入。由图2可知,该电路要求J、K信号先于CP 信号触发沿传输到G3、G4的输出端,为此它们的加入时间至少应比CP 的触发沿提前一级与非门的延迟时间。这段时间称为建立时间test。

输入信号在负跳变触发沿来到后就不必保持,原因在于即使原来的J、K信号变化,还要经一级与非门的延迟才能传输到G3和G4的输出端,在此之前,触发器已由G12、G13、G22、G23的输出状态和触发器原先的状态决定翻转。所以这种触发器要求输入信号的维持时间极短,从而具有很高的抗干扰能力,且因缩短tCPH 可提高工作速度。

从负跳变触发沿到触发器输出状态稳定,也需要一定的延迟时间tCPL。显然,该延迟时间应大于两级与或非门的延迟时间。即tCPL大于2.8tpd。

综上所述,对边沿JK 触发器归纳为以下几点:

1.边沿JK 触发器具有置位、复位、保持(记忆)和计数功能; 2.边沿JK 触发器属于脉冲触发方式,触发翻转只在时钟脉冲的负跳变沿发生; 3.由于接收输入信号的工作在CP下降沿前完成,在下降沿触发翻转,在下降沿后触发器被封锁,所以不存在一次变化的现象,抗干扰性能好,工作速度快。

JK触发器产品分类

编辑

语音

JK触发器主从JK 触发器

电路结构

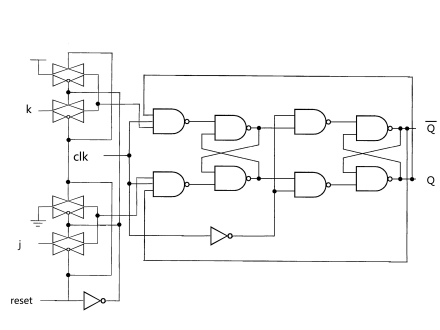

图3 JK触发器电路图主从JK 触发器是在主从RS触发器的基础上组成的,如图3所示。 在主从RS触发器的R端和S端分别增加一个两输入端的与门G11和G10,将Q端和输入端经与门输出为原S端,输入端称为J端,将Q端与输入端经与门输出为原R端,输入端称为K端。

工作原理

由上面的电路可得到S=JQ,R=KQ。代入主从RS触发器的特征方程得到:

当

J=1,K=0时,Qn+1=1;

J=0,K=1时,Qn+1=0;

J=K=0时,Qn+1=Qn;

J=K=1时,Qn+1=~Qn;

由以上分析,主从JK 触发器没有约束条件。在J=K=1时,每输入一个时钟脉冲,触发器翻转一次。触发器的这种工作状态称为计数状态,由触发器翻转的次数可以计算出输入时钟脉冲的个数。

工作特性

建立时间:是指输入信号应先于CP信号到达的时间,用tset表示。由图4可知,J、K信号只要不迟于CP信号到达即可,因此有tset=0。保持时间:为保证触发器可靠翻转,输入信号需要保持一定的时间。保持时间用tH表示。如果要求 CP=1期间J、K的状态保持不变,而CP=1的时间为tWH,则应满足:tH≥tWH。

图4 JK触发器电路图传输延迟时间:若将从CP下降沿开始到输出端新状态稳定地建立起来的这段时间定义为传输时间,则有:tPLH=3tpd tPHL=4tpd 最高时钟频率:因为主从触发器都是由两个同步RS 触发器组成的,所以由同步RS触发器的动态特性可知 ,为保证主触发器的可靠翻转,CP高电平的持续时间tWH应大于3tpd。同理,为保证从触发器能可靠地翻转, CP低电平的持续时间tWL也应大于3tpd。因此,时钟信号的最小周期为:Tc(min)≥6tpd 最高时钟频率fc(max)≤1/6tpd。

如果把图4的J、K触发器接成T触发器使用(即将J和K相连后接至高电平),则最高时钟频率还要低一些。因为从CP的下降沿开始到输出端的新状态稳定建立所需要的时间为tPHL≥4tpd,如果CP信号的占空比为50%,那么CP信号的最高频率只能达到fc(max)=1/2tPHL=1/8tpd。

JK触发器带清零功能的主从下降沿触发JK触发器

若 Reset=0时:

J=1,K=0时,Qn+1=1;

J=0,K=1时,Qn+1=0;

J=K=0时,Qn+1=Qn;

带清零功能的主从下降沿JK触发器J=K=1时,Qn+1=Qn;若 Reset=1时:

不论J、K与Qn的值,Qn+1=0。

JK触发器集成触发器

集成JK触发器的产品较多,以下介绍一种比较典型的高速CMOS双JK触发器HC76。该触发器内含两个相同的JK触发器,它们都带有预置和清零输入,属于负跳沿触发的边沿触发器,其逻辑符号和引脚分布如图5所示。其功能表如表7.5.1所示。如果在一片集成器件中有多个触发器,通常在符号前面(或后面)加上数字,以表示不同触发器的输入、输出信号,比如C1与1J、1K同属一个触发器。

综上所述

对主从JK 触发器归纳为以下几点:

1.主从JK触发器具有置位、复位、保持(记忆)和计数功能;

2.主从JK触发器属于脉冲触发方式,触发翻转只在时钟脉冲的负跳变沿发生;

图5 JK触发器电路图3.不存在约束条件,但存在一次变化现象。4.产生一次变化的原因是因为在CP=1期间,主触发器一直在接收数据,但主触发器在某些条件下(Q=0,CP=1期间J端出现正跳沿干扰或Q=1,CP=1期间K端出现正跳沿干扰),不能完全随输入信号的变化而发生相应的变化,以至影响从触发器 状态与输入信号的不对应。

JK触发器分立元件构成的触发器

两个PNP三极管(上拉管)并联构成二输入与非门电路,三个PNP三极管并联则构成三输入与非门电路。

每个按键按下时提供高电平,松开时提供低电平。CLK按下时主触发器工作,松开时从触发器工作。

词条图册

更多图册

参考资料

1.

Digital electronics and design with VHDL

.google book.25/2/2008[引用日期2017-05-12]