- 1车载摄像头总结_rccc,rccb

- 2Python爬虫记录-etree.HTML解析数据异常_python etree.html

- 3关于Windows2008R2服务器,Https未能创建 SSL/TLS 安全通道。Could not create SSL/TLS secure channel解决方案_windows2008 r2 tls12

- 4实验7 Mybatis注解式开发_mybatis注解开发实验报告

- 5Oracle数据库入门第一课(下载安装)_oracle下载安装教程

- 6Windows 2003安全设置大全

- 7【软件工程作业】 习题三_银行计算机储蓄系统

- 8ROS利用话题传输自定义消息类型_自定义的类可以通过ros话题来发送马

- 9web安全简介_Web安全:HTTP简介

- 10解释 Java 中的反射机制及其应用

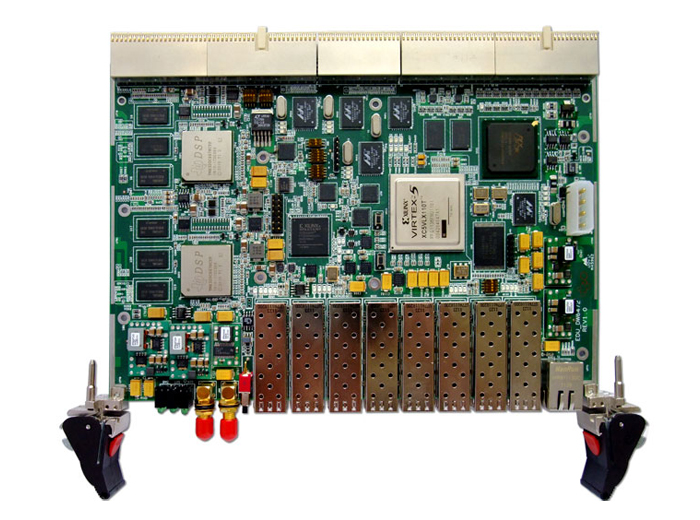

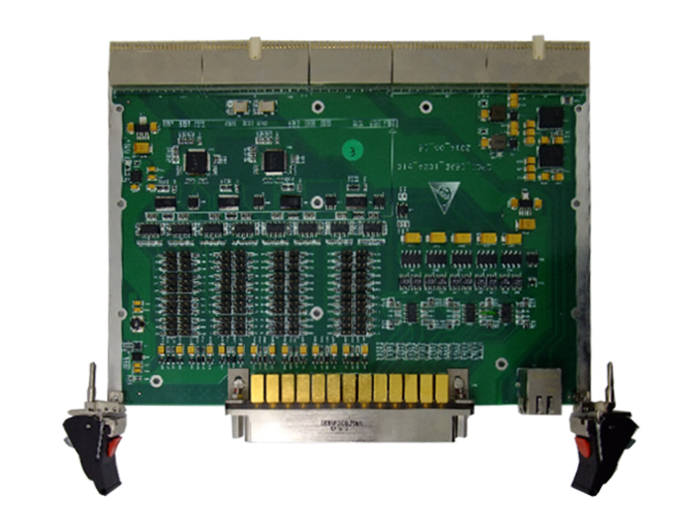

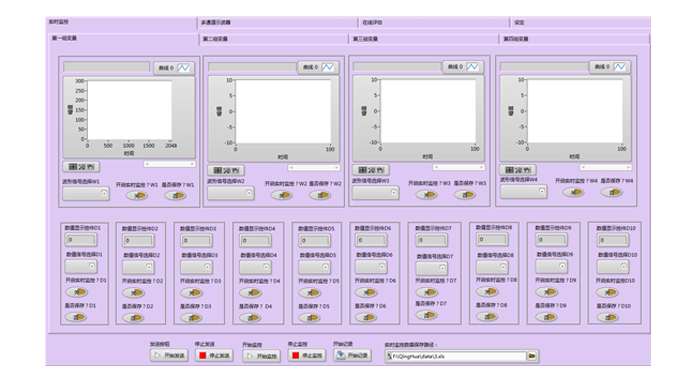

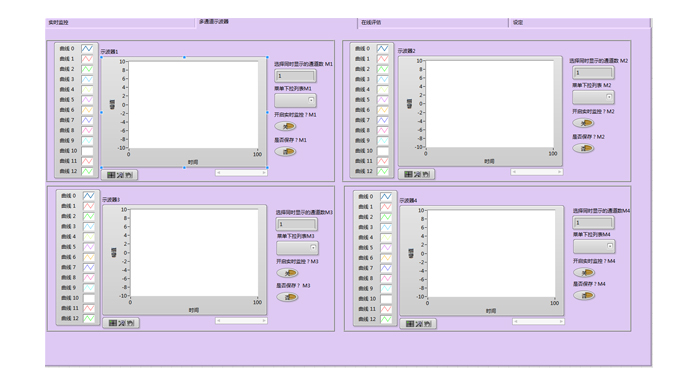

DSP实时分析平台设计方案:924-6U CPCI振动数据DSP实时分析平台

赞

踩

|