Zynq简介——FPGA学习笔记<7>

赞

踩

目录

一.xilinx Zynq UltraScale+ MPSoC

(1)APU(Application Processing Unit)

(2)RPU(Real-Time Processing Unit)

(3)GPU(Graphics Processing Unit)

(5)PMU(Platform Management Unit)

官网介绍:

Xilinx/PYNQ: Python Productivity for ZYNQ (github.com)

PYNQ - Python productivity for Zynq - Home

参考书目:《正点原子 DFZU2EG/4EV MPSoc 之 FPGA 开发指南》

一.xilinx Zynq UltraScale+ MPSoC

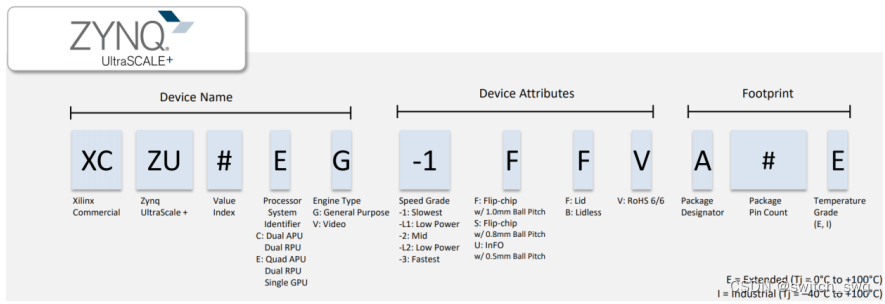

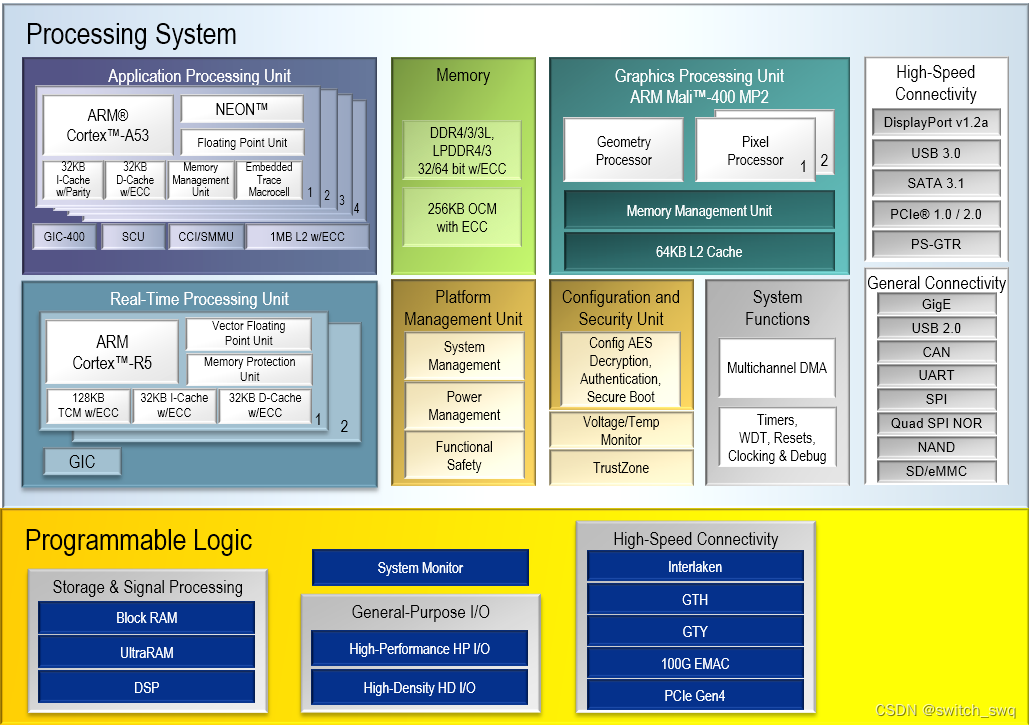

Zynq UltraScale+ MPSoC 是赛灵思推出的首款真正全可编程(All Programmable)异构多核处理 SoC 芯片。包含 PS(Processing System,处理器系统)和 PL(Programmable Logic,可编程逻辑)两部分。Zynq UltraScale+ MPSoC 整合了一个双核或四核 Cortex-A53 处理器、双核 Arm Cortex-R5F 实时处理器和一个传统的现场可编程门阵列(FPGA)逻辑部件,该器件的可编程逻辑部分基于 Xilinx 16nm FinFET+工艺的 UltraScale+系列 FPGA。这款芯片采用台积电公司 (TSMC) 新一代 16nm FinFET 工艺制程,它包含一个可扩展的 32 位或 64 位多处理器 CPU、用于实时处理图形和视频的专用硬化引擎、先进的高速外设,以及可编程逻辑,可用于汽车驾驶员辅助与安全、无线和有线通信、数据中心以及连接与控制等多种应用领域。

Zynq UltraScale+ MPSoC 系列产品分三种类型,分别是 CG 型器件、EG 型器件和 EV 型器件。其中 CG 型器件集成了由双核 Arm Cortex-A53 和双核 Arm Cortex-R5F 组成的 64 位处理系统;EG 型器件集成 了四核 Arm Cortex-A53 和双核 Arm Cortex-R5F,除此之外 EG 型器件还集成了 Arm Mali-400 MP2 (GPU)用来专门进行图像处理操作;而 EV 型器件在 EG 型器件的基础上再次增加了 H.264/H.265 视频编解码器(VCU)用来专门进行视频处理操作,它可以支持 60 帧每秒(fps)的速率同时进 行 4Kx2K 的编码和解码(约 6 亿像素/秒)或 15 帧每秒 8Kx4K 的编码解码。

1.MPSoC 简介

Xilinx 公司的 FPGA 芯片主要分为两大类,FPGA 和 SoC(System on Chip,片上处理系统),其中 FPGA 芯片只包含了可编程逻辑部分,而不包含处理器,如常见的 Spartan 系列、Artix 系列、Kintex 系列和 Virtex 系列。

每一个系列又根据制造工艺和架构的不同,分为 6 系列(45nm)、7 系列(28nm)、UltraScale(20nm) 和 UltraScale+(16nm),以提供不同的性能和功耗比。

Xilinx 的 SoC 是将可编程逻辑部分和处理器单元以及常见处理器外设封装在一起,集成到单颗芯片中, 并命名为“ZYNQ”,同样分为不同的系列,如 Zynq-7000(28nm)、Zynq UltraScale+ MPSoC(16nm)、 Zynq UltraScale+ RFSoC(16nm),如下图所示:

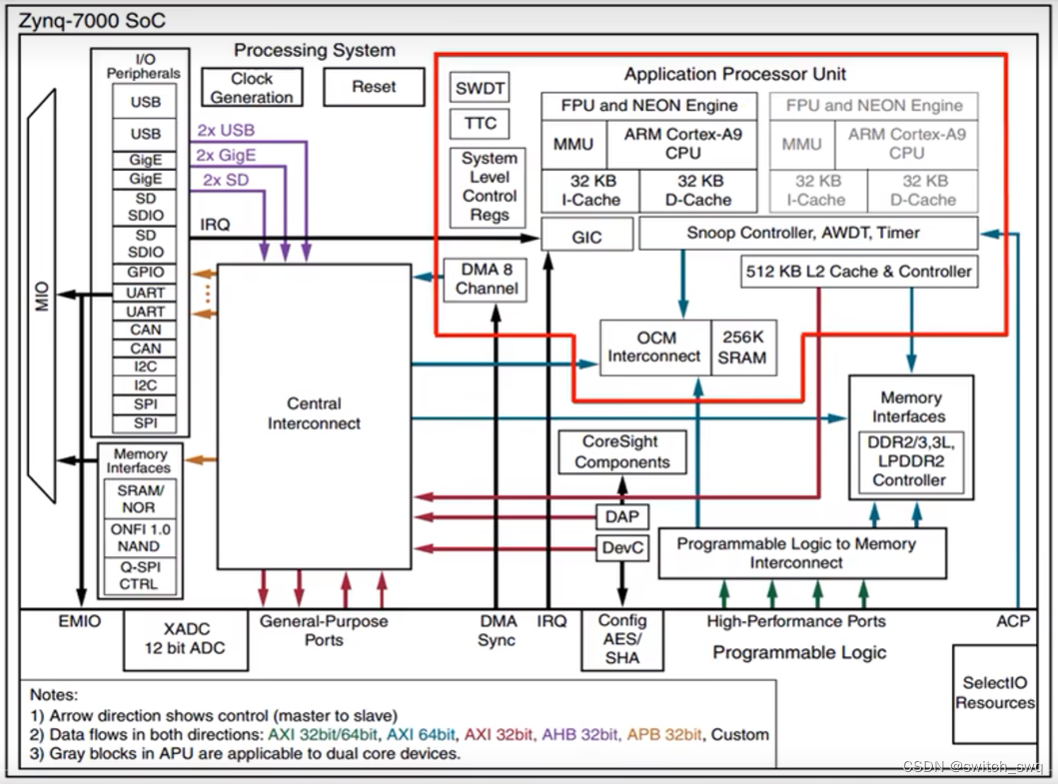

Zynq7000 系列组合了一个双核 Arm Cortex-A9 处理器和一个传统的现场可编程门阵列(FPGA)逻辑部件。由于该器件的可编程逻辑部分基于 Xilinx 28nm 工艺的 7 系列 FPGA,因此该系列产品的名称中添加了 “7000”,以保持与 7 系列 FPGA 的一致性,同时也方便日后本系列新产品的命名。

Zynq UltraScale+ MPSoC 的系统级性能功耗比相对 Zynq-7000 SoC 系列提升高达 5 倍。Zynq UltraScale+ MPSoC 整合了一个双核或四核 Cortex-A53 处理器、双核 Arm Cortex-R5F 实时处理器和一个传统的现场可编程门阵列(FPGA)逻辑部件,该器件的可编程逻辑部分基于 Xilinx 16nm FinFET+工艺的 UltraScale+系列 FPGA。

Zynq UltraScale+ MPSoC 部分系列的产品,还包含了 Arm Mail-400MP2(GPU)和 H.264/H.265 视频编 解码器,可提供原生 UltraHD 压缩及专用引擎,满足动态电源管理与安全配置需求,可以说是对 ZYNQ 7000 的升级版本。Zynq UltraScale+ MPSoC 非常适用于 5G 无线基础设施、面向数据中心和有线通信的软件定义网络、新一代汽车驾驶员辅助系统和无人驾驶系统 (ADAS)、工业物联网系统 (IIoT)、超高清和超高画质摄像机、航空电子以及便携式软件定义无线电等各种应用。

Zynq UltraScale+ RFSoC 在 SoC 架构中集成数千兆采样 RF 数据转换器和软判决前向纠错 (SD-FEC)。 配有 ARM Cortex-A53 处理子系统和 UltraScale +可编程逻辑,该系列是业界唯一单芯片自适应射频平台。 Zynq UltraScale+ RFSoC 系列可为模拟、数字和嵌入式设计提供适当的平台,从而可简化信号链上的校准和 同步。多代产品系列包含广泛的器件类型,具有不同的直接 RF 性能,可满足各种频谱需求和使用案例。

Zynq UltraScale+ MPSoC 产品在单个设备中集成了功能丰富的嵌入式处理系统(PS)和可编程逻辑(PL) UltraScale+架构,并且还包括片上存储器、多端口外部存储器接口以及丰富的外设连接接口集等等。

Zynq UltraScale+ MPSoC除了嵌入式处理系统功能强大外,它还包含了可编程逻辑(PL) UltraScale+架构, 能够灵活的去编辑我们想要的逻辑运算,实现各种各样的复杂功能。从本质上来讲,它还是一个片上处理系统(System on Chip,SoC)。

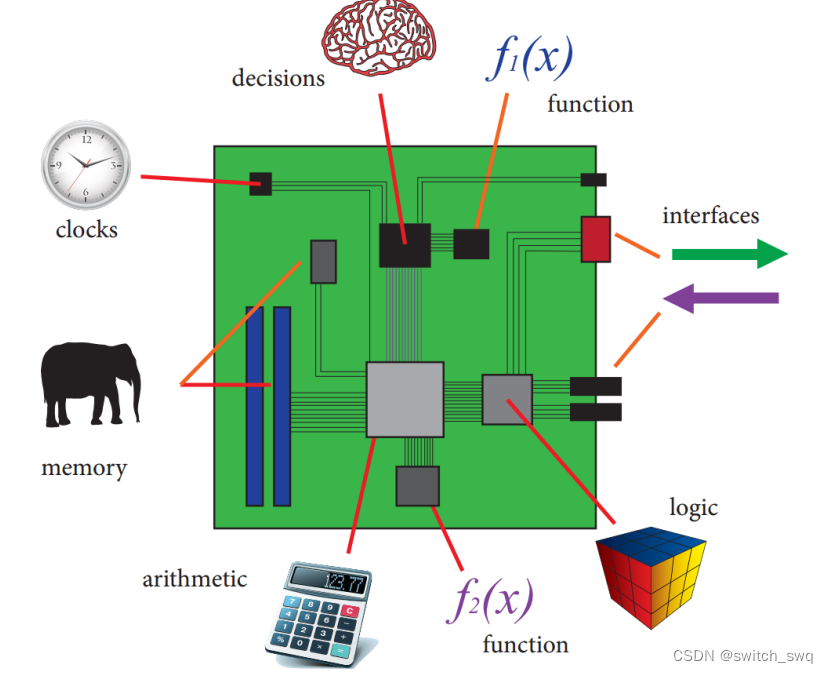

注:板上系统 (System-on-a-Board)示意图如下:

而片上系统(System-on-Chip)指的是在单个硅芯片就可以实现整个系统的功能。在一个芯片里就实现了存储、处理、逻辑和接口等各个功能模块,而不是像板上系统那样,需要用几个不同的物理芯片来实现。

在过去,SoC 这个术语常用于指专用集成电路(Application Specific Integrated Circuit,ASIC)。基于 ASIC 的 SoC 的代表性例子包括在 PC、平板和智能手机上使用的处理器,如华为旗舰手机中的麒麟系列芯片。这些处理器典型地是由至少两个处理器核、存储器、图形处理器、接口和其他功能模块组合起来的。 基于 ASIC 的 SoC 的主要缺点有两个:

1、开发周期长且成本巨大;

2、缺乏灵活性。

开发 ASIC 时不可重 用的工程投入是巨大的,使得这种 SoC 类型只适合于大批量而且寿命有限的产品中。 ASIC SoC 的局限性导致它们不适用于很多应用,特别是当快速投入市场能力、灵活性和升级能力已 经成为重要的关键因素。对于小批量或中批量的产品,ASIC SoC 也不是好的解决方案。

可编程片上系统(SOPC,System-on-Progammable-Chip)为上述应用提供了一个更灵活的解决方案: 一种在可编程、可重新配置的芯片上实现的 SoC。可编程的芯片指的就是 FPGA。FPGA 天生的灵 活性使其可以被随心所欲地重新配置,以实现不同系统的功能,包括嵌入式处理器。和使用 ASIC 来实现 SoC 相比,FPGA 能构成更为基础灵活的平台,方便系统的升级。

与基于 ASSP 的固定 SoC 解决方案不同,Zynq UltraScale+ MPSoC 能通过灵活的 32 或 64 位数据宽度的处理系统提供最大的可扩展性。它能将关键应用(例如图形和视频管线)分配给专用处理模块来处理,并通过有效的电源域 (power domain) 和电源孤岛 (power island) 来开启和关闭模块。Zynq UltraScale+ MPSoC 提供多种互连选项、DSP 模块以及可编程逻辑选择,因而具备整体灵活性,可满足 用户的各种 应用需求。该产品系列具备出色可扩展性,使设计人员能够利用单个平台和行业标准工具开发出低成本以 及高性能应用。

2.FPGA简介

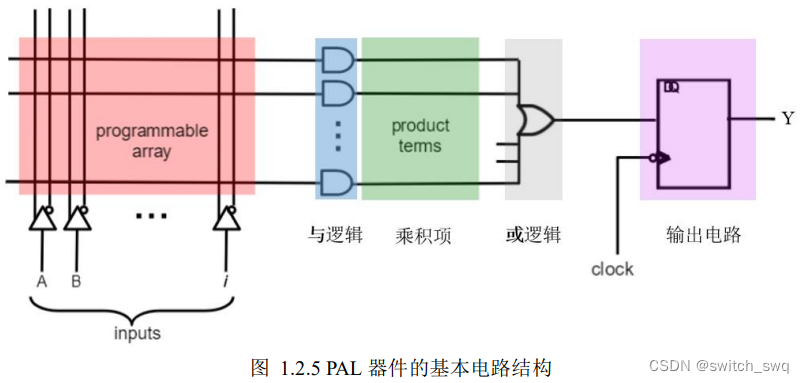

可编程逻辑器件(Programmable Logic Device,PLD),目前常见的 PLD 大体上可以分为 SPLD(simple PLD,简单 PLD)、CPLD(complex PLD,复杂 PLD)和 FPGA(field-programmable gate array,现场可编程门阵列)。SPLD 中又可分为 PLA、PAL 和 GAL 几种类型。FPGA 也是一种可编程逻辑器件,但由于在电路结构上与早期已经广为应用的 PLD 不 同,所以采用 FPGA 这个名称,以示区别。

通过扩展 SPLD 的概念就可以得到 CPLD。CPLD 是复杂可编程逻辑器件,相当于将多个 PAL 用可编程互联阵列(Programmable Interconnect Array,PIA)连接起来,形成一个大的 PLD,如下图所示:

上图中的 Logic block(逻辑块)通常被称为逻辑阵列模块,或者 LAB(Logic Array Block)。每个 LAB 相当于一个 PAL 电路,不同型号的 CPLD 器件可以包含十几个甚至上百个 LAB。通过 PIA 将这些 LAB 连接起来,就可以构成规模更大的逻辑电路了。另外,在 PAL 中,I/O 管脚是直接连接到逻辑的。而在 CPLD 中,I/O 管脚是通过 PIA 从器件的主要逻辑中分离出来的。I/O 管脚有它自己的控制逻辑,I/O 控 制单元可以根据需要将相应的引脚设置成输入、输出或双向工作模式。

CPLD 相对于 SPLD 最大的优势就是拥有更大的逻辑资源和布线的可能性。CPLD 中 LAB 逻辑和 PIA 是完全可编程的,使得它具有在单芯片中非凡的设计灵活性。CPLD 的 I/O 特性和功能也远比 SPLD 中简 单的 I/O 更有价值。

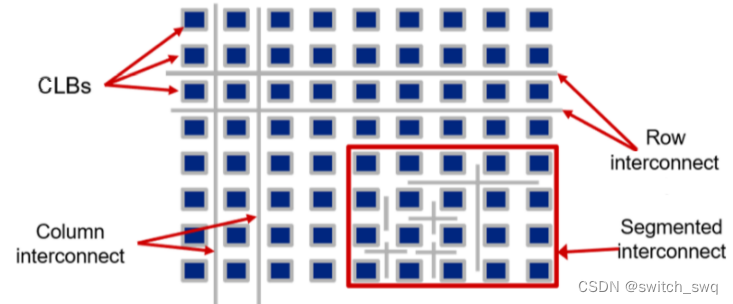

FPGA 由许多“可配置逻辑模块”(Configurable Logic Block,CLB)、输入/输出单元(I/O Block, IOB)和分布式的可编程互联矩阵(Programmable Interconnection Matrix,PIM)组成。在 FPGA 中,CLB 被布置成阵列的形式,如图 1.2.7 所示。可编程的布线资源分布在 CLB 与 CLB 之间,像大城市的街道一 样纵横联接。这些布线资源分为行互联和列互联,可以跨过整个器件,也可以是局部 CLB 之间的互联。

我们将图进行对比可以发现,FPGA 中的布线资源看上去似乎比 CPLD 中的互联阵列更简单,但它实际上提供了更大的功能性和连通性。FPGA 中的布线资源使得器件中所有的逻辑资源都可 以与芯片内其他资源进行通信,这种结构可以实现更大容量、低成本的逻辑器件。

在前面所讲的各种 SPLD 和 CPLD 电路中,都采用了与或逻辑阵列加上输出逻辑单元的结构形式。而 FPGA 则采用了完全不同的电路结构形式(查找表,LUT)

3.MPSoC PL 简介

Zynq UltraScale+ MPSoC PL 部分等价于 FPGA,因此我们将首先介绍 FPGA 的架构。

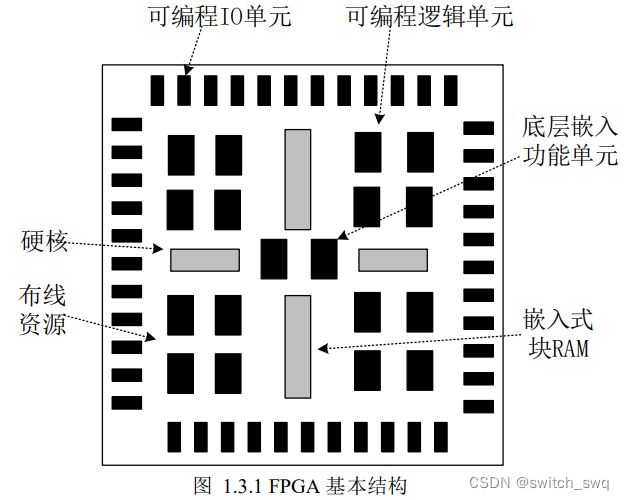

简化的 FPGA 基本结构由 6 部分组成,分别为可编程输入/输出单元、基本可编程逻辑单元、嵌入式块 RAM、丰富的布线资源、底层嵌入功能单元和内嵌专用硬核等,如下图所示:

(1)可编程输入/输出单元

目前大多数 FPGA 的 I/O 单元被设 计为可编程模式,即通过软件的灵活配置,可以适配不同的电气标准与 I/O 物理特性;可以调整匹配阻抗特性、上下拉电阻、以及调整驱动电流的大小等。 FPGA 支持的 I/O 电气标准有 LVTTL,LVCMOS,SSTL,HSTL,LVDS,LVPECL 和 PCI 等。一些高端 FPGA 通过 DDR 寄存器 技术,甚至可以支持高达 2Gbit/s 的数据数率。

Zynq UltraScale+ MPSoC 上的通用输入/输出功能(IOB)合起来被称作 SelectIO 资源,每个 I/O 都是可配置的,可以遵循多种 I/O 标准。I/O 分为高范围(HR,high-range)、高性能(HP)和高密度(HD)三种类型。其中 HR 类型提供最广泛的电压支持,从 1.2V 到 3.3V。HP 类型支持 1.0V 到 1.8V 它对性能操作进行了优化。HD 类型的 IO 一般一个 BANK 上由 24 个 IO 组成,能提供从 1.2V 到 3.3V 的电压支持。

所有的 I/O 引脚都封装在 BANK 中,每个 BANK 上可以封装 52 个 HP 引脚,或者 52 个 HR 引脚,或 者 24 个 HD 引脚。每个 BANK 有一个公共的 VCCO 输出缓冲器电源,除了给输出缓冲器供电外也可以为 输入缓冲器供电。此外,HR BANK 可以一分为二,这两部分各自都有自己的 VCCO 供电。一些单端输入缓冲器需要一个内部产生的或外部应用的参考电压(VREF)。VREF 引脚可以直接连接 PCB,或者从 FPGA 内 部产生。

所有输入和输出 IO 可以配置为组合型(wire)或注册型(reg)。所有输入和输出均支持 DDR (Double data rate)。任何输入或输出都可以单独延迟高达 1,250ps,分辨率为 5-15ps,这种延迟被称为 IDELAY 和 ODELAY。我们可以通过增减 IODELAY 的延迟步进进而调整 IODELAY 的延迟时间,也可以将 IODELAY 级联在一起,使单个方向上的延迟量增加一倍。

Zynq UltraScale+ MPSoC 的 IO 资源还支持串并转换。每个 I/O 引脚拥有一个 IOSERDES(ISERDES 和 OSERDES),能够执行 2、4 或 8 位可编程宽度的串行到并行或并行到串行转换。

(2)基本可编程逻辑单元

基本可编程逻辑单元是可编程逻辑的主体,可以根据设计灵活地改变其内部连接与配置,完成不同的逻 辑功能。FPGA 一般是基于 SRAM 工艺的,其基本可编程逻辑单元几乎都是由查找表(LUT,Look Up Table) 和寄存器(Register)组成。Xilinx UltraScale 系列 FPGA 内部查找表可以配置为带有一个输出的 6 输入 LUT, 或者两个带有独立输出但共用输入的 5 输入 LUT,查找表一般完成纯组合逻辑功能。FPGA 内部寄存器结构相当灵活,可以配置为带同步/异步复位或置位的时钟使能触发器,也可以配置成锁存器,FPGA 依赖寄 存器完成同步时序逻辑设计。 一般来说,比较经典的基本可编程逻辑单元的配置是一个寄存器加一个查找表,但是不同厂商的寄存器 与查找表也有一定的差异,而且寄存器与查找表的组合模式也不同。当然这些可编程逻辑单元的配置结构随着器件的不断发展也在不断更新,最新的一些可编程逻辑器件常常根据需求设计新的 LUT 和寄存器的配置比率,并优化其内部的连接构造。 例如,Altera 可编程逻辑单元通常被称为 LE(Logic Element),由一个寄存器加一个 LUT 构成。Altera 大多数 FPGA 将 10 个 LE 有机地组合在一起,构成更大的功能单元——逻辑阵列模块(LAB,Logic Array Block)。LAB 中除了 LE 还包含 LE 之间的进位链,LAB 控制信号,局部互联线资源,LUT 级联链,寄存器级联链等连线与控制资源。 Xilinx UltraScale 系列 FPGA 中的可编程逻辑单元叫 CLB(Configurable Logic Block,可配置逻辑块) 每个 CLB 包含一个逻辑运算片(每个逻辑运算片包含 8 个 LUT 16 个寄存器)。逻辑运算片有两种类型, 分别是 SLICEL 和 SLICEM。SLICEM 中的 LUT 可以配置为 64 位 RAM、32 位移位寄存器(SRL32)或两个 16 位移位寄存器。与上一代 Xilinx 设备中的 CLB 相比,UltraScale 体系结构中的 CLB 增加了路由和连接 性。并且 UltraScale 的 CLB 还有额外的控制信号去使能更大的寄存器封装,可以提高设备的利用率。

注:xilinx新一代 UltraScale 结构可参考《xilinx FPGA 权威设计指南》

(3)嵌入式块 RAM

目前大多数 FPGA 都有内嵌的块 RAM(Block RAM),FPGA 内部嵌入可编程 RAM 模块,大大地拓展了 FPGA 的应用范围和使用灵活性。不同器件商或不同器件族的内嵌块 RAM 的结构不同,Lattice 常用的 块 RAM 大小是 9Kbit;Altera 的块 RAM 最灵活,一些高端器件内部同时含有 3 种块 RAM 结构,分别是 M512 RAM,M4K RAM,M9K RAM。 每个基于 UltraScale 架构的设备都包含大量的 36Kb 块 RAM(Block RAM,简称 BRAM),可以配置 为一个 36Kb RAM 或两个独立的 18Kb RAM;每个块 RAM 都有两个完全独立的端口,且每个端口都可以读写数据,读写数据由时钟进行控制。每个块 RAM 列中有一个使能信号,这个信号能够让垂直相邻的块 RAM 之间级联,这样就可以创建大型、快速的存储阵列或者创建 FIFO,而且大大降低了功耗。 对于 RAM 来说,所有输入的数据、地址、时钟使能信号和写入使能都会被寄存。比如说输入一个地址 数据,这个地址数据就会被锁定(除非地址锁关闭)寄存,在下一次操作来临之前,地址寄存器的值是不会发生改变的。在写操作期间,也可以输出数据,输出的数据可以是先前存储的数据也可以是新写入的数据,当然在写操作期间也可以不输出数据。对于在设计中未使用的块 RAM 会自动关闭,以减少总功耗。在每个块 RAM 上还具有额外的引脚来控制动态功率的门控特性。 对于 Xilinx UltraScale 系列 FPGA 来说,除了具有 BRAM 资源外,还有一种 UltraRAM 资源。UltraRAM 是一种高密度、双端口、同步内存块,用于一些 UltraScale+系列器件。这两个端口共用同一个时钟,可以处理 4K x 72 位的数据,每个端口都可以独立地对内存数组进行读写操作。UltraRAM 支持两种类型的写操作方案,第一种模式与块 RAM 写操作模式一致;第二种模式允许控制数据的奇偶字节写入。多个 UltraRAM块可以级联在一起创建更大的内存阵列。UltraRAM 可以用专用的路径使整个列的存储区域连接在一起,这 使得 UltraRAM 成为替代 SRAM 等外部存储器的理想解决方案,它可以灵活的支持级联从 288Kb 到 36Mb 的存储空间,用以满足许多不同的内存需求。

(4)丰富的布线资源

布线资源连通 FPGA 内部的所有单元,而连线的长度和工艺决定着信号在连线上的驱动能力和传输速 度。FPGA 芯片内部有着丰富的布线资源,这些布线资源根据工艺、长度、宽度和分布位置的不同而划分为 4 类不同的类别:

第一类是全局布线资源,用于芯片内部全局时钟和全局复位/置位的布线;

第二类是长线资源,用以完成芯片 Bank 间的高速信号和第二全局时钟信号的布线;

第三类是短线资源,用于完成基本逻辑单元之间的逻辑互连和布线;

第四类是分布式的布线资源,用于专有时钟、复位等控制信号线。

在实际中设计者不需要直接选择布线资源,布局布线器可自动地根据输入逻辑网表的拓扑结构和约束条件选择布线资源来连通各个模块单元。从本质上讲,布线资源的使用方法和设计的结果有直接的关系。

(5)底层嵌入功能单元

底层嵌入功能单元的概念比较笼统,这里我们指的是那些通用程度较高的嵌入式功能模块,比如 PLL (Phase Locked Loop)、DLL(Delay Locked Loop)、DSP、CPU 等。随着 FPGA 的发展,这些模块被越来 越多地嵌入到 FPGA 的内部,以满足不同场合的需求。 目前大多数 FPGA 厂商都在 FPGA 内部集成了 DLL 或者 PLL 硬件电路,用以完成时钟的高精度、低抖动的倍频、分频、占空比调整、相移等功能。目前,高端 FPGA 产品集成的 DLL 和 PLL 资源越来越丰富, 功能越来越复杂,精度越来越高。 另外,越来越多的高端 FPGA 产品将包含 DSP 或 CPU 等硬核,从而 FPGA 将由传统的硬件设计手段逐步过渡到系统级设计平台。例如 Altera 的 Stratix IV、Stratix V 等器件内部集成了 DSP 核;Xilinx 的 Virtes II 和 Virtex II pro 系列 FPGA 内部集成了 Power PC450 的处理器。FPGA 内部嵌入 DSP 或 CPU 等处理器, 使 FPGA 在一定程度上具备了实现软硬件联合系统的能力,FPGA 正逐步成为 SOPC 的高效设计平台。

(6)内嵌专用硬核

这里的内嵌专用硬核与前面的底层嵌入单元是有区分的,这里讲的内嵌专用硬核主要指那些通用性相对较弱,不是所有 FPGA 器件都包含硬核。 在 ZYNQ UltraScale 的 PL 端和 PS 端各有一个系统监视模块——System Monitors,它就是一个硬核。 System Monitors 包含一个模数转换器(ADC),一个模拟多路复用器,片上温度和片上电压传感器等。我们可以利用这个模块监测芯片温度和供电电压,也可以用来测量外部的模拟电压信号。

4.MPSoC PS 简介

MPSoC 实际上是 一个以处理器为核心的系统,PL 只是它的一个外设。MPSoC 系列的亮点在于它包含了完整的 ARM 处理器系统,且处理器系统中集成了内存控制器和大量的外设,使 Cortex-A53 处理器可以完全独立于可编程逻辑单元。而且实际上在 MPSoC 中,PL 和 PS 两部分的供电电路是独立的,这样 PS 或 PL 部分不被使用的话就可以被断电。

在前面我们介绍 SOPC 时提到过,FPGA 可以用来搭建嵌入式处理器,像 Xilinx 的 MicroBlaze 处理器 或者 Altera 的 Nios II 处理器。像这种使用 FPGA 的可编程逻辑资源搭建的处理器我们称之为“软核”处理器,它的优势在于处理器的数量以及实现方式的灵活性。

而 MPSoC 中集成的是一颗“硬核”处理器,它是硅芯片上专用且经过优化的硬件电路,硬核处理器的优势是它可以获得相对较高的性能。另外,MPSoC 中的硬件处理器和软核处理器并不冲突,我们完全可以使用 PL 的逻辑资源搭建一个 Microblaze 软核处理器,来和 ARM 硬核处理器协同工作。

从上面的结构图中可以很清楚的看到 MPSoC 的结构,它分为 PS 和 PL 两部分。在 PS 部分中它主要由 Arm Cortex-A53(APU 共 4 个核)、Arm Cortex-R5F(RPU 共两个核)以及 Arm Mali-400 MP2(GPU)三 种内核处理器构成,并且还包括 DDR 控制单元、平台管理单元、高速外设控制器以及普通外设控制器等外设组成。

(1)APU(Application Processing Unit)

APU 主要是由两个或者四个 ARM 处理器核组成的,Cortex-A53 核心是基于 Arm-v8A 架构的 32 位/64 位应用程序处理器,拥有极佳的性能/功率比,每一个 Cortex-A53 核心拥有 32KB 指令和数据 L1 缓存,具 有奇偶校验、ECC 保护、NEON SIMD 引擎、单精度和双精度浮点单元。除了这些模块,APU 还有一个 snoop 控制单元以及一个带 ECC 保护的 1MB L2 缓存,这样的设计可以更好的提高系统级的性能。该 APU 还具有 内置的中断控制器支持虚拟中断。

它的结构框图如下所示:

(2)RPU(Real-Time Processing Unit)

PS 中的 RPU 包含一个双核 Arm Cortex-R5F 处理器,Cortex-R5F 是 32 位实时处理器,它是基于 Arm-v7R 架构的处理器内核。每个 Cortex-R5F 核都有 32KB 的指令和数据缓存(L1),除了 L1 缓存,每个 Cortex-R5F 核心还具有 128KB 的紧耦合内存(TCM)接口,用于实时单周期访问。RPU 还有一个专用的中断控制器。 两个 RPU 既可工作在独立模式,也可以工作在同步模式。在独立模式中两个处理器都是独立运行的;在同步模式下,它们彼此并行运行,逻辑资源也会综合到一起,并且 TCM 资源也整合成 256KB。RPU 还可以通过 AXI-4 端口与 PS 端的 LPD 区域进行通信或者与 PL 端进行低延迟通信。支持实时 DEBUG 和信号跟踪, 每个内核还具有一个嵌入式跟踪宏单元(ETM)方便 Arm 内核调试。

Cortex-R5 处理器是用于深度嵌入式实时系统的 CPU,它采用了 Thumb-2 技术以获得最佳的代码密度和处理吞吐量,它还具有一个算术逻辑单元(ALU),为了更加有效地利用其他资源(例如寄存器资源),算术逻辑单元会执行有限的双重指令。Cortex-R5 处理器会通过重新启动和加载多个指令来保持较低的中断延迟,并且还会使用一个专用的外围端口来实现对中断控制器的低延迟访问。处理器具有紧密耦合内存(TCM) 端口,用于低延迟和确定性地访问本地 RAM。错误检查和纠正功能(ECC)是用于 Cortex-R5 处理器端口和 Level 1 (L1) 存储器的,这样可以提高系统的可靠性和准确性。Cortex-R5 处理器的结构框图如下所示:

(3)GPU(Graphics Processing Unit)

GPU 是基于 Arm Mali - 400 MP2 硬件加速器的 2D 和 3D 图形子系统。它由一个几何图形处理器(GP)、 两个像素处理器(PP)、64KB L2 缓存控制器(L2)、针对 GP 和每个 PP 的独立内存管理单元(MMU)以及 128 位 AXI 总线接口构成。Arm Mali-400 MP2 作为 PS 专用的图形处理器它可以支持 2D 和 3D 图形加速, 最高分辨率为 1080p,对于 3D 图形它能够支持 OpenGL ES 1.1 and 2.0 规范而对于 2D 的矢量图形它只能支 持 Open VG 1.1 标准。它的几何处理器(GP)和 2 个像素处理器会并行地执行贴图渲染操作。它为 GP 和像素处理器提供了专用的内存管理单元,支持 4 KB 的页面大小。

GPU 还有 64KB 的二级(L2)只读缓存,它支持 4X 和 16X 全场景抗锯齿(FSAA)功能。它有内置的硬件纹理解压缩,允许纹理在图形硬件中保持压缩(ETC 格式),并在运行中解压所需的样本。它还支持在不消耗额外带宽的情况下有效地混合多个硬件层,它的像素填充率为 200 万像素/秒/MHz,三角形填充率为 0.1Mvertex/秒/MHz。GPU 支持广泛的纹理格式为 RGBA 8888、565、1556 以及 YUV 格式,对于功率敏感 的应用,GPU 支持对每个 GP、像素处理器和 L2 缓存的时钟和功率进行门控。在功率门控过程中,GPU 不 消耗任何静态或动态功率;在时钟门控过程中,它只消耗静态电源。

(4)DDR Memory Controller

DDR 存储控制器通过六个 AXI 数据接口和一个 AXI 控制接口连接到 MPSoC 的其余部分,其中一条数据路径连接到实时处理单元(RPU),两条数据路径连接到缓存相干互连(CCI-400),其他的在 DisplayPort 控 制器、FPD、DMA 和编程逻辑(PL) 上多路复用。在 6 个接口中,5 个是 128 位宽,而第 6 个接口(绑定到 RPU)是 64 位宽。DDR 子系统支持 DDR3、DDR3L、LPDDR3、DDR4 和 LPDDR4,它可以通过 AXI 总线 接口接收来自 6 个应用主机端口的读写请求,这些请求在内部排队访问 DRAM 设备。存储器控制器在 DDRPHY 接口上向 PHY 模块发出命令,PHY 模块从 DRAM 中读取和写入数据。DDR Memory Controller 的结 构如下图所示:

(5)PMU(Platform Management Unit)

Zynq UltraScale+ MPSoC包括一个专用的用户可编程处理器,用于电源、错误管理的平台测量单元(PMU) 处理器,以及用于功能安全应用的可选软件测试库(STL)。由于 PMU 的结构和配置相当复杂这里我们只简 要列出他的功能,更加详细的介绍大家可以参考 Xilinx 官方文档 ug1085。 PMU 的功能如下:1、 使用系统监视器检查电源水平,以确保 CSU 和 LP 域的其余部分正常运行。 2、 初始化 pll 的默认配置和他们潜在的旁路。 3、 触发和排序必要的扫描和 MBIST。 4、 捕获并发出错误信号,错误 ID 可以通过 JTAG 读取。 5、 释放复位到 CSU。 6、 在应用程序和实时处理器处于睡眠状态时充当它们的委托,并在接收到它们的唤醒请求之后对他 们进行开机和重启。 7、 在任何时候维护系统电源状态。 8、 处理不同块的上电、下电、复位、内存内置自修复(MBISR)、MBIST 和扫描归零所需的低级事件序列。 9、 在休眠模式下管理系统,并基于各种触发机制唤醒系统。 10、 PS-level 错误捕获。

(6)High-Speed Connect Zynq

UltraScale+ MPSoC 的 PS 端集成了 5 个高速外设,分别是 DP 控制器、USB3.0 控制器、SATA3.1 控制器、PCIE 1.0/2.0 控制器以及 PS-GTR 收发器。

1、DP接口(DisplayPort 控制器):Zynq UltraScale+ MPSoC 的 PS 端集成了 DisplayPort 控制器,它可以从内存(非实时输入)或(实时输入)可编程逻辑(PL)中获取数据,并将这些数据处理过后通过 DisplayPort 源控制器块输出到外部显示设备或 PL(实时输出)上。DisplayPort 控制器由 DMA、缓冲区管理器、显示渲染块、音频混音块、DisplayPort 源控制器以及 PS-GTR 模块组成,它可以支持 超高清(UHD)视频,因此 DP 接口常用来做视频图像传输的接口。

2、 USB3.0:USB 3.0 控制器由两个独立的 DRD (dual-role device)控制器组成,两者都可以单独配置为 在任何给定时间作为主机或从机设备工作。USB 3.0 DRD 控制器通过高级的可扩展 AXI 从接口, 可以为系统软件提供一个可扩展的主控制器接口(xHCI)。控制器中有一个内部的 DMA 引擎,它利 用 AXI 主接口来传输数据。三个双端口 RAM 的配置可以实现 RX 数据 FIFO、TX 数据 FIFO 和描 述符/寄存器缓存功能,AXI 主端口与协议层可以通过缓冲区管理单元访问不同的 RAM。

3、 SATA3.1:SATA 控制器是一种高性能双端口主机控制器,具有 AHCI 兼容的命令层,该命令层对 使用端口乘法器的系统来说,具有支持基于本地命令队列和帧信息结构(FIS)交换的高级功能。 SATA 使用 ATA/ATAPI 命令集,但是通过不同的导线可以实现与 SATA 第 1 代、第 2 代或第 3 代 相对应的 1.5、3.0 或 6.0 Gb/sec 的速率进行串行通信。串行数据采用 8B/10B 编码,确保数据模式 中有足够的转换以确保直流平衡(这里的转换指数据的 0/1 转换,关于直流平衡的知识大家可以自行了解或者看我们 HDMI 相关的视频,其中有涉及),并使时钟数据恢复电路能够从输入数据模式中提取时钟。

4、 PCIe 1.0/2.0 控制器:MPSoC 集成了一个 PCIe 通信控制器,用于实现 PCIe 的通信,它包含 AXI-PCIe 桥和 DMA 组件,AXI-PCIe 桥主要是为 PCIe 和 AXI 提供高性能桥接。模块示意图如下所示:

从上图中可以看到控制器由两个子模块组成,其中 PCIe 桥的主要功能除了将 PCIe 协议与 AXI 协议相互转换外还可以转换入口/出口地址,为 DMA 和 Root Port/Endpoint (RP/EP)模式切换提供特定的服务。

5、 PS-GTR 收发器:千兆 GTR 收发器为串行输入输出单元(SIOU)的外围设备、媒体访问控制器(mac) 以及它们的高速通信链路提供专用的 I/O。Zynq UltraScale+ MPSoC 共有四个可编程高速收发器, 可以支持数据速率高达 6gb /s 的子层协议。

(7)普通外设控制器

Zynq UltraScale+ MPSoC 的 PS 端除了集成的高速通信外设之外,还有一些普通的低速外设,其中包括 GigE、USB2.0、CAN、UART、SPI、Quad SPI NOR、NAND 以及 SD/eMMC 等外设控制器。

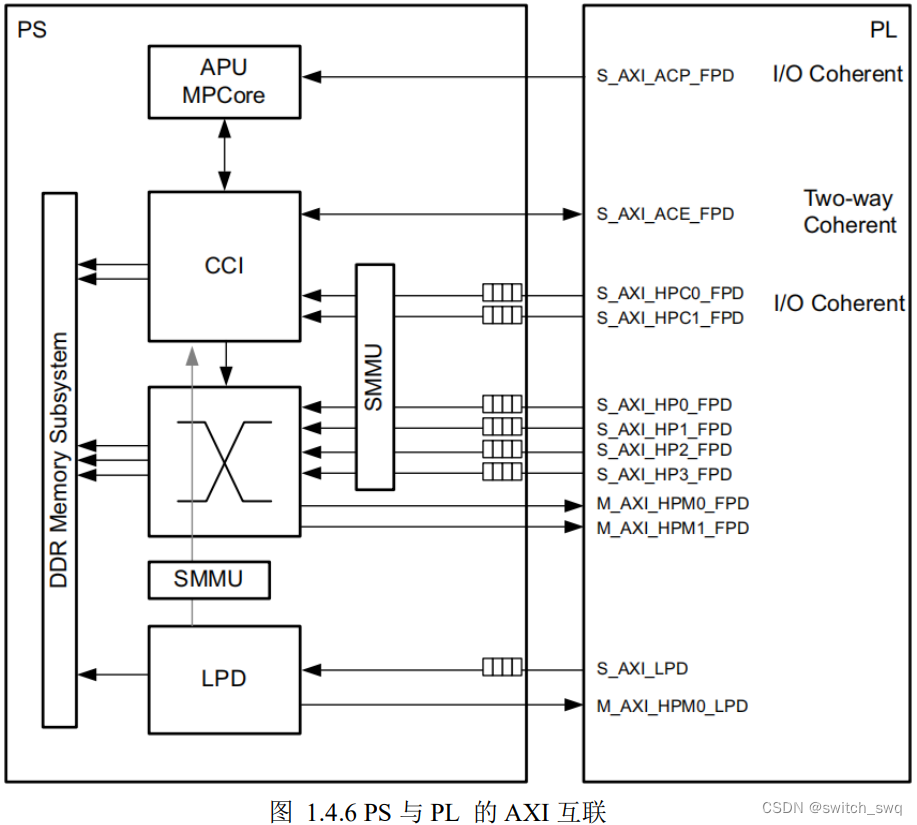

(8)PS-PL AXI 接口

MPSoC 将高性能 ARM Cotex-A 系列处理器与高性能 FPGA 在单芯片内紧密结合,为设计带来了如减小体积和功耗、降低设计风险,增加设计灵活性等诸多优点。在将不同工艺特征的处理器与 FPGA 融合在 一个芯片上之后,片内处理器与 FPGA 之间的互联通路就成了 MPSoC 芯片设计的重中之重。如果 Cotex-A53 与 FPGA 之间的数据交互成为瓶颈,那么处理器与 FPGA 结合的性能优势就不能发挥出来。 Xilinx 从 Spartan-6 和 Virtex-6 系列开始使用 AXI 协议来连接 IP 核。在 7 系列、Zynq-7000 和 Zynq UltraScale+ MPSoC 器件中,Xilinx 在 IP 核中继续使用 AXI 协议。AXI 的英文全称是 Advanced eXtensible Interface,即高级可扩展接口,它是 ARM 公司所提出的 AMBA(Advanced Microcontroller Bus Architecture)协议的一部分。

AXI 协议是一种高性能、高带宽、低延迟的片内总线,具有如下特点:

1、总线的地址/控制和数据通道是分离的;

2、支持不对齐的数据传输;

3、支持突发传输,突发传输过程中只需要首地址;

4、具有分离的读/写数据通道;

5、支持显著传输访问和乱序访问;

6、更加容易进行时序收敛。

在数字电路中只能传输二进制数 0 和 1,因此可能需要一组信号才能高效地传输信息,这一组信号就组成了接口。AXI4 协议支持以下三种类型的接口:

1、 AXI4:高性能存储映射接口。

2、 AXI4-Lite:简化版的 AXI4 接口,用于较少数据量的存储映射通信。

3、 AXI4-Stream:用于高速数据流传输,非存储映射接口。

AXI4 协议支持突发传输,主要用于处理器访问存储器等需要指定地址的高速数据传输场景。AXI-Lite 为外设提供单个数据传输,主要用于访问一些低速外设中的寄存器。而 AXI-Stream 接口则像 FIFO 一样, 数据传输时不需要地址,在主从设备之间直接连续读写数据,主要用于如视频、高速 AD、PCIe、DMA 接 口等需要高速数据传输的场合。

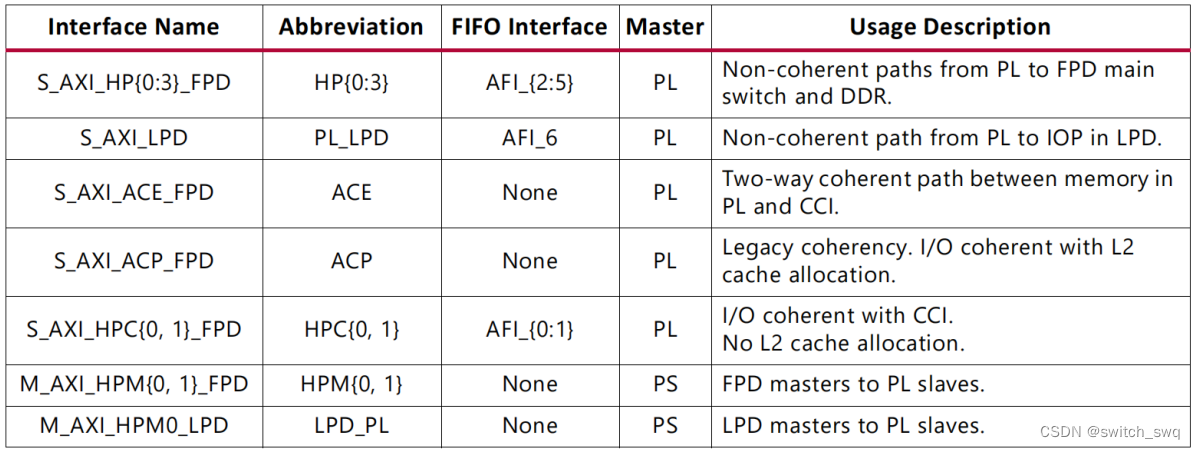

在 PS 和 PL 之间的主要连接是通过一组 12 个 AXI 接口,每个接口有多个通道组成。这些形成了 PS 内部的互联以及与 PL 的连接,如下图所示:

上图给出了每个接口的简述,标出了主机是 PL 还是 PS(按照惯例,主机是控制总线并发起会话的, 而从机是做响应的)。需要注意的是,接口命名的第一个字母表示的是 PS 的角色,也就是说,第一个字 母 “M” 表示 PS 是主机,而第一个字母“S”表示 PS 是从机。

S_AXI_HP{0:3}_FPD/S_AXI_HPC{0,1}_FPD:六个 PL 侧高性能(High Performance)AXI 主接口连接到 PS 侧的 FPD(Full-power domain),主要用于访问 DDR 内存,进行大量数据的传输,如摄像头图像数据等。所有的六个高性能 AXI 主接口都经过了 PS 中的 SMMU(System Memory Management Unit), SMMU 能够使用物理和虚拟地址转换。其中一致性 S_AXI_HPC 接口连接到了 CCI(Cache-coherent interconnect),可以访问 L1 和 L2 Cache,也正是连接到了 CCI,所以在访问 DDR 控制器时,相比于 S_AXI_HP 接口来说,延时会较大。

S_AXI_LPD:主机 PL 连接至从机 PS 侧 LPD(Low-power domain)的高性能 AXI 接口,它能够低延 时地访问 OCM(On-chip Memory)和 TCM(Tightly-coupled Memory)。 S_AXI_ACE_FPD:主机 PL 与从机 PS 中的 CCI 相连接,它能够支持 PS 和 PL 中的硬件块之间的完全一致性(双向)。该接口使用的是 ACE(AXI coherency extension)协议,与 AXI 接口相比,ACE 协议 使用了五个额外的通道,三个通道用于监听,两个用于应答。 S_AXI_ACP_FPD:该接口实现了 PL 和 PS 之间的低延时访问,PL 端可以直接访问 APU 的 L1 和 L2 Cache 以及 DDR 内存。

M_AXI_HPM{0,1}_FPD:该高性能接口由主机 PS 侧 FPD 连接至从机 PL,可以用于 CPU、 DMA、 PCIe 等传输大量数据到 PL。

M_AXI_HPM0_LPD:该高性能接口由主机 PS 侧 LPD 连接至从机 PL,该接口适合于为 PS 中的 LPD 主机(例如 LP-DMA)提供对 PL 中的存储器的访问,也经常用于配置 PL 端的寄存器。

上面每条总线都是由一组信号组成的,这些总线上的会话是根据 AXI4 总线协议进行通信的。

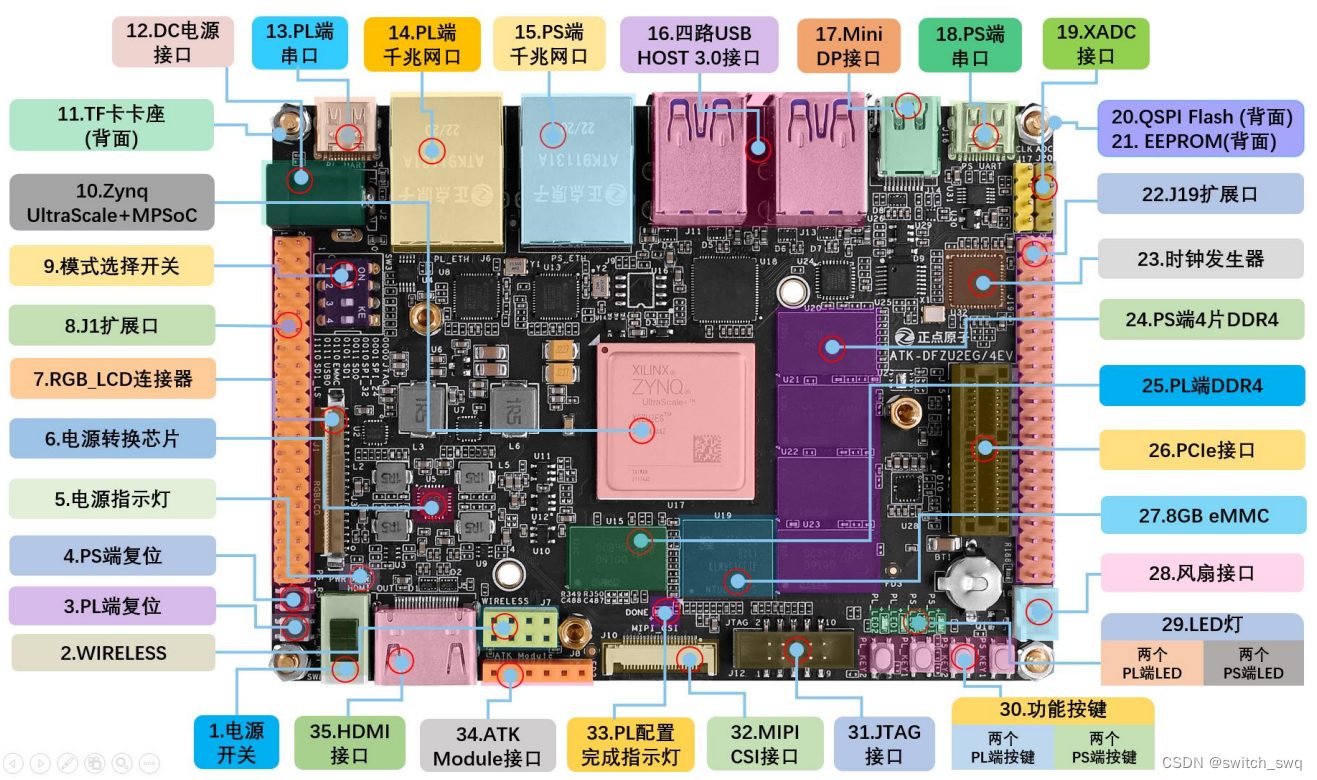

5.DFZU2EG MPSoc 硬件连接资源

具体说明见参考书目 P38~P42 ;注意点说明:1.纽扣电池座:DFZU2EG/4EV MPSoC 开发板板载一个纽扣电池座,在开发板断电时,电池可以持续为 MPSoC 芯片内 部的 RTC 实时时钟模块进行供电,以维持计时的功能。2. 1.8 V IO 电平扩展口和 3.3 V IO 电平扩展口。

详细说明:

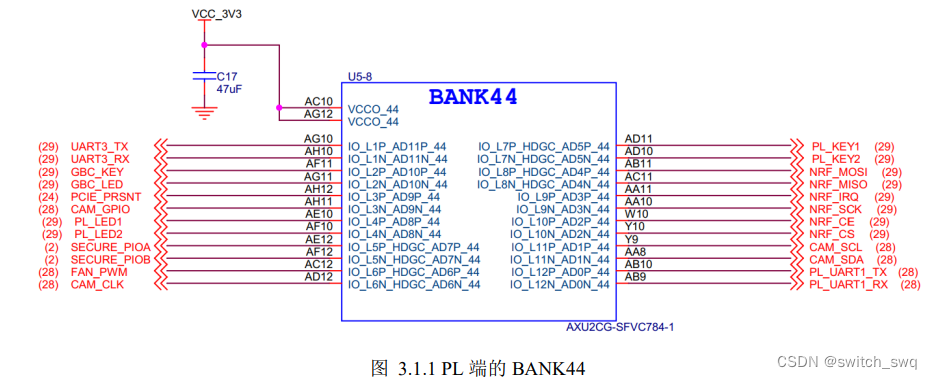

(1)IO 分配

Zynq UltraScale+ MPSoC 系列的 xczu2cg-sfvc784-2、 xczu2eg-sfvc784-2 和 xczu4ev-sfvc784-1,总共有 14 个用户 BANK(指连接外设的 BANK,不包 BANK224)。这 14 个 BANK 中有 6 个属于 PS 端,8 个属于 PL 端,不同的 BANK 上连接有不同的外设。

PL 端的 IO 被分成 8 组也就是 8 个 BANK,同一个 BANK 中 IO 供电是相同的,不同的 BANK 之间供电电压可以不相同。在 DFZU2EG/4EV MPSoC 开发板中 PL 端 BANK24、BANK44、BANK25 以及 BANK26 都是 3.3V 电压供电,而 BANK64、BANK65 是 1.2V 供电,BANK0、BANK66 是 1.8V 供电。之所以不同 BANK 之间的供电不同主要和它们连接的外设,即承担的功能有关,遵循的原则就是速度越快电压越低,例如 BANK64 连接的是 DDR4 芯片,需要处理高速的数据吞吐,因此它的供电电压较低,为 1.2V。举例 BANK 的原理图如下所示:

从原理图中可以看出 DFZU2EG/4EV MPSoC 开发板的 PL 端引脚是非常多的,为了方便大家查找我们将例程用到的整理成了一张表格,可在参考书目P55~P59查看。

PS 端一共包含了 6 个 IO BANK,与 PL 端 IO BANK 不同的是,PS 端的 IO 连接是是相对固定的,用户不能够像 PL 引脚那样,将 PS 端的 IO 随意分配到某个外设。PS 端外设的 IO 口与 MIO(多路复用 IO)之间,具有固定关系的映射,某 个外设的 IO 口可能会映射到不同的 MIO 上,某个 MIO 也有可能会具有多个外设的 IO 口映射到其上面。 可在参考书目P63~P65查看。

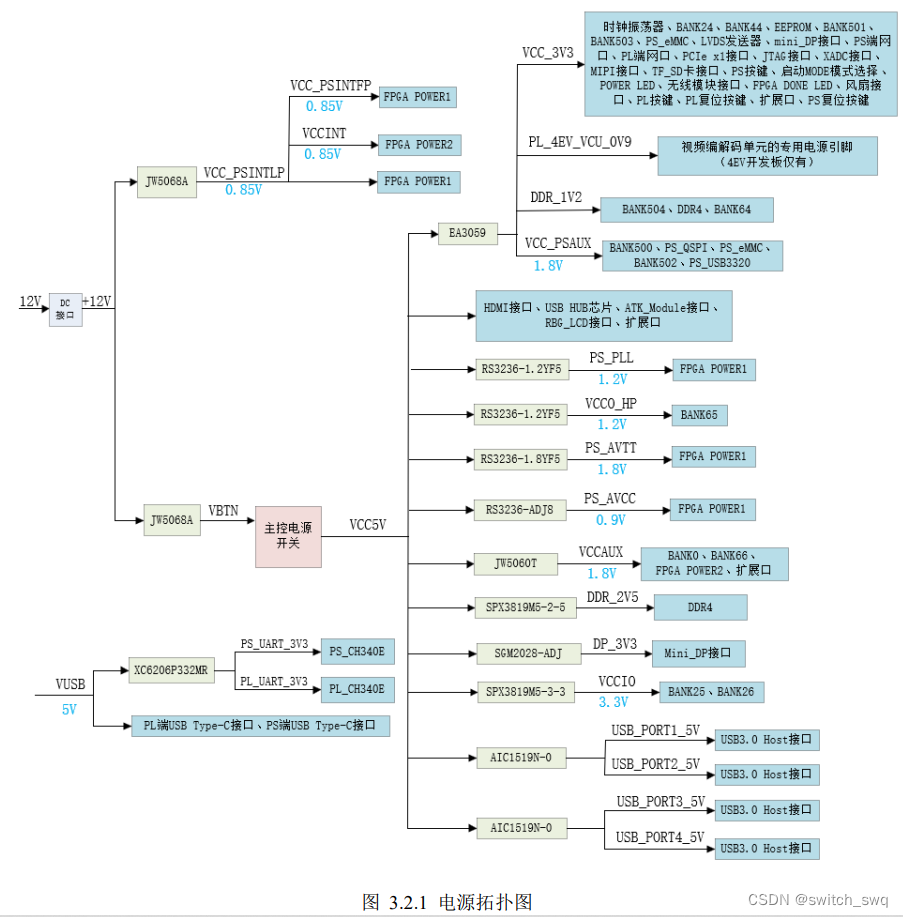

(2)电源系统

下图是电源的拓扑结构,标出了降压模块和降压后的电压:

这里要特别提醒一下大家,板子上有的已经有一种电压了例如 1.8V,为什么后 面还要再转个 1.8V 出来,而且同一种电压还会有好几个名称,这主要是因为有很多器件是有上电顺序的, 不可以同时上电,虽然工作电压都相等,但是上电顺序有先后要求,所以我们就通过一定的电路设计让整 个板子上的器件有一个先后的上电顺序,这就是为什么同一种电压转换了多次或者好几个名字,主要是每 个名字代表的电压产生的顺序不同。

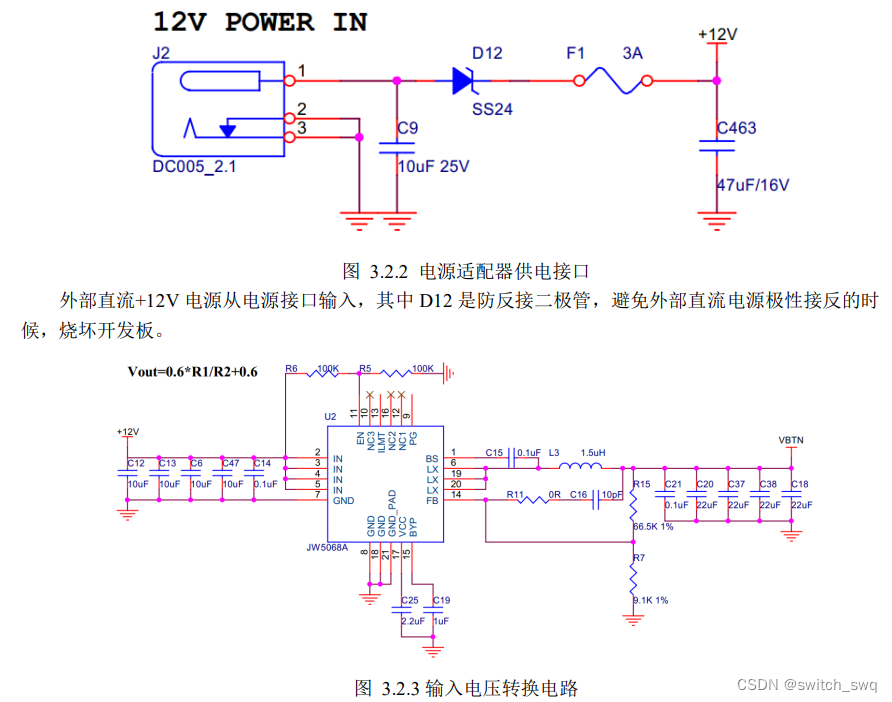

电源适配器供电的电源接口原理图如下图所示:

上图电路的作用是将外部输入的+12V 电压经过降压芯片转换为 5V 电源 VBTN 输出。参考书目上有各个模块供电的说明P67~P76。

启动顺序: VCC_PSAUX>DDR_1V2>VCC_3V3>PL_VCU_0V9(1.8V>1.2V>3.3V>0.9V)

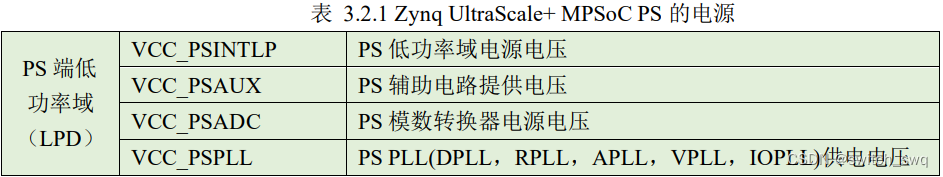

PS 端在全功率域(FPD)可以工作之前,低功率域(LPD)必须工作。

为了实现最小电流消耗并确保 I/O 在通电时处于三态,列出了低功率域(LPD)的建议通电顺序。同时 建议关机顺序与开机顺序相反。

1.VCC_PSINTLP

2.VCC_PSAUX、VCC_PSADC 和 VCC_PSPLL 以任何顺序或同时进行。

3.VCCO_PSIO

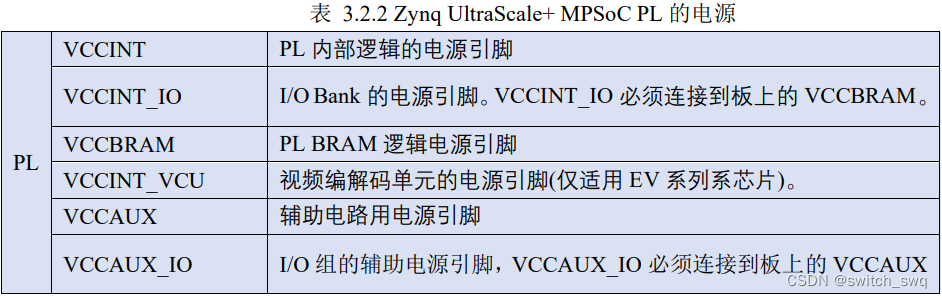

为了实现最小电流消耗并确保 I/O 在通电时处于三态,列出了全功率域(FPD)的建议通电顺序。同时 建议关机顺序与开机顺序相反。 、

1.由同一电源驱动的 VCC_PSINTFP 和 VCC_PSINTFP_DDR。

2.VPS_MGTRAVCC 和 VCC_PSDDR_PLL 以任何顺序或同时进行。

3.VPS_MGTRAVTT 和 VCCO_PSDDR 以任何顺序或同时进行。

官方推荐的 PS 端低功率域(LPD)上电顺序为:VCC_PSINTLP→VCC_PSAUX、VCC_PSADC 和 VCC_PSPLL→VCCO_PSIO。

官方推荐的 PS 端 全 功 率 域 ( FPD ) 上 电 顺 序 为 : VCC_PSINTFP 和 VCC_PISNTFP_DDR→ VPS_MGTRAVCC 和 VCC_PSDDR_PLL→VPS_MGTRAVTT 和 VCCO_PSDDR。

![]()

(3)启动模式

DFZU2EG/4EV MPSoC 开发板支持 8 种启动模式,我们常用的启动模式是 JTAG 启动、FLASH 启动以 及 SD 卡启动,此外还支持 eMMC 启动以及 USB 启动。具体的启动方式选择可以通过拨动拨码开关去控制,拨码开关拨动的值和对应的启动模式,在原理图中以表格的形式给大家列举出来了。其原理图如下所示:

(4)其他硬件资源

此外,参考书目P76~P101列出了 PL 端千兆以太网、PS 端千兆以太网、USB3.0 接口、USB HUB 芯片、MINI DP 接口、PS 端串口、PL 端串口、XADC 接口、时钟振荡器、J19 扩展口、J1 扩展口、EEPROM、PCIe 接口、PS 端 4 片 DDR4、PL 端 1 片 DDR4、eMMC、风扇接口、PL和 PS 端按键、PL 和 PS 端 LED、MIPI CSI 接口、PL 配置完成指示灯、电源指示灯、HDMI 接口WIRELESS 接口、ATK-MODULE、PL 和 PS 端复位、TF 卡接口、QSPI FLASH、RGB888 TFT-LCD 等的电路连接、引脚说明、时序结构等说明。

6.其他

(1)注意事项

为了让大家更好的使用 DFZU2EG/4EV MPSoC 开发板,我们在这里总结该开发板使用的时候尤其要 注意的一些问题,希望大家在使用的时候多多注意,以减少不必要的问题。

1. 当你想使用某个 IO 口用作其他用处的时候,请先看看开发板的原理图,该 IO 口是否有连接在开发板的某个外设上,如果有,该外设的这个信号是否会对你的使用造成干扰, 先确定无干扰,再使用这个 IO。

2. 开发板上的拨码开关需要拨到对应的模式才能启动开发板,如果模式和启动方式不对应会造成代码下载失败或者板子启动不起来。

3. 当液晶显示白屏的时候,请先检查液晶模块是否插好(拔下来重新插试试),如果 还不行,可以通过串口看看 LCD ID 是否正常,再做进一步的分析。

(2)学习 MPSoC 基本方法:

<1>了解 MPSoC 的基本结构

学习 MPSoC 之前需要先对 MPSoC 基本结构和其功能有个大概的了解,如 PS、AXI 总线、锁相环 PLL、FIFO 等。需要知道 PLL 是用来产生不同频率的时钟,如使用 HDMI 时需要生成 75MHz 的时钟; FIFO 用于数据的缓存和异步时钟域数据的传递等。

<2>了解 Verilog HDL 基本语法

Verilog HDL 做为一种硬件描述语言,是 对数字电路的一种描述,而数字电路是并行工作的,因而在编写 Verilog HDL 时要有并行的思想,不同于 软件设计语言,软件设计语言是由 CPU 统一进行处理,一条指令一条指令的串行运行,所以软件设计语 言是基于串行的设计思想,因而在写 Verilog HDL 代码的时候要注意这种差别。另外对于 Verilog HDL 的 基本语法是务必要掌握的,如一般常用的 module/endmodule、input/output/inout、wire/reg、begin/end、 posedge/negedge、always/assign、if/else、case/default/endcase/parameter/localparam 等关键字要清楚它们的作用和区别。掌握了 Verilog HDL 的基本语法和 Verilog HDL 的并行设计思想后,会觉得 Verilog HDL 和 C 语言一样简单。

<3>MPSoC PS 的学习

学习 MPSoC PS 首先要了解 C 语言的基本语法。然后了解 PS 端基本的系统框架和外设,例如 PS 端架构、片内互连、AXI 总线、DDR 控制器等等。最关键的是 PS 端的 C 程序。软件系统可以被认为是建立于基于硬件的系统上的一个栈,或者说是一系列层,从底至上依次是基础硬件系统(来自 Vivado 的自定义硬件)、板级支持包、Operating System、软件应用。

初学者可以多看看官方的文档和资料,对于 PS 端的软件,xilinx 提供了丰富的库函数,很多时候用户直接调用调用即可,读者要学会利用这些库函数。遇到问题时,读者可以借助 xilinx 的 SDK 开发环境中的各种调试功能来定位错误,以帮助解决问题。