- 1魔百和CM211-1&CM201-1 S905L3B通刷精简音线刷包及教程_魔百盒cm201-1刷机包

- 2python界面开发哪个库最好,python界面怎么设置中文_python 哪种方式做操作界面好

- 3【 React 】state和props有什么区别?

- 4超级简单的Android源码下载_安卓源码下载

- 5xshell中出现的绿色背景的文件夹

- 6High-Resolution Image Synthesis with Latent Diffusion Models 论文重点

- 7vscode编辑器自动生成.vue文件三组标签结构的方法_vscode生成vue页面结构

- 8Jquery插件大全

- 9unity urp 实现衣服绒毛效果_unity动物毛发

- 10DifFace——一种扩散模型来提高人脸图片分辨率与清晰度_基于扩散模型从低质量图像到高质量图像

数字电路基础知识——组合逻辑电路(数据选择器MUX、多路复用器)_mux是什么逻辑运算

赞

踩

数字电路基础知识——组合逻辑电路(数据选择器MUX、也即多路复用器)

本次介绍数据选择器的相关知识,数据选择器在电路设计中尤为重要,尤其是对于在Verilog中的if-else的语法即 o = a?b :c 都可以看到有数据选择器的使用。

介绍数据选择器的设计原则以及实例:用Verilog描述一个多路复用器,输入的通道数目N,每一路的位宽为M。

求log以2为低的整数的算法(使用移位寄存器、数据比较器)

一、二选一数据选择器(2-1 MUX)

二选一的数据选择器是最简单的结构,其逻辑框图、门级电路、以及真值表如下:

二、 用 2输入mux,实现与,或,非,异或

二选一用Verilog语言描述:

o = s ? a : b;

-

与逻辑:

out = (a == 1’b0)? 1’b0: ((b == 1’b0)? 1’b0: 1’b1);

或

out = (a == 1’b1)? b: 1’b0;

Y=SA+S’B=AB+A’0=AB -

或逻辑:

out = (a == 1’b1)? 1’b1: ((b == 1’b1)? 1’b1: 1’b0);

或

out = (a == 1’b0)? b: 1’b1;

Y=SA+S’B=A’B+A=A+B -

非逻辑:

out = (a == 1’b1)? 1’b0: 1’b1; -

异或

out = (a == 1’b1)? ((b == 1’b1)? 1’b0: 1’b1) : (b);

Y=AB’+A’B

三、 四选一选择器

在实际的芯片器件中,用的最多的是双四选一选择器 74HC153

下图是内部逻辑电路图:

四选一只需两位地址输入,四个输入状态选择其中一个

而八选一需要三位地址输入,八个输入状态选择其中一个,利用S’作为第三个地址输入端

因此可以利用这两个四选一选择器接成一个八选一的选择器

四、用选择器设计组合逻辑电路

基本原理:

利用如下关系

一个具有n位地址输入的数据选择器,可以产生任何形式的

输入不大于n+1的组合函数

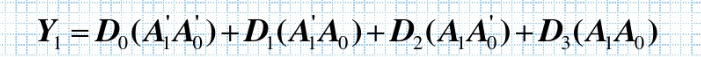

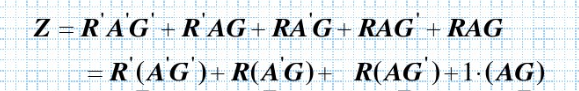

对于下面的逻辑表达式:

即Z=R’(A’G’)+R(A’G)+R((AG’)+1(AG))

当然也可以用R A 作为选通地址,G作为选通端,将函数化简如下:

Z=(R’A’)G’+(RA’)G+(RA)1

五、例:用Verilog描述一个多路复用器,输入的通道数目N,每一路的位宽为M。

- 代码设计如下:

module mux

#(

parameter m = 8,

parameter n = 8,

parameter width = clogb2(n)

)

(

input [n*m-1:0] indata,

input [width-1:0] sel,

output [m-1:0] outdata

);

assign outdata = indata[(m*(sel+1)-1)-:m];

//-------------------------------------------------------

//以下两个函数任用一个

//求2的对数函数

function integer log2;

input integer value;

begin

value = value-1;

for (log2=0; value>0; log2=log2+1)

value = value>>1;

end

endfunction

//求2的对数函数

function integer clogb2 (input integer bit_depth);

begin

for(clogb2=0; bit_depth>0; clogb2=clogb2+1)

bit_depth = bit_depth>>1;

end

endfunction

endmodule

- 1

- 2

- 3

- 4

- 5

- 6

- 7

- 8

- 9

- 10

- 11

- 12

- 13

- 14

- 15

- 16

- 17

- 18

- 19

- 20

- 21

- 22

- 23

- 24

- 25

- 26

- 27

- 28

- 29

- 30

- 31

- 32

- 33

- 34

- 35

- 36

- 37

这里需要注意:

- [n-:m]表示数据位宽为m的从n开始的数据位宽。如reg [6-:3] 表示 reg [6:4]

- 参数传递必须时具体数值,如在parameter定义。

- 求log以2为低的整数,具体方法上面用到的是移位寄存器,即将数据向右移位即可以得到所需最大的整数。

也可以利用下面的方法:

function integer log2(input integer x);

integer i;

begin

log2 = 1;

for (i = 0; 2**i < x; i = i + 1) //不用移位寄存器,只用比较器

begin

log2 = i + 1;

end

end

endfunction

- 1

- 2

- 3

- 4

- 5

- 6

- 7

- 8

- 9

- 10

注: 2**i 表示2i

log2(10)等于4

log2(16)等于4

log2(510001000)等于26